本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试平台构建的过程。

首先对测试平台集成者(testbench integrator)和测试编写者(test writer )进行区分,前者负责测试平台的构建和配置,后者可能对测试平台的底层了解较少,但用它来创建测试用例。

基于验证组件创建测试平台的步骤是:

Review可重用的验证组件配置参数。

实例化和配置验证组件。

为接口验证组件创建可重用的sequences(可选)。

添加一个virtual sequencer(可选)。

增加checking和functional coverage。

创建测试用例以实现覆盖率目标。

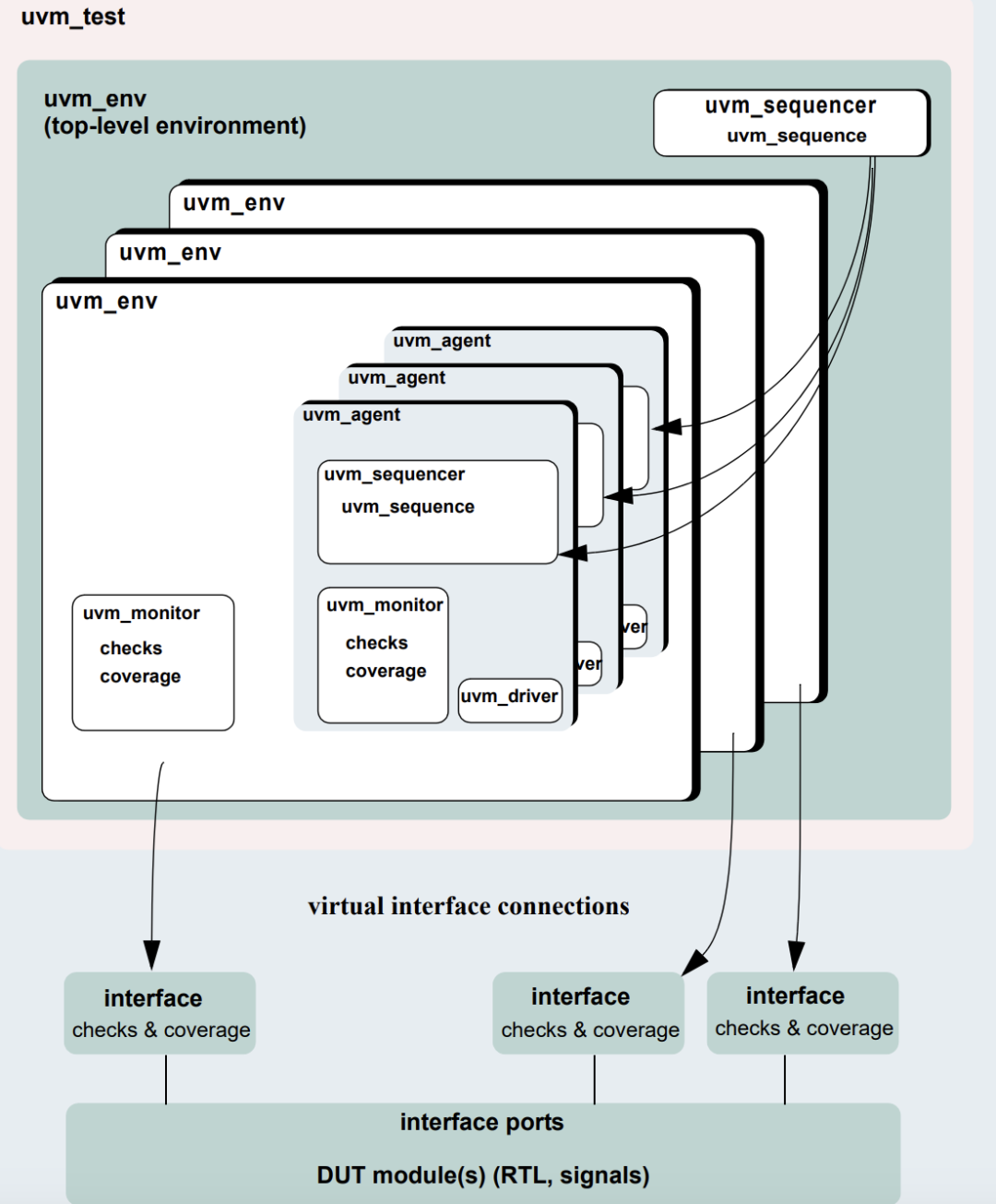

创建Top-Level Environment

Top-Level Environment是一个容器,它定义了可重用验证组件的拓扑结构,实例化并配置可重用的验证IP,并根据需要定义该IP的默认配置。不同的测试用例可以实例化并重新配置Top-LevelEnvironment类,以更好地实现其测试目的。

实例化验证组件

不同的测试用例可以实例化上面的top-level environment 类,并根据需要对其进行配置,而不需要了解它被创建和配置的所有细节。

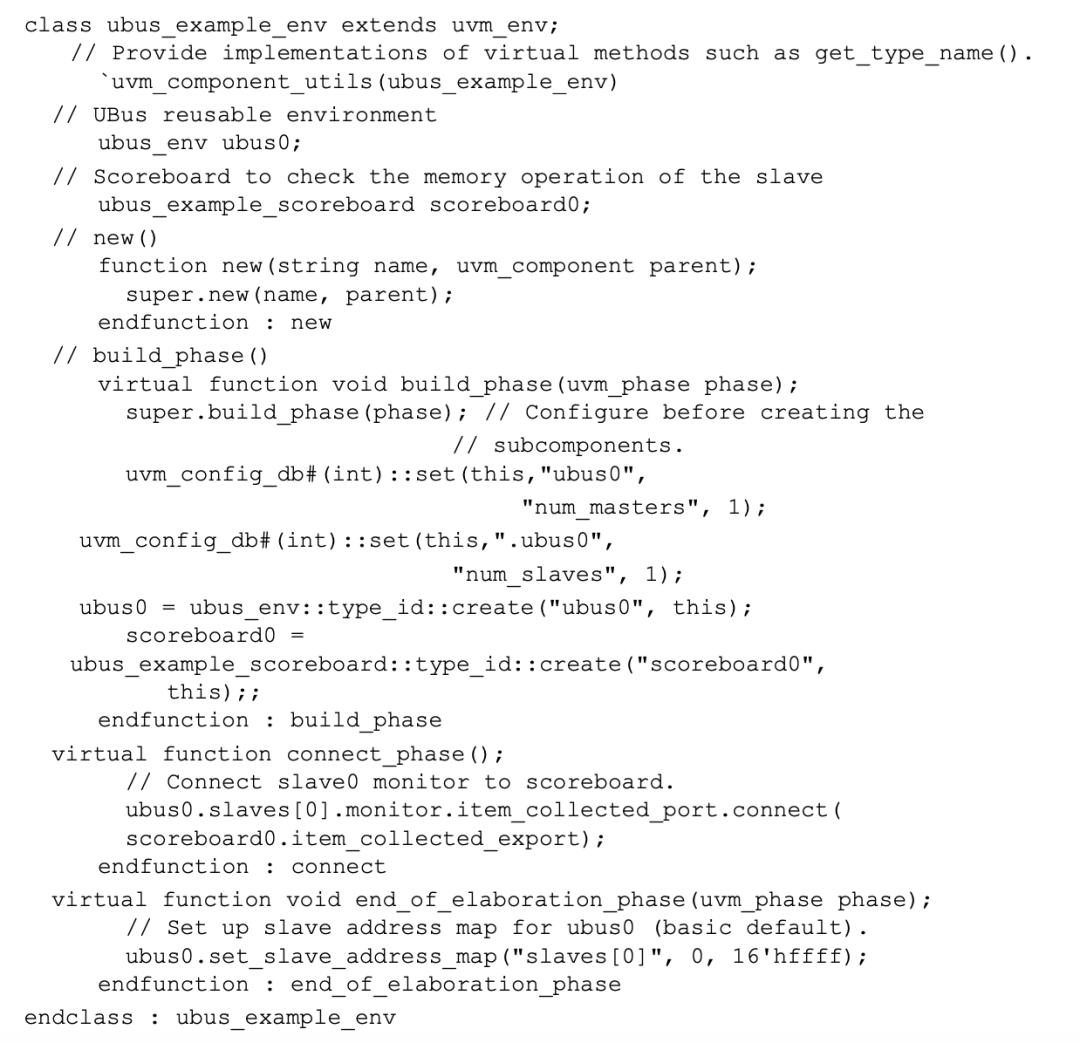

我们不是在ubus_example_env的new()构造函数,而是在内置的UVM phase中创建验证子组件。

uvm_config_db::set 调用指 定masters和slaves的数量都应该是1。这些配置 在 ubus0 build_phase()中被使用,定义ubus0环境的拓 扑结构。

super.build_phase()作为ubus_example_env’s build()的第一行调用,如果使用了UVM字段自动化宏(UVM field automation macros ),这将更新ubus_example_tb的配置字段。

connect_phase()是一个内置的UVM phase,用于在slave monitor 和scoreboard之间建立连接。slave monitor包含一个TLM analysis port,它与scoreboard上的TLM analysis export 相连。在build_phase()和connect_phase()函数完成后,用户可以对一些配置进一步进行调整。

创建testcase

uvm_test类定义了测试场景(test scenario),涉及到验证环境的配置。尽管验证环境开发者提供了验证环境拓扑和配置属性的默认值,测试用例开发者可以使用UVM类库提供的配置覆盖机制进行覆盖。UVM中的测试用例是由uvm_test类派生的类,通常定义一个基础test case类,实例化并配置Top-Level Environment,然后被扩展以定义特定场景。

审核编辑:刘清

-

UVM

+关注

关注

0文章

183浏览量

20100 -

TLM

+关注

关注

1文章

46浏览量

25425

发布评论请先 登录

可重用机床编码技术及重构算法研究

户外光伏组件户外测试平台设计

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

数字IC验证之“构成uvm测试平台的主要组件”(4)连载中...

求助,可重用组件的推荐目录结构是什么?

基于FPGA的NoC验证平台的构建

可测性DSP软硬件协同仿真验证平台设计

基于可重用激励发生机制的虚拟SoC验证平台

基于System Verilog的可重用验证平台设计及验证结果分析

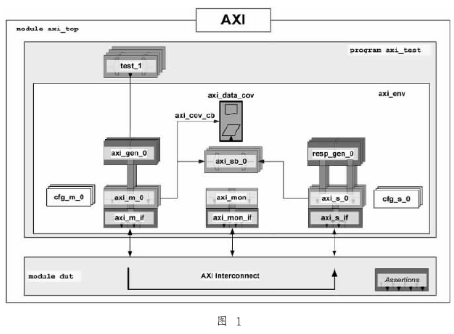

基于VMM构建的验证平台在AXI总线协议SoC中的应用研究

介绍从一组可重用的验证组件中构建测试平台所需的步骤

介绍从一组可重用的验证组件中构建测试平台所需的步骤

评论