验证环境用户需要创建许多测试用例来验证一个DUT的功能是否正确,验证环境开发者应该通过以下方式提高测试用例的开发效率:

在数据项类中加入旋钮,以简化测试用例开发控制

创建一些可重用的sequences library。

声明自定义的Sequences

Sequences是由几个数据项组成的,它们共同构成一个数据pattern以触发有趣的DUT场景。

验证组件可以包括一个基本sequences library(而不是单一的数据项),测试用例编写者(验证环境使用者)可以调用它。这种方法加强了对常见数据pattern的复用,并减少了测试用例的代码长度。此外,一个Sequences可以调用其他Sequences,从而创造更复杂的场景。

UVM类库提供了uvm_sequence基类。你应该直接或间接地从这个类派生出所有的Sequences类。要创建一个用户定义的Sequences:

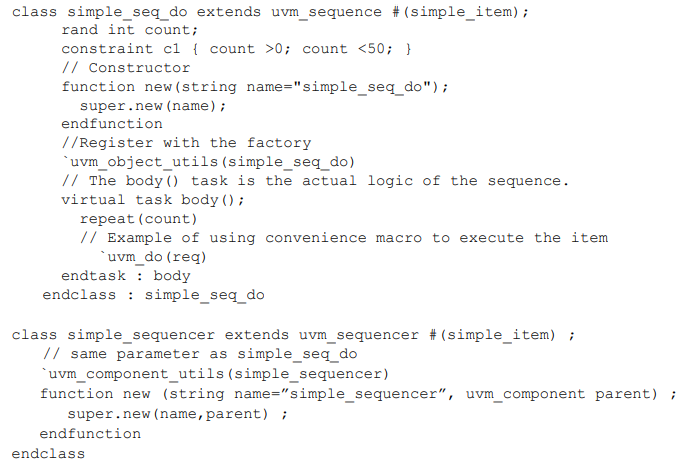

从uvm_sequence基类派生出一个Sequences,并指定request和response数据项类型参数。在下面的例子中,只指定了request类型,即simple_item,所以response数据项类型也是simple_item 。

使用`uvm_object_utils宏来向factory注册Sequences类型。

如果Sequences需要访问其相关sequencer,使用'uvm_declare_p_sequencer宏来声明sequencer指针。

实现Sequences的body任务来触发特定的DUT场景。在body任务中,你可以发送数据项或者调用其他Sequences。

下面例子中的simple_seq_do类定义了一个简单的Sequences。它是由uvm_sequence派生出来的,并 使 用 了 `uvm_object_utils 宏 。这个例子还定义了一个simple_sequencer类,simple_seq_do序列可以在该simple_sequencer上运行。

发送Sequence Items或者Subsequences的基本流程

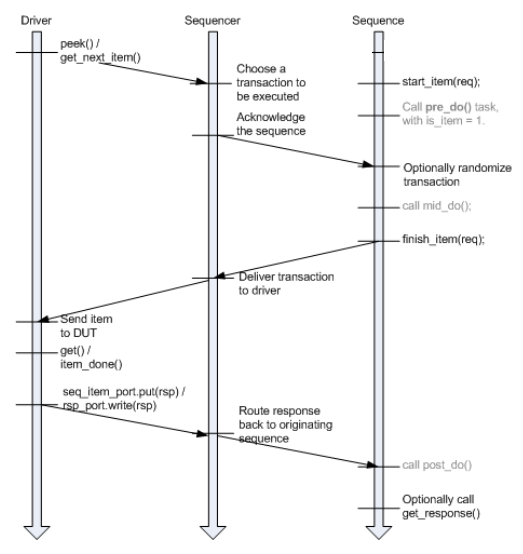

要 发 送 一 个sequence item,sequence的body()任务 需 要create() 该 sequence item , 对 该sequence item调 用start_item(),然后随机化该sequence item(可选的),最后对该sequence item调用finish_item()。

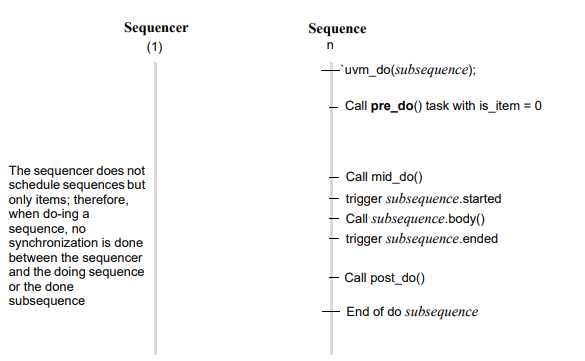

要发送一个subsequence,parent sequence的body()任务需要create该subsequence,对其进行随机化(可选的),最后对该subsequence调用start()。如果subsequence有一个相应的response,parent sequence可以调用get_response()。

上图显示了在uvm_do宏中实现的发送sequence items和sequences的完整流程。uvm_do宏会更根据传递的类型create一个对象,并且根据发送sequence items和sequences执行对应的流程。

uvm_do宏不会执行subsequences的pre_body()和post_body()方法。

审核编辑:刘清

-

UVM

+关注

关注

0文章

183浏览量

20108 -

DUT

+关注

关注

0文章

194浏览量

13501 -

sequence

+关注

关注

0文章

23浏览量

3309

原文标题:基于UVM验证环境开发测试用例

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

整车环境测试耐久试验主要测什么?有哪些特点?流程和方法

基于 NineData 的多环境表结构变更流程编排实践

NVMe高速传输之摆脱XDMA设计24: UVM 验证包设计

基于UVM验证环境开发测试流程

基于UVM验证环境开发测试流程

评论