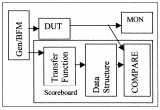

芯片验证中的checker和scoreboard介绍

典型的和验证组件相对比较独立的checker,这些checker通常与时序相关,例如检查DUT中的状....

芯片功能验证中的Sequences和Scenarios介绍

如果你做过功能验证并且开发过随机用例,那么你就会知道场景组合会如雪球般地爆炸增长。

受约束随机验证的效果真的比直接用例测试好吗?

当介绍uvm验证时大家肯定都看过上面类似的图片,以展示受约束的随机验证相比直接用例测试如何具有先进性....

使用SystemVerilog解决数组问题

数独是一种非常流行的游戏,数独本质上也是一个约束问题,所以我们可以让SystemVerilog的约束....

为什么不是uvm_transaction构建UVM事务呢?

UVM 中的事务是一个具有信号属性(例如地址和数据)以及错误、延迟等额外信息的类。总之,这个所谓事务....

一些有趣的数组相关的SystemVerilog约束

我们在工作中常常会针对数组施加各式的约束,下面列举一下有趣的Systemverilog数组约束示例。

可以通过降低约束的复杂度来优化Formal的执行效率吗?

我们可以通过降低约束的复杂度来优化Formal的执行效率,但是这个主要是通过减少Formal验证空间....

介绍一种能够完成自然语言和SVA相互转换的小工具

结论就是,SVA本身就是比较清晰的描述性语言,SVA和自然语言的转换工具基本上没有价值吧。

SVA Assertion有什么优势?

如果我们设计正确工作时需要满足FRAME_上升沿后的1~2拍会出现LDP_的下降沿,如下图所示

System Verilog中的Mailboxes

Mailboxes是进程间通信的另一种方式,但是比semaphores更强大,因为Mailboxes....

SystemVerilog中的fork-join_none

fork-join_none和fork-join、fork-join_any的区别一样在于进程退出机....

SystemVerilog中的电平敏感事件控制

在verilog中绝大多数使用的都是边沿敏感事件,例如@(posedge event)和@(nege....

SystemVerilog中的Semaphores

SystemVerilog中Semaphore(旗语)是一个多个进程之间同步的机制之一,这里需要同步....