声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22287浏览量

630303 -

转换器

+关注

关注

27文章

9365浏览量

155125 -

ADI

+关注

关注

150文章

46086浏览量

270612

发布评论请先 登录

相关推荐

热点推荐

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于JESD204B应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK0482x系列超低噪声JESD204B兼容时钟抖动清除器技术文档总结

转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于JESD204B应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。16 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 8 个 JESD204B 转换器或其

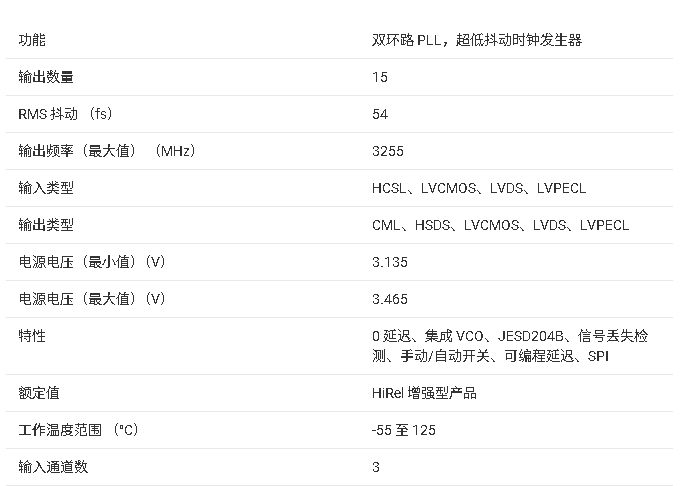

LMK04828-EP 超低噪声JESD204B兼容时钟抖动清除器总结

LMK04828-EP 器件是业界性能最高的时钟调理器,支持 JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻

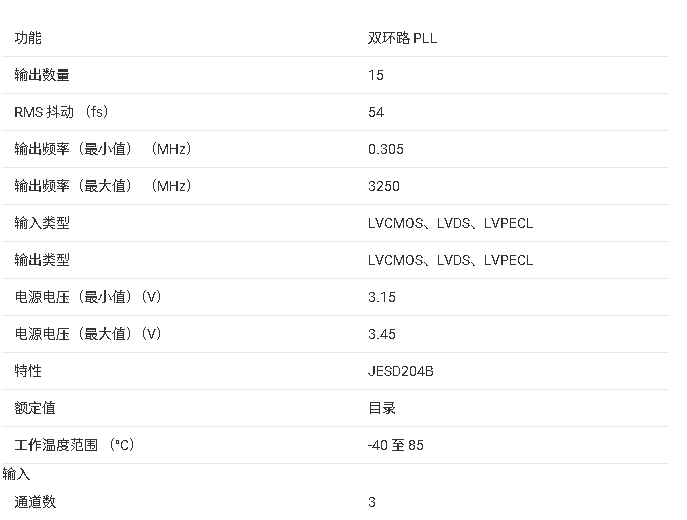

LMK04832 超低噪声、3.2 GHz、15 输出、JESD204B 时钟抖动清除器技术手册

JESD204B转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于JESD204B应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK04368-EP 超低噪声JESD204B/C双环路时钟抖动清除器总结

JESD204B/C 转换器或其他逻辑器件。SYSREF 可以使用直流和交流耦合提供。不仅限于 JESD204B/C 应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

1. 概述PC7044是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B型)接口的高速数据转换器执行参考时钟选择和超低噪声频率的生成。 PC7044具有两个整

发表于 05-08 15:57

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册

C subclass 1 器件时钟 / SYSREF 对以及一个通用输出,或者就是 11 个面向非 JESD204B/JESD204C 应用的通用时钟输出。每个输出都有自己的可个别编程分频器和输出驱动

AD9680 JESD204B接口的不稳定会导致较大的电流波动,怎么解决?

AD采集芯片为AD9680-1000,时钟芯片为AD9528。当 AD 采样时钟为 500MHz 时,jesd204B (串行线速 = 5 Gbps) 稳定。但是,当 AD 采样时钟为 800MHz

发表于 04-15 06:43

使用jesd204b IP核时,无法完成综合,找不到jesd204_0.v

做的,但是去问的时候人家说是根据两个IP核的示例工程中的某个文件来在jesd204b_base.v中例化,其他的对方不记得了,这里想问下这个问题该怎么解决?

发表于 03-12 22:21

JESD204B有专用于ADC/DAC和FPGA或ASIC的接口吗?

请问各位大侠:JESD204B专用于ADC/DAC和FPGA或ASIC的接口吗,该接口同Rapid/PCIe的物理层Serdes接口有何区别,谢谢!

发表于 02-08 09:10

TI ADS42JB69系列JESD204B ADC与Altera FPGA的互操作性

电子发烧友网站提供《TI ADS42JB69系列JESD204B ADC与Altera FPGA的互操作性.pdf》资料免费下载

发表于 12-10 14:27

•2次下载

两种JESD204B A/D转换器转FPGA设置与实现技巧

两种JESD204B A/D转换器转FPGA设置与实现技巧

评论