AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析

在电子设计领域,时钟发生器对于系统的稳定运行起着至关重要的作用。今天,我们就来深入探讨一款功能强大的时钟发生器——AD9528,它在高性能无线通信、医疗仪器等众多领域都有着广泛的应用。

文件下载:AD9528.pdf

一、AD9528的关键特性

1. 输出配置灵活

AD9528拥有14个输出通道,这些输出可灵活配置为HSTL或LVDS电平。其中,6个输出的最高频率可达1.25 GHz,另外8个输出最高频率可达1 GHz,具体频率取决于压控晶体振荡器(VCXO)的频率精度,其启动频率精度小于100 ppm。

2. 精准的延时控制

每个输出都配备了专用的8位分频器,具备粗延时和细延时功能。粗延时有63个步长,为RF VCO分频器输出频率周期的1/2,且不会引入抖动;细延时有15个步长,分辨率为31 ps。典型的输出间偏斜仅为20 ps,还能对奇数分频设置进行占空比校正。

3. 低抖动性能

在122.88 MHz、12 kHz至20 MHz的积分范围内,绝对输出抖动小于160 fs,能有效满足对时钟精度要求极高的应用场景。

4. 丰富的控制与监测功能

具备数字频率锁定检测功能,支持SPI和I²C兼容的串行控制端口,方便工程师进行配置和调试。采用双PLL架构,PLL1可对参考输入时钟进行清理,PLL2则能提供高频时钟,实现低积分抖动和低宽带噪声。

二、工作原理剖析

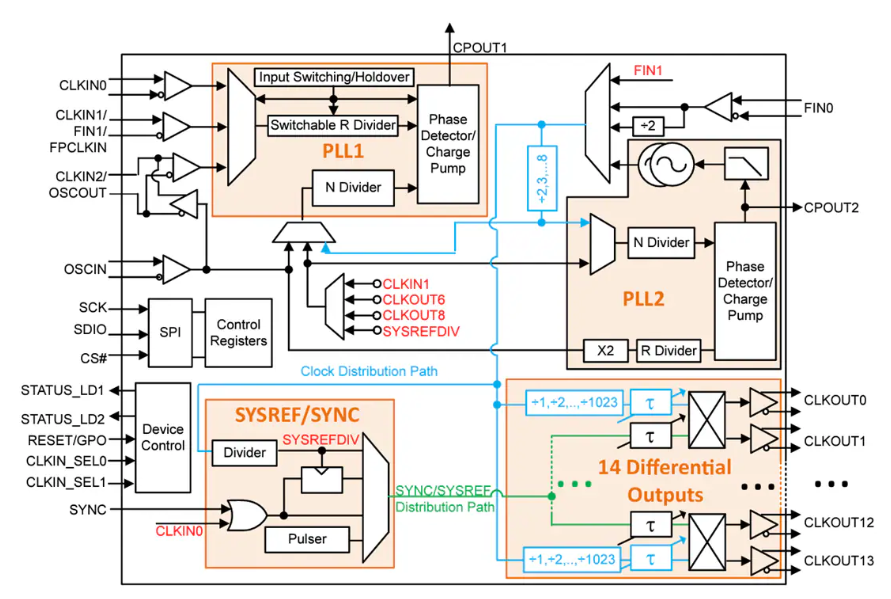

1. 双PLL架构

- PLL1:由鉴相器(PFD)、电荷泵、外部VCXO和部分外部环路滤波器组成。它能够以较窄的环路带宽工作,有效抑制输入参考信号上的抖动,其低相位噪声输出可作为PLL2的参考,也能路由到时钟分配部分。

- PLL2:包含可选的输入参考2×乘法器、参考分频器、PFD、集成模拟环路滤波器、集成压控振荡器(VCO)和反馈分频器。VCO的频率范围为3.450 GHz至4.025 GHz,能自动选择合适的频段。

2. 时钟分配

时钟分配部分由14个独立通道组成,每个通道的输入频率源可选择PLL1输出、PLL2输出或SYSREF。每个通道还包括一个专用的8位分频器、两个专用的相位延迟元件和一个输出驱动器,可实现输出通道的同步和相位调整。

3. SYSREF操作

AD9528支持JESD204B/JESD204C标准,可提供成对的设备时钟和SYSREF时钟信号,用于同步高速转换器和逻辑设备。SYSREF信号有外部和内部两种来源,可通过寄存器进行三种模式的配置,满足不同应用的需求。

三、电气特性详解

1. 电源与电流

- 电源电压:VDDx为3.3 V ± 5%,涵盖多个VDD引脚。

- 电源电流:不同工作模式下的电源电流有所不同,如双环模式、单环模式、缓冲模式和芯片掉电模式等。以双环模式为例,不同VDD引脚的电流典型值在19 mA至71 mA之间。

- 功耗:典型双环模式下的总功耗约为1675 mW,还给出了不同输出模式下的增量功耗。

2. 输入与输出特性

- 输入特性:支持差分和单端输入,输入频率范围、灵敏度、电容等参数都有明确规定。

- 输出特性:HSTL和LVDS模式下的输出频率、上升/下降时间、占空比、差分输出电压摆幅等特性各有特点。例如,HSTL模式下输出频率最高可达1.25 GHz,LVDS模式下输出频率最高可达1 GHz。

3. 抖动与相位噪声

在不同工作模式和输出频率下,时钟输出的绝对时间抖动和绝对相位噪声都有详细的测试数据。如在双环模式下,HSTL输出在122.88 MHz、12 kHz至20 MHz积分范围内的绝对时间抖动典型值为159 fs。

四、应用案例

1. 无线通信领域

在高性能无线收发器、LTE和多载波GSM基站等设备中,AD9528可提供低抖动、低相位噪声的时钟信号,确保信号的准确传输和处理。

2. 医疗仪器领域

在医疗仪器中,高精度的时钟信号对于数据采集和处理至关重要。AD9528的低抖动特性能够满足医疗仪器对时钟精度的严格要求,提高设备的性能和可靠性。

五、设计建议

1. 电源设计

由于AD9528的功耗较大,在设计电源时要确保电源的稳定性和足够的功率输出。同时,要注意各个VDDx引脚的供电,即使某些部分不使用,也需为所有VDDx引脚供电。

2. 布局布线

合理的布局布线对于减少信号干扰和提高性能至关重要。要将敏感的时钟信号与其他信号分开,避免相互干扰。同时,要注意外部环路滤波器和去耦电容的布局,确保其靠近芯片引脚。

3. 散热设计

考虑到AD9528的功耗,散热设计不容忽视。可根据实际应用情况选择合适的散热方式,如使用散热片、风扇等,确保芯片在安全的温度范围内工作。

六、总结

AD9528作为一款高性能的JESD204B/JESD204C时钟发生器,具有输出配置灵活、延时控制精准、低抖动性能等诸多优点。通过深入了解其工作原理和电气特性,工程师可以更好地将其应用于各种电子系统中。在设计过程中,要注意电源、布局布线和散热等方面的问题,以充分发挥AD9528的性能优势。希望本文能为电子工程师在使用AD9528进行设计时提供有益的参考。

你在使用AD9528的过程中遇到过哪些问题?或者你对它的应用有什么独特的见解?欢迎在评论区留言分享。

-

时钟发生器

+关注

关注

1文章

357浏览量

70160 -

电子设计

+关注

关注

42文章

2870浏览量

49916 -

ad9528

+关注

关注

1文章

6浏览量

2974

发布评论请先 登录

AD9094:8位、1 GSPS、JESD204B四通道ADC的深度解析

高性能时钟分配利器:LTC6953深度解析

LMK04828 超低噪声JESD204B兼容时钟抖动清除器技术手册

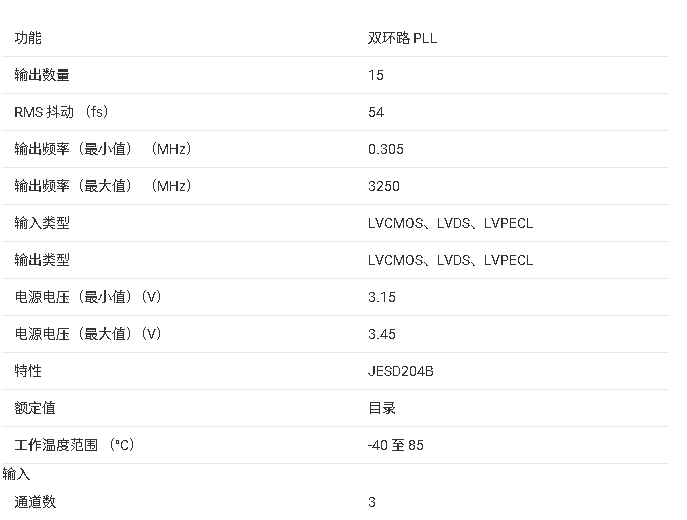

LMK0482x系列超低噪声JESD204B兼容时钟抖动清除器技术文档总结

LMK04616 超低噪声低功耗JESD204B兼容时钟抖动清除器总结

LMK04828-EP 超低噪声JESD204B兼容时钟抖动清除器总结

LMK04832 超低噪声、3.2 GHz、15 输出、JESD204B 时钟抖动清除器技术手册

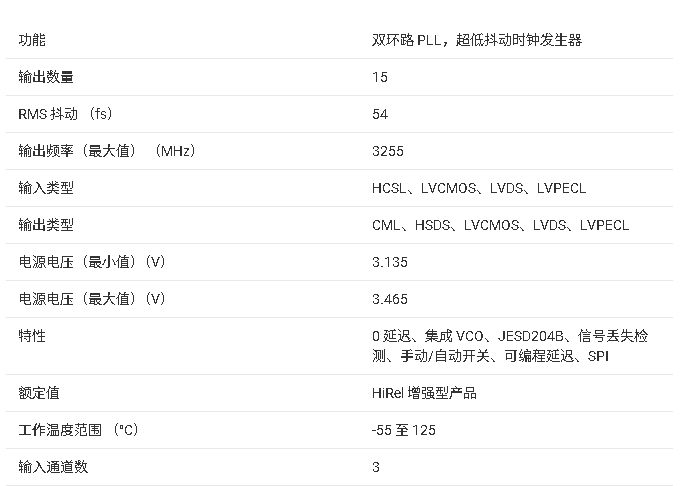

LMK04368-EP 超低噪声JESD204B/C双环路时钟抖动清除器总结

AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析

AD9528:高性能JESD204B/JESD204C时钟发生器的深度解析

评论