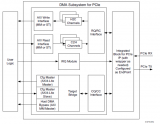

本视频将介绍 Xilinx PCIe DMA 子系统的设置过程与性能测试,先展示可实现的硬件性能,然后说明用软件进行实际传输怎么会影响性能。最后将讨论不同的选项,以提高包括选择最佳传输量与轮询在内的性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

133164 -

硬件

+关注

关注

11文章

3556浏览量

68757 -

PCIe

+关注

关注

16文章

1424浏览量

87589

发布评论请先 登录

相关推荐

热点推荐

Amphenol HD Express®:满足PCIe® Gen 6需求的高性能互连系统

Amphenol HD Express®:满足PCIe® Gen 6需求的高性能互连系统 在当今高速发展的电子科技领域,对于高性能、高密度互连系统

Xilinx高性能低延时8通道PCIe-DMA控制器IP,SGDMA,QDMA,CDMA,RDMA, V4L2驱动,高速视频采集, 高速AD采集

实现Host存储器和PCIe DMA子系统之间的数据搬移。这些DMA可以同时是Host to Card(H2C)和Card to Host(C2H)传输。每个

发表于 12-11 11:07

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

是4K-Byte,最大是512K-Byte。每次读写访问,用户可以指定本次传输的顺序传输长度(4K~512K Byte),不同的顺序传输长度对应不同的DMA读写性能。针对多路数据通道访问PCIe SSD

发表于 11-14 22:40

双Zynq MPSoC PS侧PCIe高速DMA互连解决方案

在涉及Xilinx Zynq UltraScale+ MPSoC的项目中,实现设备间高速、低延迟的数据传输往往是核心需求之一。PCIe(尤其PS侧)结合DMA(直接内存访问)正是满足这类需求的理想技术方案。

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

子系统模型组成。UVM验证包用于构建测试用例、提供激励、监测接口、对比分析统计测试结果;DUT 为待测试对象即 NoP 逻辑加速引擎;AXI BRAM IP 用于模拟外部存储,对接

发表于 08-26 09:49

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

子系统模型组成。UVM验证包用于构建测试用例、提供激励、监测接口、对比分析统计测试结果;DUT 为待测试对象即 NoP 逻辑加速引擎;AXI BRAM IP 用于模拟外部存储,对接

发表于 07-31 16:39

PCIe协议分析仪能测试哪些设备?

场景:分析连接到PCIe总线的NVMe存储设备的性能,评估高速数据读写时的表现。

应用价值:优化存储子系统,确保其满足大规模数据集训练任务的需求。

企业级存储阵列

测试场景:

发表于 07-25 14:09

NVMe IP高速传输却不依赖便利的XDMA设计之三:系统架构

请求数据传输, 数据传输通过 AXI4总线接口对接用户逻辑, 使用突发传输提高数据传输性能。

图1 Nvme逻 辑加速IP系统架构图

新系统中,Nvme逻辑加速IP通过 PCIe 3.

发表于 06-29 17:42

基于AMD Versal器件实现PCIe5 DMA功能

Versal是AMD 7nm的SoC高端器件,不仅拥有比16nm性能更强的逻辑性能,并且其PS系统中的CPM PCIe也较上一代MPSoC PS硬核

RK3568驱动指南|第十二篇 GPIO子系统-第135章 GPIO子系统与pinctrl子系统相结合实验

RK3568驱动指南|第十二篇 GPIO子系统-第135章 GPIO子系统与pinctrl子系统相结合实验

基于PCIe(XDMA/QDMA)的多路视频采集与显示IP 多路高速AD采集与DA回放IP

队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。在超带宽视频采集情况下,支持采集丢帧操作,后续视频可以正常采集。视频采集与显示子系统使用高效的PCIe

发表于 04-14 15:17

在RC测试中执行pcitest-S-r-s 1024后ep系统崩溃了怎么解决?

] pci_epf_test pci_epf_test.0:无法获取 DMA 通道

在 RC 测试中执行 pcitest-S-r-s 1024 后 ep 系统崩溃

发表于 03-25 07:04

PCIE XDMA开发环境搭建以及环路测试

大家 XILINX FPGA PCIE 应用解决方案。 本教程以MZ7035FA作为样机测试。在正式开始教程内容前,有必要把MZ7035FA开发板的特点说明下。这是一款高性价比的FPGA开发板。带

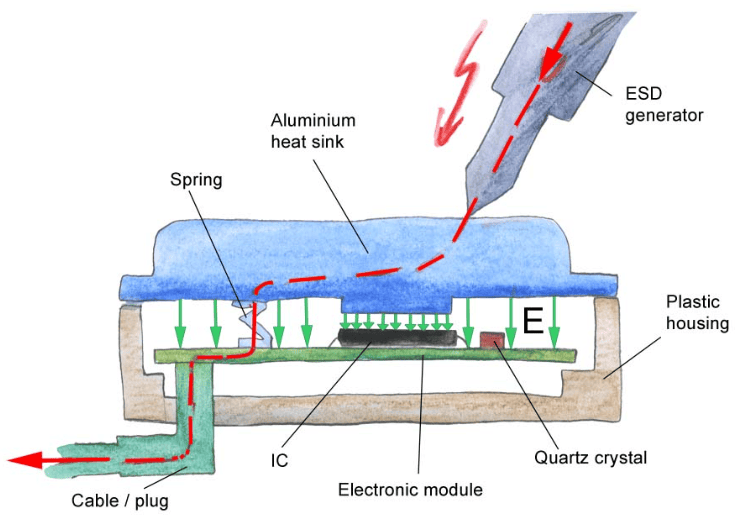

集成电路电磁兼容性及应对措施相关分析(一) — 电子系统性能要求与ESD问题

此专题将从三个方面来分享: 一、电子系统性能要求与ESD问题 二、集成电路ESD问题应对措施 三、集成电路ESD 测试与分析 工业、消费及汽车电子模块开发的 EMC 问题会导致极高的开发成本和时间

Xilinx PCIe DMA子系统的性能测试

Xilinx PCIe DMA子系统的性能测试

评论