本期文章《基于AMD Versal器件实现PCle5 DMA功能》,诚邀您率先了解如何利用Versal强大性能实现高速数据传输!

序言

Versal是AMD 7nm的SoC高端器件,不仅拥有比16nm性能更强的逻辑性能,并且其PS系统中的CPM PCIe也较上一代MPSoC PS硬核PCIe单元强大得多。本节将基于AMD官方开发板展示如何快速部署PCIe5x8及DMA功能。

1测试环境

Vivado版本:2023.2/2024.2,在windows10或者ubuntu22.04

实验板卡:VPK120

上位机主板:EPYC9124超微主板

上位机系统:Ubuntu20.04/24.04

2Vivado工程生成

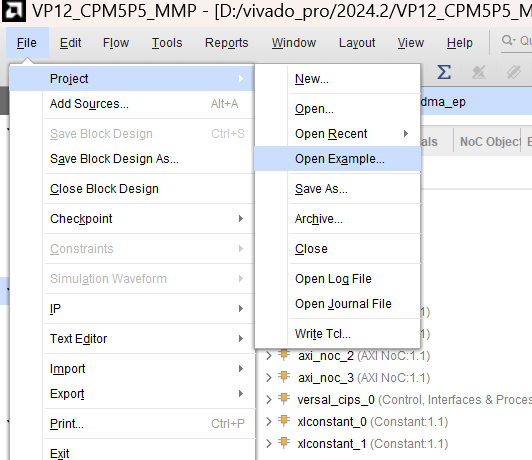

File->Project->Open Example

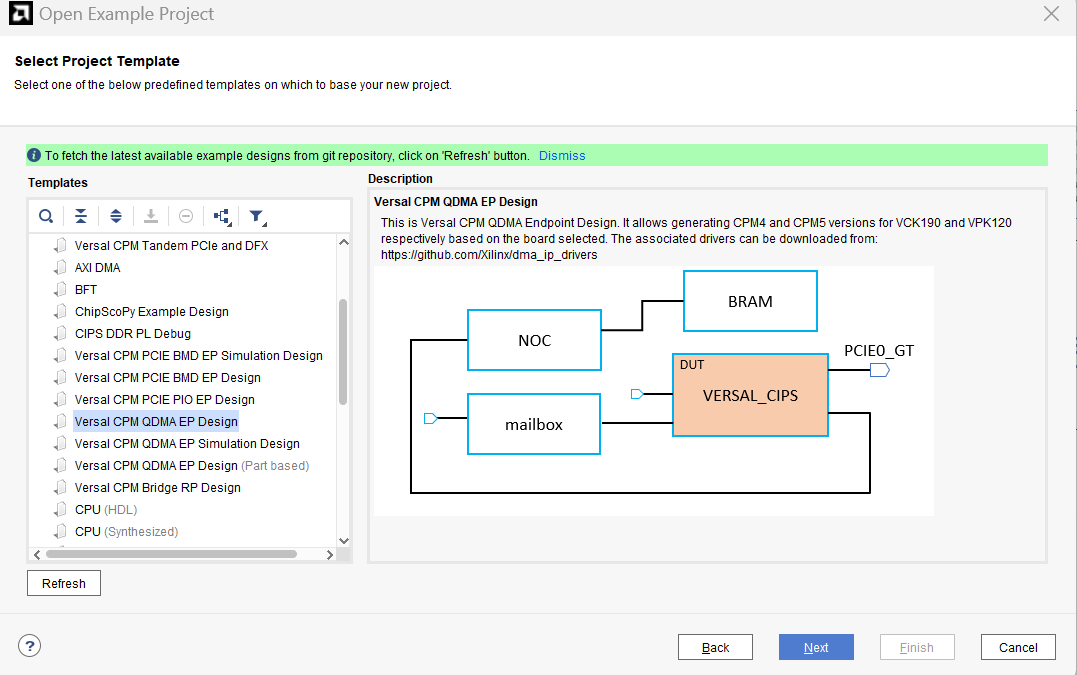

选择Versal CPM QDMA EP Design

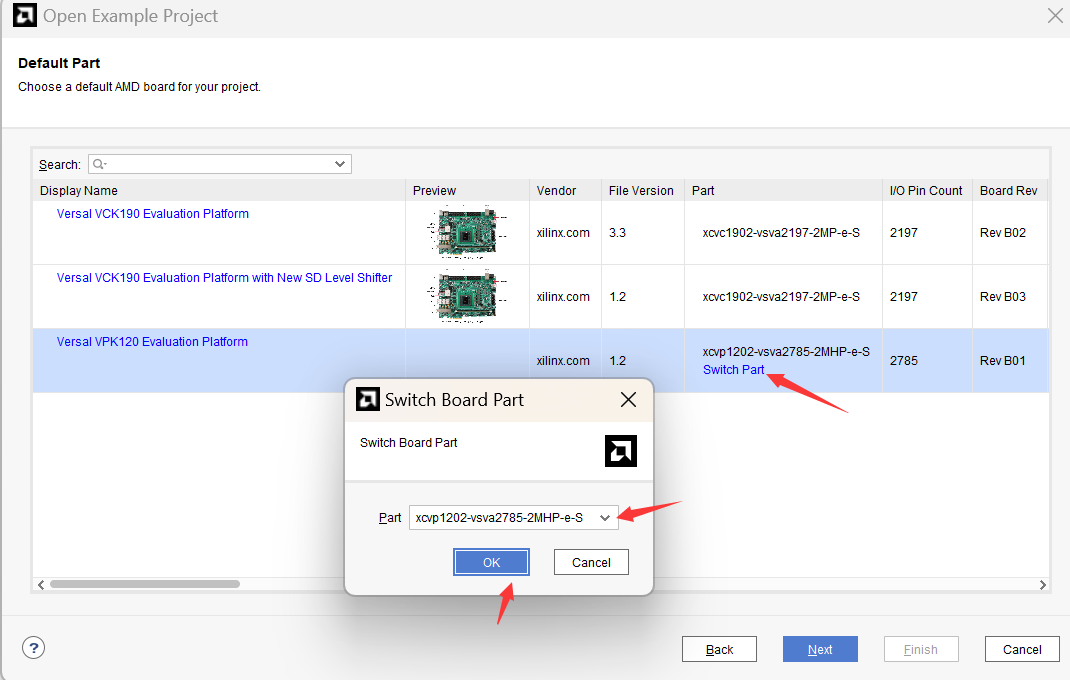

选择名称以后,选择器件,注意选择MHP

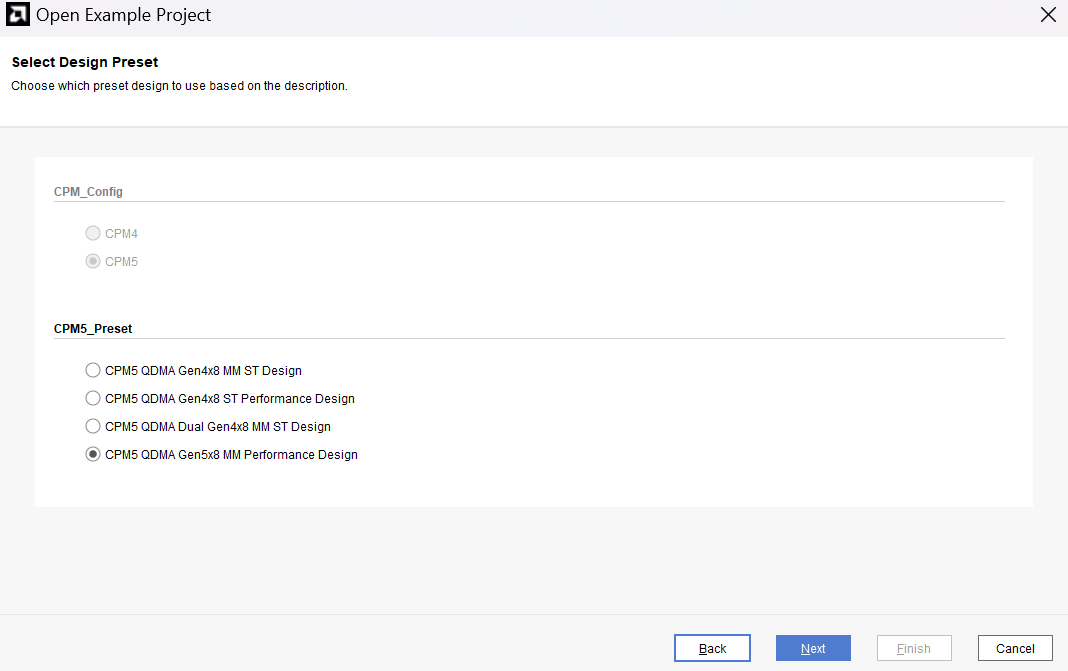

打开CPM5 QDMA Gen5x8 MM Performance Design,然后finish即可

3BD工程介绍与配置

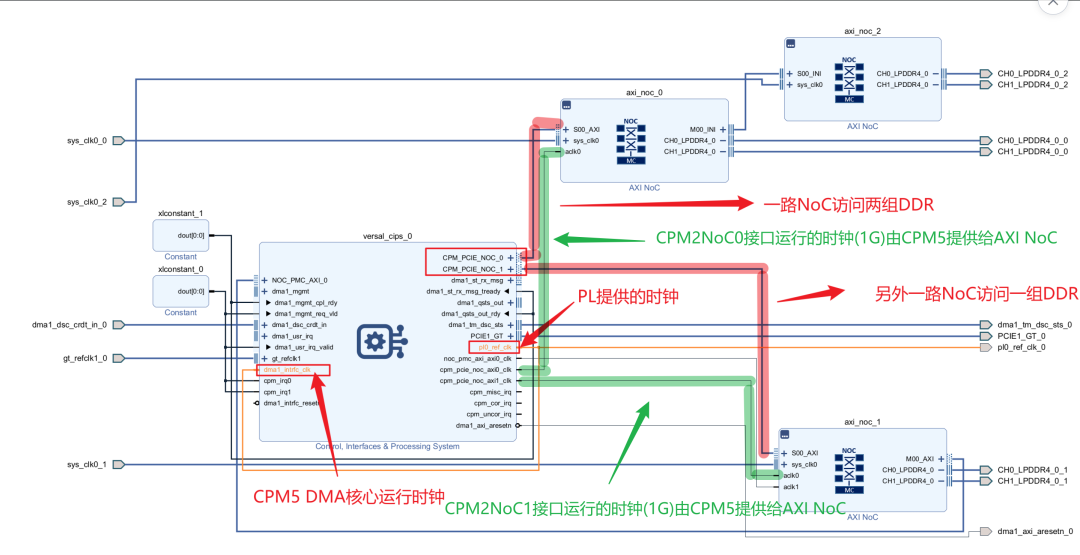

可以看到从CIPS IP中出现两个CPM_PCIE_NOC口去访问两边的DDR:

1)数据访问架构:

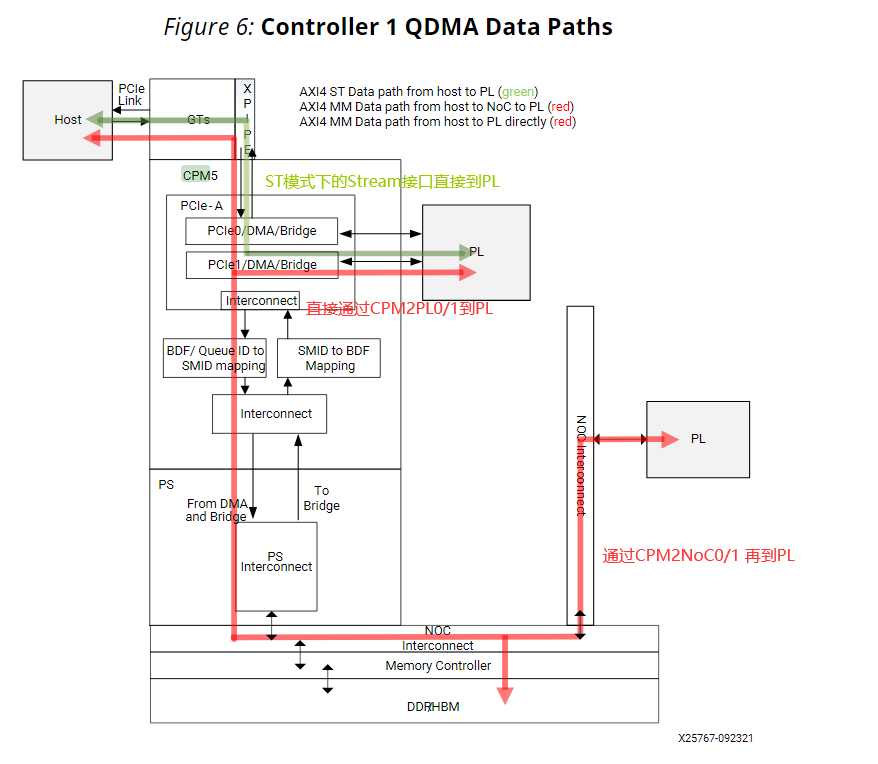

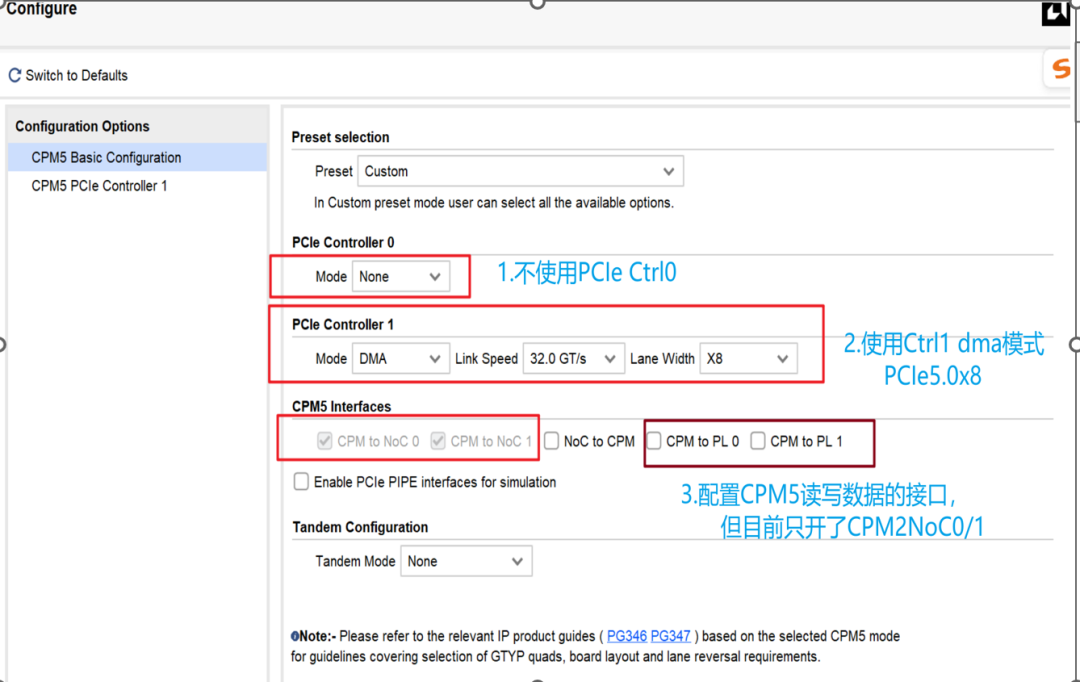

在VPK120上有两个CPM控制器0与1,控制器1访问数据的路径有以下三种:ST_CPM2PL、MM_CPM2NoC、MM_CPM2PL,本次示例用两个MM_CPM2NoC,通过NoC直接从DDR中搬运数据。

2)相关端口

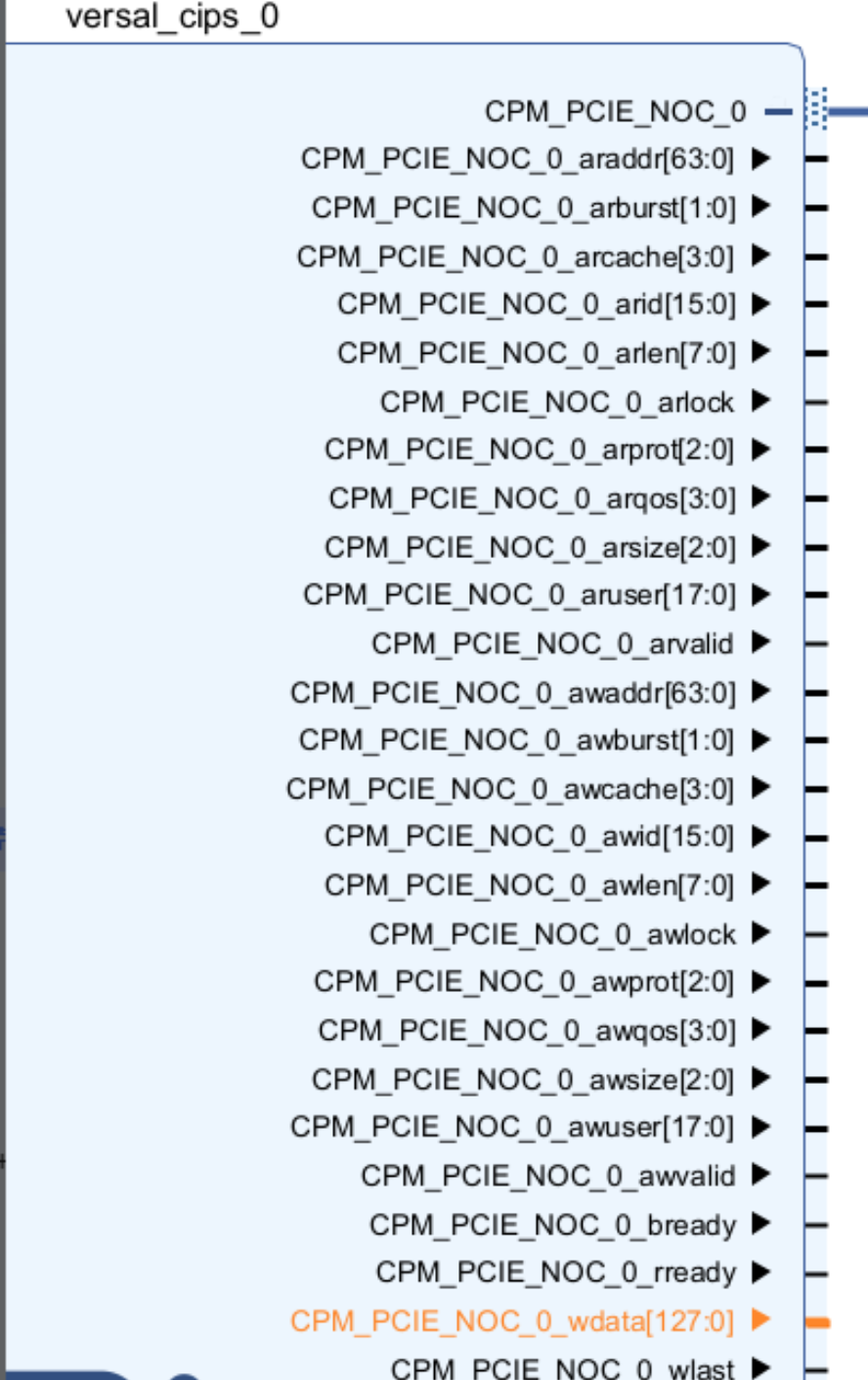

为什么开两个?

下图是MM_CPM2NoC接口,看CPM2NoC接口的位宽与带宽,由于走的是NoC,所以其单个接口的理论带宽是128bit x 1000M(NoC运行频率)=16GB,而PCIe5x8的理论带宽是32GB/s,为此至少需要两个MM端口,又由于担心DDR访问影响,所以demo中两个端口同时去访问两组DDR,保证带宽尽量不受DDR的影响。

为什么选用MM接口,而不是ST接口?

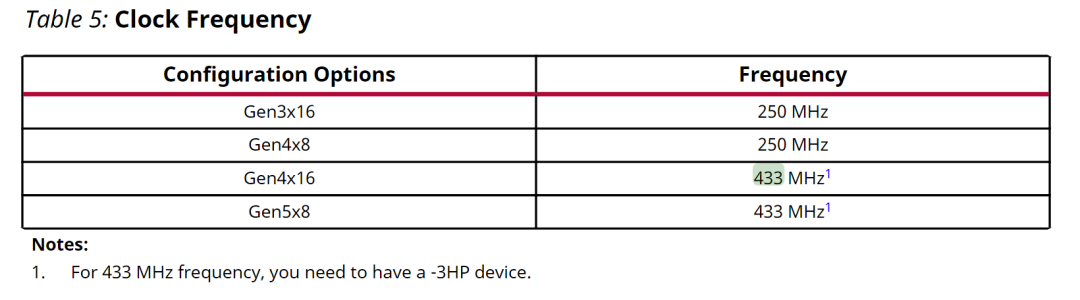

根据ds959手册以及PG347手册,ST模式下由于只会有一组ST_CPM2PL接口,而且位宽是512bit,所以理论上要到达PCIe5x8的带宽,是需要时钟跑到500M,但由于器件限制,其时钟最高是433M,实际综合下来时序收敛挑战很大。

3)细节配置

注意:CPM控制器0的数据路径不如控制器1多,少了MM_CPM2PL,为此这里选择控制器1。

如果要实现两路PCIe5x8,则需要将棕色框两个接口勾选上。

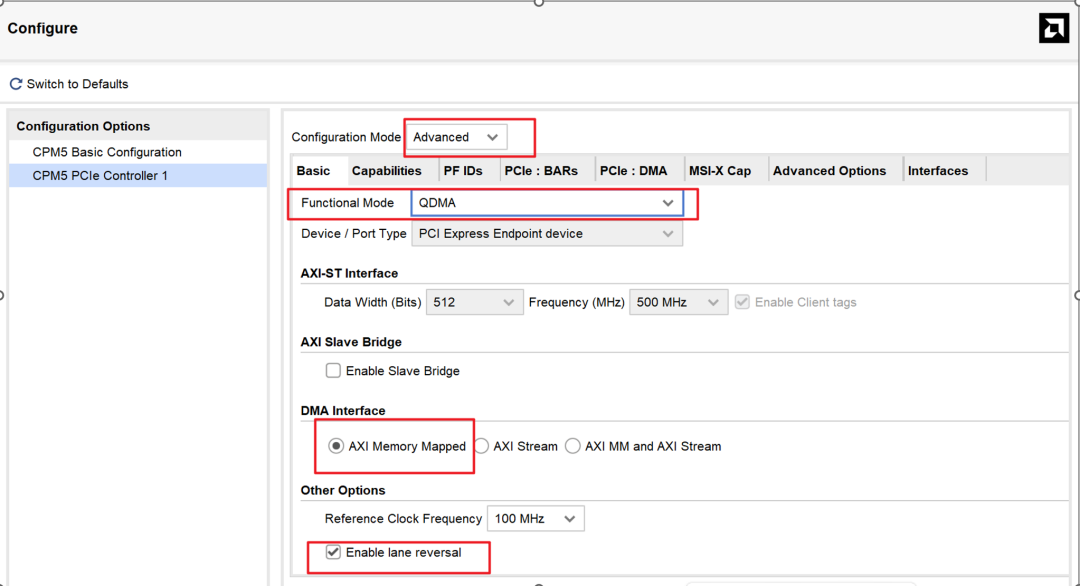

选择QDMA模式下的AXI MM,根据硬件结构选择Lane翻转。

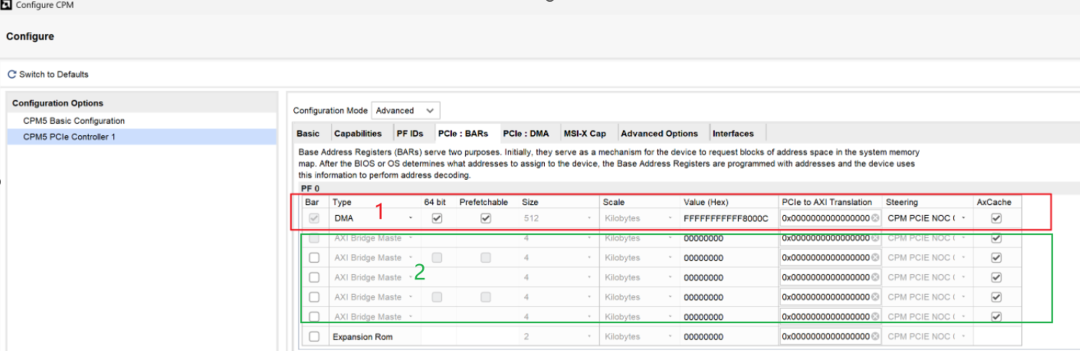

选择bar空间

1:是主要的数据路径接口;

2:类似于之前XDMA挂载寄存器的方式。

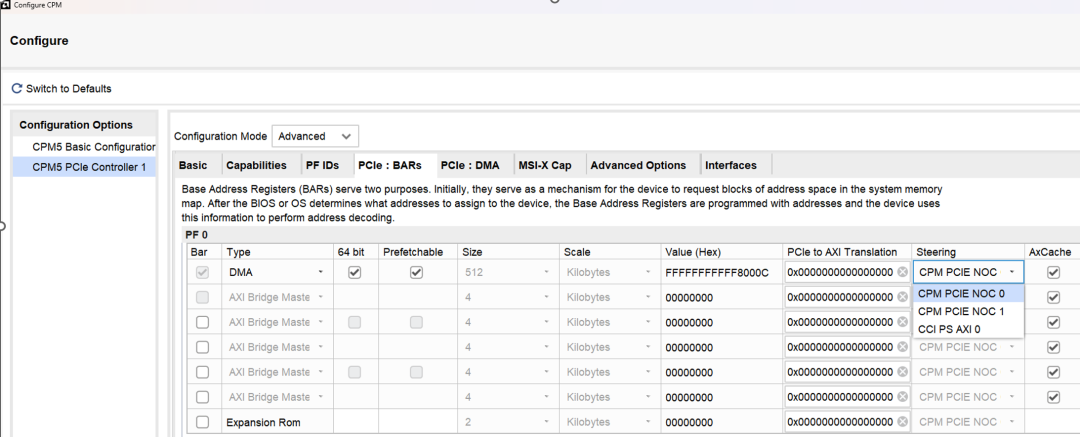

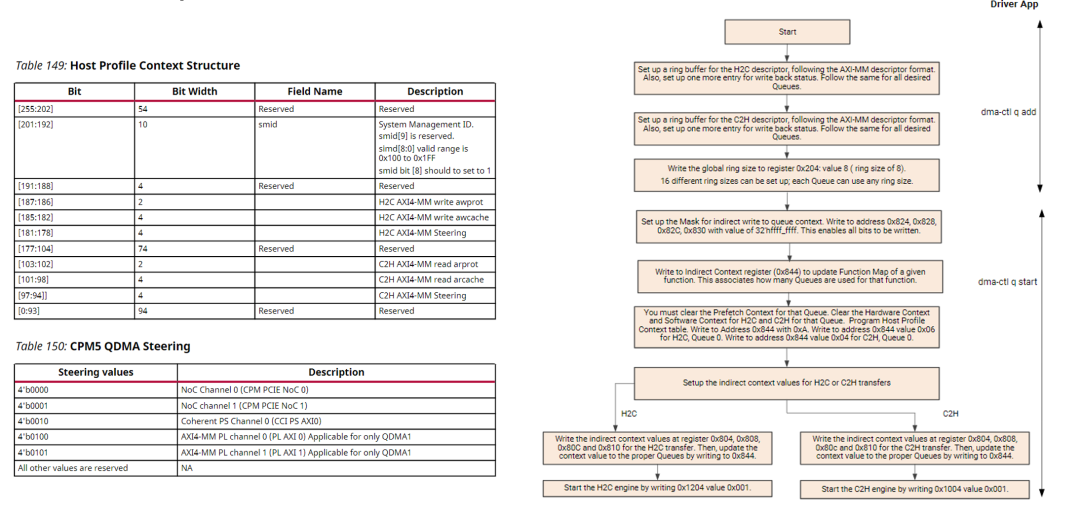

转向器选择:这里默认只选择CPM2NoC0,这个后续通过Host profile来指定使用两个CPM2NoC接口

4实际运行配置

在配置完后,直接编译后,进入实操环节

安装驱动

参考《pg347》的Using the Provided Software and Drivers章节

#下载驱动源码,注意最好跟vivado版本对应上,master是最新的,对应vivado2024.1/2

git clone https://github.com/Xilinx/dma_ip_drivers.git

#如果之前已经加载过驱动,则先删除驱动

rmmod qdma_pf

rm -rf dma_ip_drivers

#清理+编译

make clean & make

make install

modprobe qdma-pf #安装驱动

lspci -vvv -d 10ee: #查看设备节点是否存在

配置host profile

参考《pg347》的Host profile章节以及下面的链接

https://adaptivesupport.amd.com/s/article/000035811?language=en_US

是通过相关设备节点配置寄存器

执行CFG启动测试

CFG相关参考:

https://adaptivesupport.amd.com/s/article/Understanding-the-Versal-CPM5-QDMA-Gen4x8-ST-Only-Performance-Design-CED-Example-in-Vivado-2023-2?language=en_US

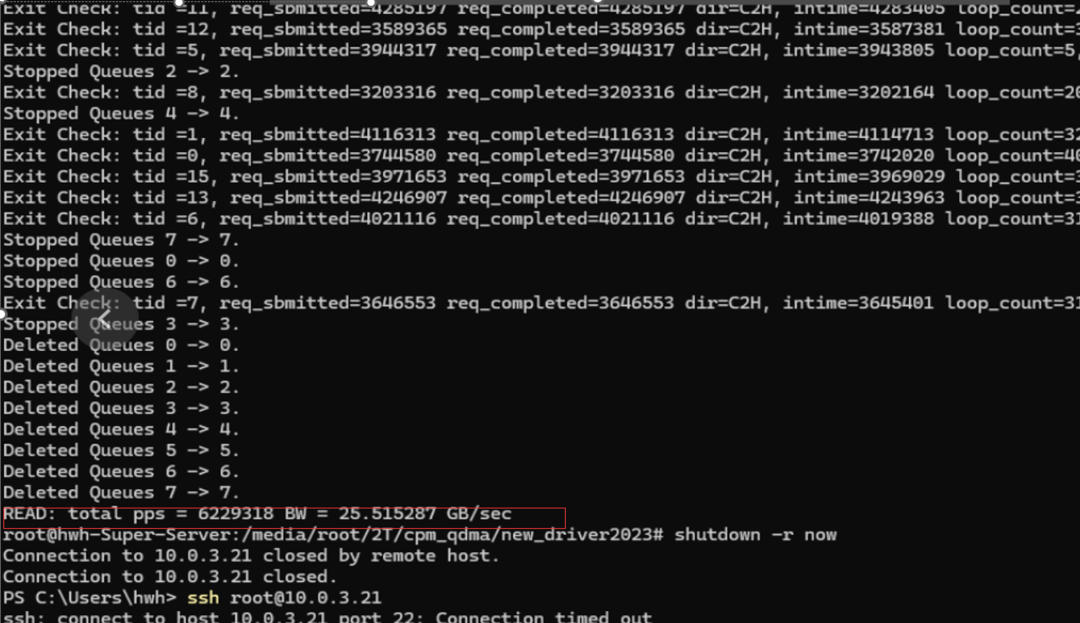

可以看到能够到25GB/s左右

5总结

AMD Versal器件CPM单元集成了硬核QDMA功能,只需使用少量逻辑便能实现PCIe Gen5高带宽数据传输。同时官方也集成好了dma-perf等测试程序以及相关驱动,可以快速地进行验证与产品化,但需要注意的是MM模式的优劣以及性能影响因素,比如DDR、NoC带宽等,不是所有应用都适用,适当在ST与MM模式下做选择,可以帮助实现更高的性能。如果想在一个VP1202上实现两个PCIe5x8 MM,如果想在一个VP1202上实现两个PCIe5x8 MM,您可发送邮件至此邮箱寻求技术支持:AMD-xilinxchina@avnet.com。

关于安富利

安富利是全球领先的技术分销商和解决方案提供商,在过去一个多世纪里一直秉持初心,致力于满足客户不断变化的需求。通过遍布全球的专业化和区域化业务覆盖,安富利可在产品生命周期的每个阶段为客户和供应商提供支持。安富利能够帮助各种类型的公司适应不断变化的市场环境,在产品开发过程中加快设计和供应速度。安富利在整个技术价值链中处于中心位置,这种独特的地位和视角让其成为了值得信赖的合作伙伴,能够帮助客户解决复杂的设计和供应链难题,从而更快地实现营收。

-

amd

+关注

关注

25文章

5655浏览量

139102 -

soc

+关注

关注

38文章

4522浏览量

227769 -

开发板

+关注

关注

26文章

6152浏览量

113964 -

Vivado

+关注

关注

19文章

848浏览量

70529

原文标题:基于AMD Versal器件实现PCIe5 DMA功能

文章出处:【微信号:AvnetAsia,微信公众号:安富利】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AMD 7nm Versal系列器件NoC的使用及注意事项

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

《电子发烧友电子设计周报》聚焦硬科技领域核心价值 第16期:2025.06.16--2025.06.20

PCIe DMA设计实现

Versal CPM AXI Bridge模式的地址转换

基于AMD FPGA的PCIE DMA逻辑实现

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD推出第二代Versal Premium系列

第二代AMD Versal Premium系列产品亮点

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

基于AMD Versal器件实现PCIe5 DMA功能

基于AMD Versal器件实现PCIe5 DMA功能

评论