SN74F1056 8位肖特基势垒二极管总线终端阵列:设计与应用解析

引言

在电子系统设计中,总线反射噪声和负瞬变问题常常影响系统的稳定性和性能。SN74F1056 8位肖特基势垒二极管总线终端阵列作为一款专门设计用于解决这些问题的器件,在众多电子设备中发挥着重要作用。本文将深入探讨 SN74F1056 的特性、参数以及应用场景,为电子工程师在实际设计中提供参考。

文件下载:SN74F1056DG4.pdf

产品概述

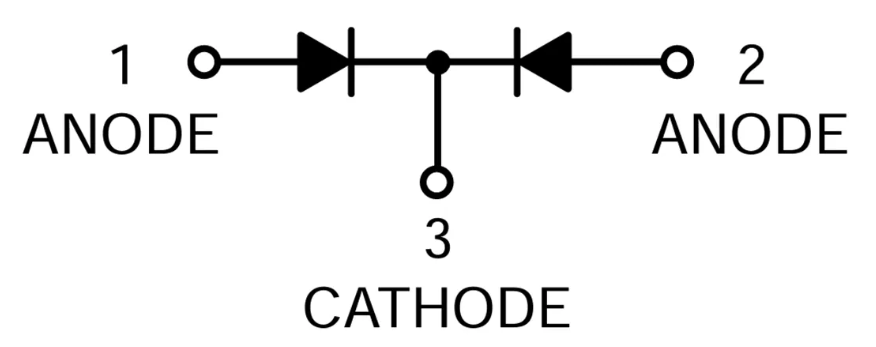

SN74F1056 是一款 8 位肖特基势垒二极管总线终端阵列,其主要设计目的是降低内存总线上的反射噪声。该器件采用 8 位高速肖特基二极管阵列,适合接地钳位,工作温度范围为 0°C 至 70°C。

封装形式

它有 SC 和 D 两种封装形式,不同封装的引脚排列有所不同。SC 封装有 16 个引脚,D 封装有 10 个引脚,具体引脚定义可参考文档中的引脚图。

电气特性

绝对最大额定值

在使用 SN74F1056 时,需要注意其绝对最大额定值,以避免对器件造成永久性损坏。以下是一些关键的绝对最大额定值参数:

- 稳态反向电压($V_R$):7V

- 连续正向电流($I_F$):任何 D 端子到地为 50 mA,所有接地端子的总电流为 170 mA

- 重复峰值正向电流($I_{FRM}$):任何 D 端子到地为 300 mA,所有接地端子的总电流为 1.2A

- 连续总功耗:在 25°C 自由空气温度下为 500 mW

- 工作自由空气温度范围:0°C 至 70°C

- 存储温度范围:未明确给出

需要注意的是,超出这些绝对最大额定值的应力可能会导致器件永久性损坏,并且在超出推荐工作条件的情况下,器件的功能操作并不被保证。

电气特性参数

单二极管操作

| 在单二极管操作模式下,有以下关键参数: | 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| 静态反向电流($R$) | $V_R = 7V$ | 2 | μA | |||

| 静态正向电压($V_F$) | $I_F = 18 mA$ | 0.8 | 1 | V | ||

| $I_F = 50 mA$ | 1 | 1.2 | ||||

| 峰值正向电压($V_{FM}$) | $I_F = 200 mA$ | 1.23 | V | |||

| 总电容($C_t$) | $V_R = 0$,$f = 1 MHz$ | 3 | 3.75 | pF | ||

| $V_R = 2V$,$f = 1 MHz$ | 2.5 | 3 |

所有典型值均在 $T_A = 25°C$ 下测量,并且测试条件和限制分别适用于每个二极管,在测量这些特性时,未测试的二极管处于开路状态。

多二极管操作

在多二极管操作模式下,内部串扰电流是一个重要参数。当总接地电流为 1.2A 时,内部串扰电流的典型值为 50 μA,最小值为 10 μA。

开关特性

在 $TA = 25°C$ 时,反向恢复时间($t{rr}$)在特定测试条件下($IF = 10 mA$,$I{RM(REC)} = 10 mA$,$R_{(REC)} = 1 mA$,$R_L = 100Ω$)的典型值为 5 ns。

下冲特性

下冲电压($V_{US}$)在特定测试条件下($2 ns$,$tW = 50 ns$,$V{IH} = 5 V$,$V_{IL} = 0$,$Z_S = 25 Ω$,$Z_O = 50 Ω$,36 英寸同轴电缆)的典型值为 0.6 V,最大值为 0.7 V。

应用场景

抑制负瞬变

在内存设备(如 DRAMs、SRAMs、EPROMs 等)的输入或许多时钟设备的时钟线上,大的负瞬变可能导致设备运行不正常。SN74F1056 二极管终端阵列可以帮助抑制由传输线反射、串扰和开关噪声引起的负瞬变。

与电阻终端方案相比,二极管终端具有多个优势。例如,分裂电阻或戴维南等效终端可能会导致功耗大幅增加;使用单个接地电阻来终端线路通常会导致输出高电平下降,从而降低噪声免疫力;在驱动器输出端放置串联阻尼电阻可以减少负瞬变,但也会增加线路上的传播延迟,因为串联电阻会降低驱动设备的输出驱动能力。而二极管终端则没有这些缺点。

放置位置

二极管阵列在抑制负瞬变方面的最大效果出现在将其放置在传输线的末端和/或从主传输线分支出来的长支线的末端。此外,二极管还可用于减少由于线路中间不连续而产生的负瞬变,例如背板中为附加卡提供的插槽。

封装与订购信息

封装选项

| SN74F1056 有两种可订购的封装选项: | 可订购设备 | 状态 | 封装类型 | 封装图纸 | 引脚数 | 封装数量 | 环保计划 | 引脚镀层/球材料 | MSL 峰值温度 | 工作温度(°C) | 器件标记 | 样品 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SN74F1056D | 活跃 | SOIC | D | 16 | 40 | RoHS & Green | NIPDAU | Level - 1 - 260C - UNLIM | 0 至 70 | F1056 | ||

| SN74F1056DR | 活跃 | SOIC | D | 16 | 2500 | RoHS & Green | NIPDAU | Level - 1 - 260C - UNLIM | 0 至 70 | F1056 |

包装材料信息

不同封装的包装材料信息包括卷带和管装的尺寸等参数,具体可参考文档中的相关表格。

总结

SN74F1056 8 位肖特基势垒二极管总线终端阵列是一款功能强大的器件,能够有效降低总线反射噪声和抑制负瞬变。电子工程师在设计电子系统时,可以根据实际需求选择合适的封装和应用方式,以提高系统的稳定性和性能。在使用过程中,务必注意其绝对最大额定值和电气特性参数,确保器件的正常运行。你在实际设计中是否遇到过类似的总线噪声问题?你是如何解决的呢?欢迎在评论区分享你的经验。

-

肖特基势垒二极管

+关注

关注

0文章

42浏览量

9616

发布评论请先 登录

探索SN74S1053:16位肖特基势垒二极管总线终端阵列的卓越性能

SN74F1016:16位肖特基势垒二极管R - C总线终端阵列的特性与应用

肖特基势垒二极管的经典应用电路实例

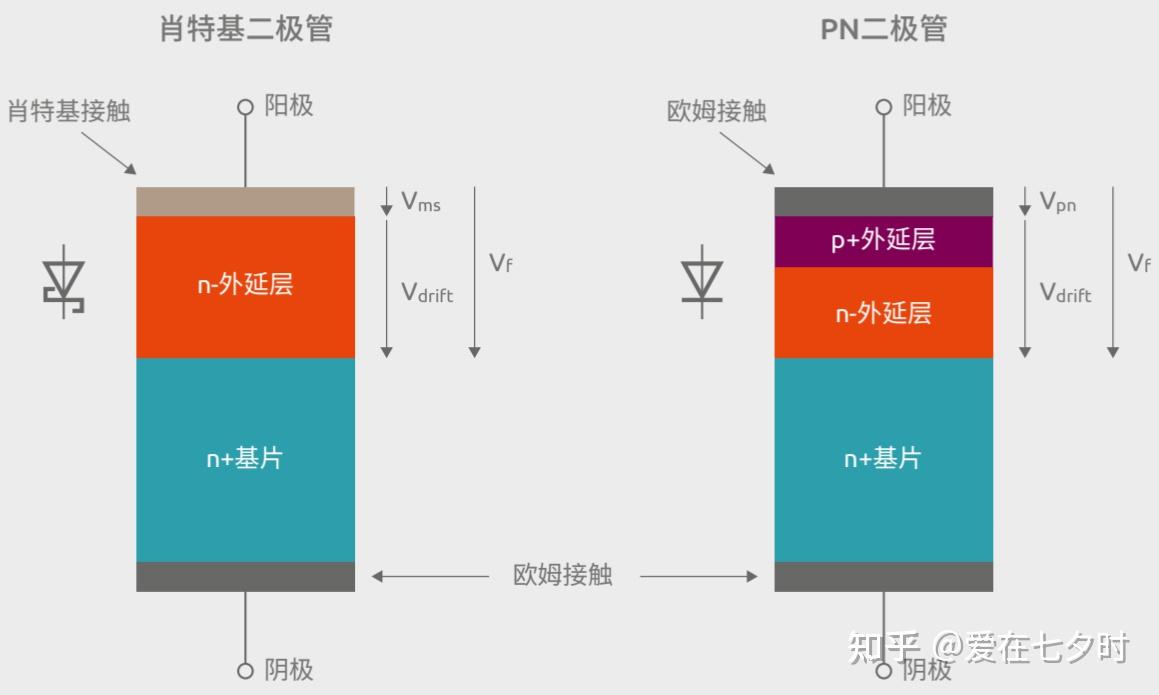

肖特基势垒二极管的金属半导体结解析

深入剖析SN74S1053:16位肖特基势垒二极管总线终端阵列

SN74S1053 16位肖特基势垒二极管总线终端阵列:解决反射噪声的理想方案

NSR30CM3:双共阴极肖特基势垒二极管的卓越特性与应用分析

NSR0170肖特基势垒二极管技术解析与应用指南

半导体“沟槽式MOS势垒肖特基二极管(TMBS)”的详解;

0201 表面贴装低势垒硅肖特基二极管反并联对 skyworksinc

表面贴装, 0201 低势垒硅肖特基二极管 skyworksinc

硅肖特基势垒二极管:封装、可键合芯片和光束引线 skyworksinc

SN74F1056 8位肖特基势垒二极管总线终端阵列:设计与应用解析

SN74F1056 8位肖特基势垒二极管总线终端阵列:设计与应用解析

评论