SN74F1016:16位肖特基势垒二极管R - C总线终端阵列的特性与应用

在高速数字电路设计中,总线信号的完整性至关重要,反射噪声、振铃以及负瞬变等问题可能导致设备的误操作。德州仪器(TI)的SN74F1016 16位肖特基势垒二极管R - C总线终端阵列,为解决这些问题提供了有效的解决方案。

文件下载:SN74F1016DWG4.pdf

产品概述

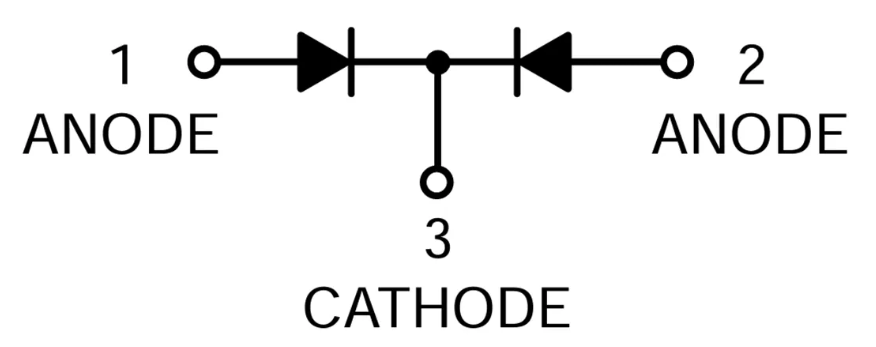

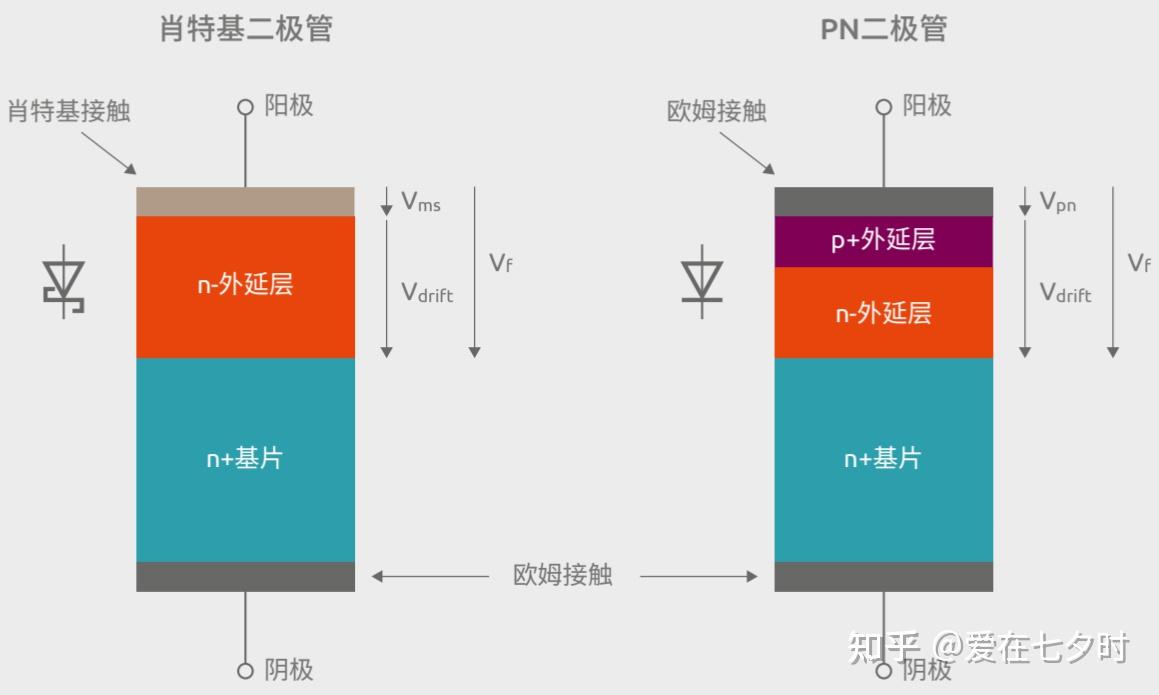

SN74F1016专为减少高性能总线上的反射噪声和振铃而设计。它采用16位R - C网络和肖特基势垒二极管阵列结构,适用于面向总线的系统。该器件的工作温度范围为0°C至70°C,其肖特基二极管具有接地钳位功能,可有效减少高速开关总线的过冲和下冲。

产品特性

电气特性

- 重复峰值正向电流:任何D端子相对于地的重复峰值正向电流可达300 mA(在 (t_{w} ≤100 mu s) ,占空比 (≤20 %) 条件下)。

- 电容与电压参数:总电容最大值为80 pF,电阻值为 (50 ±10%) ,电容值为 (47 pF±10%) ,反向电压 (V{R}=2.5 ~V{i}) ,工作频率 (f = 1MHz) 。

- 正向电压与内部串扰电流:单二极管工作时,典型值在 (T{A}=25^{circ} C) 条件下给出;多二极管工作时,内部串扰电流在特定条件下测量,其中一个二极管静态,其他二极管开关(开关二极管 (t{w}=100 mu s) ,占空比 (=20 %) ;静态二极管 (V_{R}=5 ~V) )。

开关特性

在 (T_{A}=25^{circ} C) 条件下,通过特定测试条件(如 (F = 10 mA) , (R(REC)= 100Ω) )测量其下冲特性,下冲电压在0.7 - 0.8 V之间。

应用优势

在实际应用中,内存设备(如DRAM、SRAM、EPROM等)的输入或许多时钟设备的时钟线上出现的大负瞬变可能导致设备误操作。SN74F1016二极管终端阵列有助于抑制由传输线反射、串扰和开关噪声引起的负瞬变。

与电阻终端方案相比,二极管终端具有明显优势。例如,分路电阻或戴维南等效终端会导致功耗大幅增加;使用单个接地电阻终端线路通常会导致输出高电平下降,降低噪声免疫力;在驱动器输出端放置串联阻尼电阻会减少负瞬变,但也会增加线路的传播延迟。而二极管终端则没有这些缺点。

应用建议

二极管阵列在抑制负瞬变方面的最大效果是将其放置在线路末端和/或从主传输线分支的长短截线末端。此外,它们还可用于减少线路中间不连续处产生的负瞬变,例如背板中为附加卡提供的插槽。

封装信息

SN74F1016有两种封装选项:SN74F1016DW和SN74F1016DWR,均为SOIC封装(DW),引脚数为20。SN74F1016DW每包数量为25,SN74F1016DWR每包数量为2000。它们均符合RoHS和绿色标准,引脚镀层为NIPDAU,湿度敏感度等级为Level - 1 - 260C - UNLIM,工作温度范围为0°C至70°C,器件标记为F1016。

总结

SN74F1016 16位肖特基势垒二极管R - C总线终端阵列凭借其独特的设计和优异的性能,为高速总线系统提供了有效的信号完整性解决方案。电子工程师在设计面向总线的系统时,可以考虑使用该器件来减少反射噪声和负瞬变,提高设备的可靠性和稳定性。你在实际设计中是否遇到过类似的信号完整性问题?你会选择使用SN74F1016来解决这些问题吗?

-

信号完整性

+关注

关注

68文章

1497浏览量

98237

发布评论请先 登录

SN74F1056 8位肖特基势垒二极管总线终端阵列:设计与应用解析

肖特基势垒二极管的经典应用电路实例

肖特基势垒二极管的金属半导体结解析

NSR30CM3:双共阴极肖特基势垒二极管的卓越特性与应用分析

半导体“沟槽式MOS势垒肖特基二极管(TMBS)”的详解;

0201 表面贴装低势垒硅肖特基二极管反并联对 skyworksinc

表面贴装, 0201 低势垒硅肖特基二极管 skyworksinc

硅肖特基势垒二极管:封装、可键合芯片和光束引线 skyworksinc

SN74F1016:16位肖特基势垒二极管R - C总线终端阵列的特性与应用

SN74F1016:16位肖特基势垒二极管R - C总线终端阵列的特性与应用

评论