AD9959:4 通道 500 MSPS DDS 芯片的详细解析

在电子设计领域,直接数字合成(DDS)技术凭借其频率分辨率高、切换速度快等优势,在众多应用中发挥着关键作用。今天,我们就来深入探讨一款高性能的 DDS 芯片——AD9959。

文件下载:AD9959.pdf

一、AD9959 概述

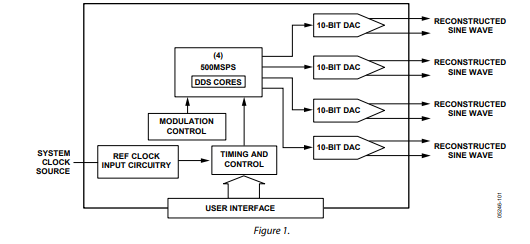

AD9959 是一款集成了四个直接数字合成器(DDS)核心的芯片,每个通道都能独立控制频率、相位和幅度。这种灵活性使得它能够有效校正由于模拟处理(如滤波、放大或 PCB 布局不匹配)导致的信号失衡问题。而且,所有通道共享一个系统时钟,这就保证了它们在本质上是同步的,同时该芯片还支持多个设备之间的同步。

二、芯片特性

2.1 高性能通道

- 同步与独立控制:具备 4 个同步的 DDS 通道,采样率高达 500 MSPS,各通道之间可独立进行频率、相位和幅度控制,频率/相位/幅度变化的延迟也相互匹配,通道间隔离度大于 65 dB,能有效减少通道间的干扰。

- 调制与扫描功能:支持高达 16 级的频率/相位/幅度调制(如 FSK、PSK、ASK),还具备线性频率/相位/幅度扫描能力,适用于雷达、仪器仪表等多种应用场景。

2.2 集成 DAC

芯片集成了 4 个 10 位的数模转换器(DAC),每个 DAC 的满量程电流可单独编程,分辨率为 10 位,能满足不同的输出需求。

2.3 高精度参数

- 频率分辨率:频率调谐分辨率可达 0.12 Hz 或更高,可实现精确的频率控制。

- 相位与幅度分辨率:拥有 14 位的相位偏移分辨率和 10 位的输出幅度缩放分辨率,为信号处理提供了更多的灵活性。

2.4 接口与供电

- SPI 接口:采用串行 I/O 端口(SPI),具有增强的数据吞吐量,还提供了多种配置选项,通过四个数据引脚(SDIO_0/SDIO_1/SDIO_2/SDIO_3)可实现四种可编程的串行 I/O 操作模式。

- 双电源供电:采用双电源供电,DDS 核心使用 1.8 V 电源,串行 I/O 接口使用 3.3 V 电源,满足不同部分的电压需求。

2.5 时钟与同步

- REFCLK 选项:REFCLK 输入源可直接驱动,也可与集成的 REFCLK 乘法器(PLL)配合使用,乘法因子可在 4 到 20 之间以整数步长进行编程,最大支持 500 MSPS。此外,REFCLK 输入还配备了振荡器电路,支持使用 20 MHz 到 30 MHz 的外部晶体作为时钟源。

- 多设备同步:支持多个 AD9959 设备的同步,方便构建复杂的系统。

2.6 封装与温度范围

芯片采用 56 引脚的 LFCSP 封装,节省空间。工作温度范围为 -40°C 到 +85°C,能适应工业环境的要求。

三、应用场景

3.1 信号源

可作为灵活的本地振荡器,为通信系统提供稳定的信号;也可作为 AOTF(声光可调滤波器)的 RF 源,满足其对信号精度和稳定性的要求。

3.2 雷达与声纳

在相控阵雷达和声纳系统中,其多通道同步和高精度的频率控制能力,可实现精确的波束形成和目标探测。

3.3 仪器仪表

为各类测试测量仪器提供精确的时钟信号和信号源,确保测量的准确性。

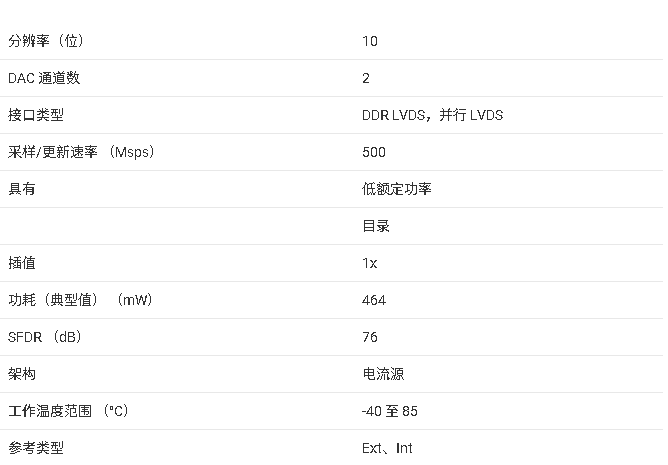

四、技术参数详细解读

4.1 参考时钟输入特性

参考时钟输入特性在不同模式下有不同的要求和范围,例如在 REFCLK 乘法器旁路时,频率范围为 1 - 500 MHz;启用乘法器时,频率范围为 10 - 125 MHz。内部 VCO 输出频率范围也会根据 VCO 增益控制位的设置而有所不同。同时,输入信号的电平、偏置电压、电容、占空比等参数也都有相应的规定,这些参数的合理设置对于芯片的正常工作至关重要。

4.2 DAC 输出特性

- 分辨率与电流:DAC 输出分辨率为 10 位,满量程输出电流范围为 1.25 - 10 mA,各通道间的输出幅度匹配误差在 -2.5% 到 +2.5% 之间,能保证输出信号的一致性。

- 线性度与隔离度:具有较好的线性度,差分非线性为 ±0.5 LSB,积分非线性为 ±1.0 LSB。通道间隔离度大于 65 dB,有效减少了通道间的串扰。

- 宽频与窄频 SFDR:在不同频率范围内,宽频和窄频的无杂散动态范围(SFDR)表现良好,能够满足大多数应用对信号纯净度的要求。

4.3 相位噪声特性

在不同输出频率和 REFCLK 乘法器设置下,芯片的残余相位噪声表现不同。例如,在 15.1 MHz 输出频率下,当 REFCLK 乘法器旁路时,在 1 kHz 偏移处的残余相位噪声为 -150 dBc/Hz;当 REFCLK 乘法器启用 5 倍时,在 1 kHz 偏移处的残余相位噪声为 -139 dBc/Hz。了解这些相位噪声特性,有助于在设计中评估信号的质量。

4.4 串行端口与杂项时序特性

- 串行端口:串行时钟(SCLK)的最大频率为 200 MHz,对 SCLK 脉冲宽度、数据设置时间、数据保持时间、CS 设置时间等都有严格的要求,这些参数决定了串行通信的稳定性和可靠性。

- 杂项时序:如 MASTER_RESET、I/O_UPDATE 等信号的最小脉冲宽度和设置保持时间也都有明确规定,确保芯片的正常时序操作。

4.5 电源与数据延迟

- 电源功耗:在不同工作模式下,芯片的总功耗有所不同,例如在所有通道开启的单音模式下,总功耗为 540 - 635 mW;在全功率关断模式下,总功耗仅为 13 mW。

- 数据延迟:在不同模式下,频率、相位和幅度数据从输入到 DAC 输出的延迟也不同,如在单音模式下,匹配延迟启用时,频率、相位和幅度字到 DAC 输出的延迟为 29 个系统时钟周期。

五、引脚配置与功能

AD9959 的引脚配置丰富,每个引脚都有其特定的功能。例如,SYNC_IN 和 SYNC_OUT 用于多个 AD9959 设备的同步;MASTER_RESET 为高电平有效复位引脚,可将内部寄存器恢复到默认状态;REF_CLK 为参考时钟输入引脚,可根据需要选择不同的时钟模式;I/O_UPDATE 用于将数据从串行 I/O 端口缓冲区传输到活动寄存器,其操作必须满足 SYNC_CLK 的设置和保持时间要求,以确保数据传输的稳定性。

六、典型性能特性

文档中给出了多个典型性能特性的图表,包括不同输出频率下的宽频 SFDR 和窄频 SFDR 曲线,以及不同输出频率和 REFCLK 乘法器设置下的残余相位噪声曲线。这些图表直观地展示了芯片在不同条件下的性能表现,为工程师在设计过程中评估芯片的适用性提供了重要参考。

七、总结与思考

AD9959 芯片凭借其高性能的通道控制、集成的 DAC、高精度的参数以及丰富的接口和同步功能,在众多应用领域具有广阔的应用前景。然而,在实际设计中,工程师需要充分考虑芯片的各项技术参数和引脚功能,合理设置时钟、电源等参数,以确保芯片能够发挥出最佳性能。同时,对于不同的应用场景,还需要根据具体需求对芯片进行优化和调整。例如,在对信号纯净度要求较高的应用中,如何进一步降低相位噪声和提高 SFDR 是需要思考的问题;在多设备同步的应用中,如何确保各设备之间的同步精度也是一个挑战。希望通过对 AD9959 的深入了解,能为广大电子工程师在相关设计中提供有价值的参考。

你在使用 AD9959 芯片的过程中遇到过哪些问题?又是如何解决的呢?欢迎在评论区分享你的经验和见解。

-

DDS芯片

+关注

关注

1文章

25浏览量

17519 -

电子设计

+关注

关注

42文章

2880浏览量

49916 -

AD9959

+关注

关注

4文章

9浏览量

14297

发布评论请先 登录

AD9958:高性能2通道DDS芯片的深度剖析

500 MSPS直接数字频率合成器AD9911:功能、特性与应用深度解析

AD9838:低功耗高性能DDS芯片的深度解析

MAX19517:高性能双通道10位130Msps ADC的深度解析

MAX19506:高性能双通道8位100Msps ADC的全面解析

低功耗4通道16位500kSPS PulSAR ADC AD7655技术解析

AD9484:高性能8位500 MSPS模数转换器的深度解析

AD9684:高性能14位500 MSPS双路模数转换器的深度解析

高性能16通道14位65 MSPS ADC——AD9249的深度解析

SGM31360:36 通道 LED 驱动芯片的详细解析

AD4854:高性能4通道同步采样20位1MSPS数据采集系统解析

STP4CMP:低电压4通道恒流LED驱动芯片的深度解析

德思特干货 | DDA技术深度解析系列(二):如何改变DDS设置?

DAC3154 双通道、10位、500MSPS数模转换器(DAC)技术手册

AD9959内置四通道10 bit DAC的500 MSPS直接数字频率合成器技术手册

AD9959:4 通道 500 MSPS DDS 芯片的详细解析

AD9959:4 通道 500 MSPS DDS 芯片的详细解析

评论