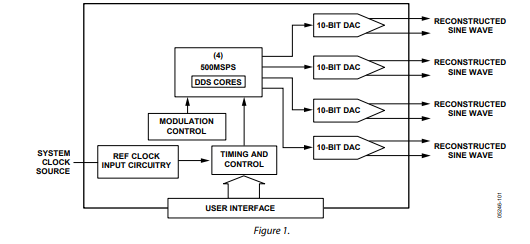

概述

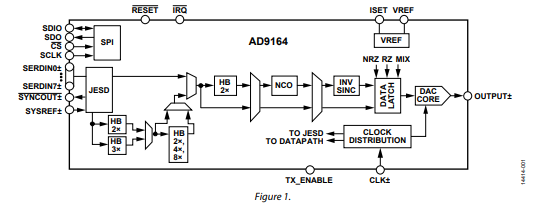

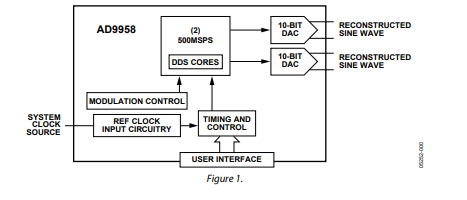

AD9959由四个直接数字频率合成器(DDS)内核构成,每个通道均可提供独立的频率、相位和幅度控制。这种灵活性可用于校正信号之间由滤波、放大等模拟处理或PCB布局失配而引起的不平衡问题。由于所有通道共享一个公共系统时钟,因此它们具有固有的同步性,支持多个设备的同步。

数据表:*附件:AD9959内置四通道10 bit DAC的500 MSPS直接数字频率合成器技术手册.pdf

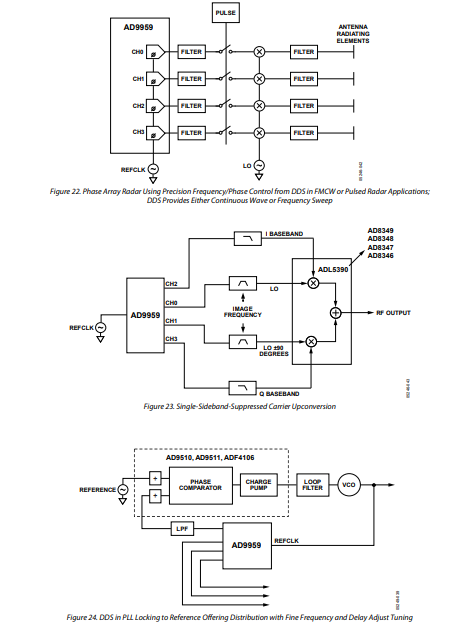

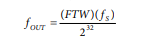

AD9959可以执行高达16阶的频率、相位或幅度调制(FSK、PSK、ASK)。通过将数据施加到模式引脚,可执行调制。此外,AD9959还支持线性频率、幅度或相位扫描,适合雷达、仪器仪表等应用。

AD9959的串行I/O端口可支持多种配置,提供了极大的灵活性。与ADI公司以往DDS产品中提供的SPI工作模式类似,串行I/O端口提供SPI兼容工作模式,。四个数据引脚(SDIO_0/ SDIO_1/SDIO_2/SDIO_3)对应串行I/O的四种可编程模式,从而提供了灵活性。

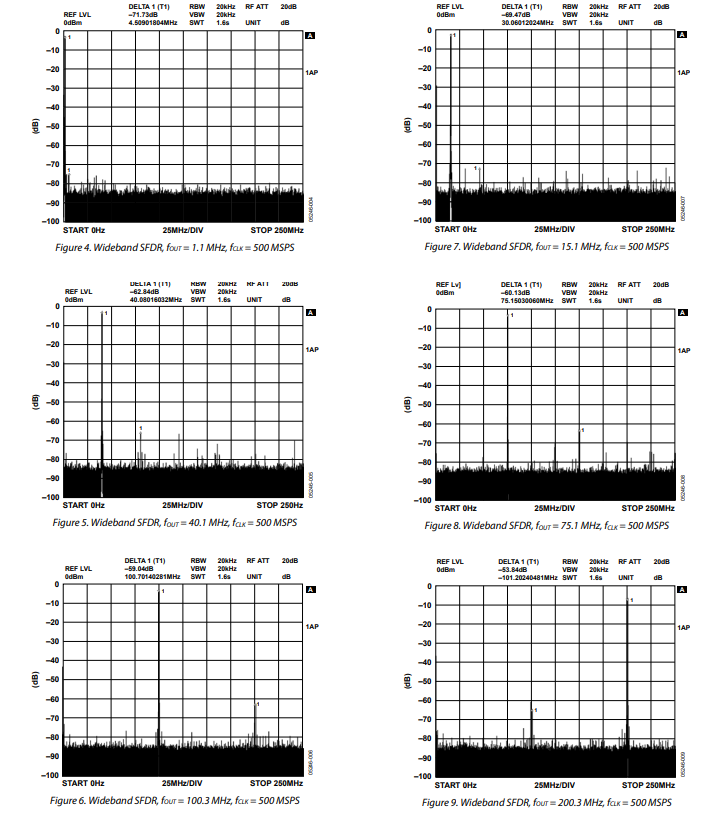

AD9959采用高级DDS技术,可在低功耗下提供高性能。这款器件集成了四个具有卓越宽带和窄带SFDR性能的高速10 bit DAC。每个通道均具有专用的32 bit频率调谐字、14 bit相位偏移和10 bit输出比例乘法器。

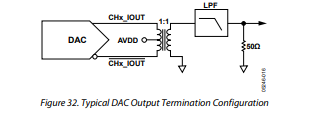

DAC输出以电源电压为参考源,必须经由电阻或AVDD中心抽头变压器连接到AVDD。每个DAC均具有各自的可编程基准源,用于实现每个通道不同的满量程电流。

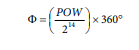

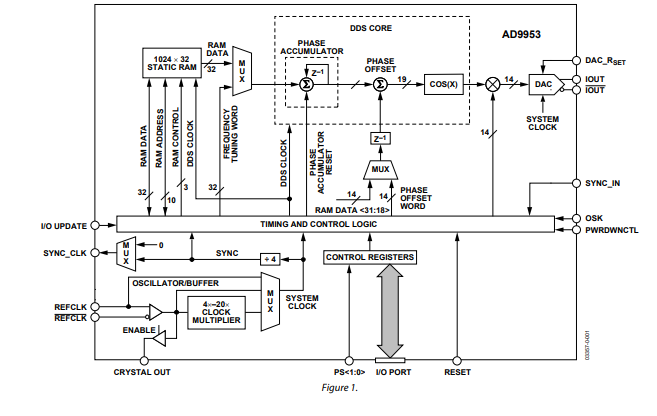

当使用REFCLK作为输入,并由DAC提供输出时,这款DDS可用作高分辨率分频器。所有通道共用REFCLK输入源,REFCLK输入源可被直接驱动,或与高达最大值500 MSPS的内置REFCLK乘法器(PLL)配合使用。PLL倍增因数的可编程范围为4~20,步进为整数。REFCLK输入还具有振荡电路,可将外部晶振用作REFCLK源。晶振的频率必须在20 MHz与30 MHz之间。晶振可与REFCLK乘法器配合使用。

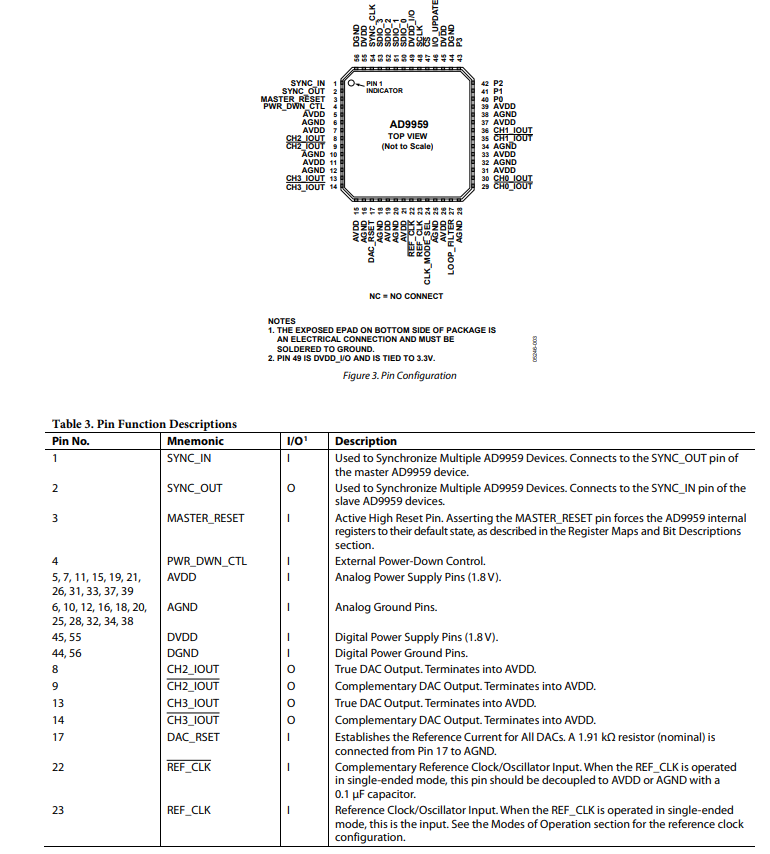

AD9959采用节省空间的56引脚LFCSP封装。DDS内核(AVDD和DVDD引脚)采用1.8 V电源供电。数字I/O接口(SPI)在3.3 V电压下工作,并需要将DVDD_I/O(引脚49)连接至3.3 V电压。

AD9959可在-40°C~+85°C的工业温度范围内工作。

应用

特性

- 4个同步DDS通道(500 MSPS)

- 通道间独立的频率/相位/幅度控制

- 频率/相位/幅度变化的延迟匹配

- 出色的通道间隔离(>65 dB)

- 线性频率/相位/幅度扫描功能

- 高达16级频率/相位/幅度调制(引脚可选)

- 4个集成式10位数模转换器(DAC)

- 单独可编程DAC满量程电流

- 频率调谐分辨率:0.12 Hz或以上

- 14位相位偏移分辨率

- 10位输出幅度调整分辨率

- 串行I/O端口接口(SPI)具有增强数据吞吐量

- 软件/硬件控制省电功能

- 双电源供电(1.8 V DDS内核/3.3 V串行I/O)

- 多器件同步

- 可选4×至20× REFCLK乘法器(PLL)

- 可选REFCLK晶体振荡器

- 56引脚LFCSP封装

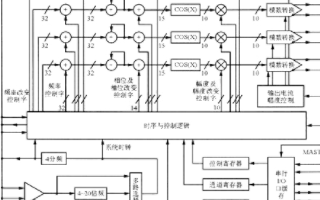

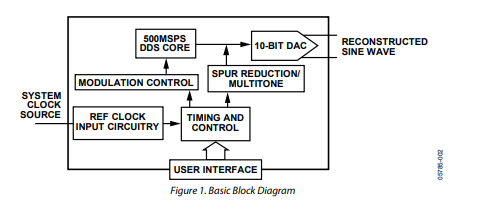

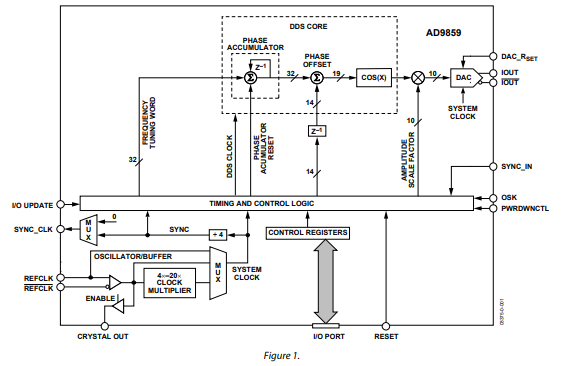

框图

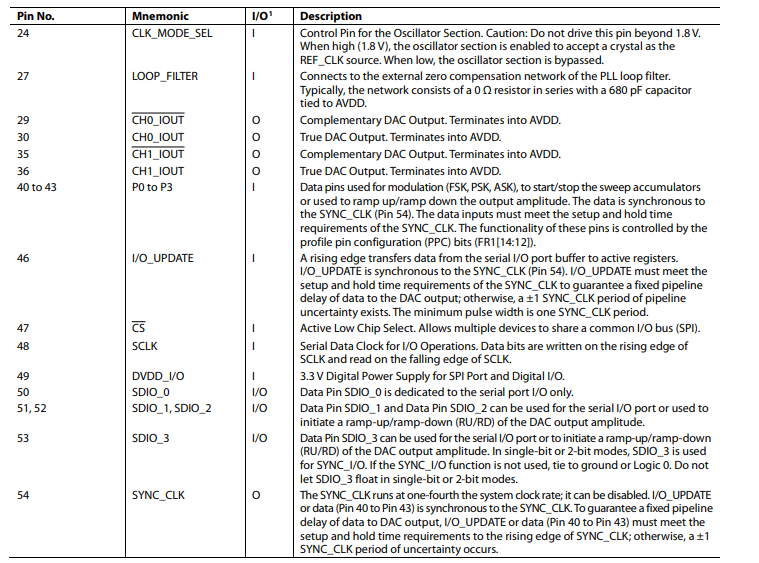

引脚配置描述

典型性能特征

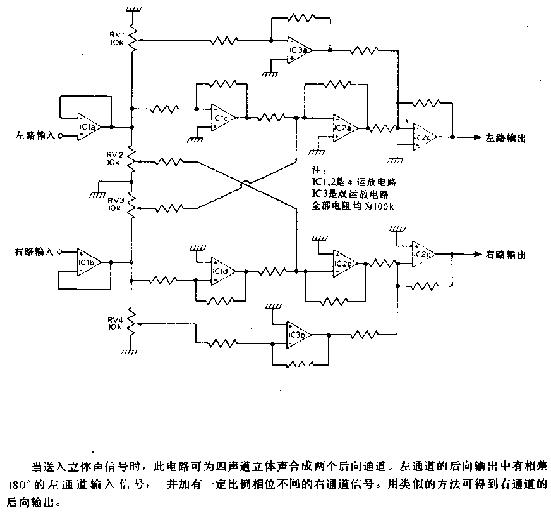

应用电路

直接数字频率合成器(DDS)内核

AD9959有四个DDS内核,每个内核由一个32位相位累加器和相位 - 幅度转换器组成。当相位累加器被时钟驱动且相位增量值(频率调谐字)大于0时,这些数字模块共同生成数字正弦波。相位 - 幅度转换器同时将相位信息转换为幅度信息,通过cos(θ)运算实现。

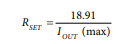

每个DDS通道的输出频率(fOUT)是每个相位累加器回滚速率的函数。确切关系由以下公式给出:

其中:

- ( f_S )是系统时钟速率。

- FTW是频率调谐字,且( 0 ≤ FTW ≤ 2^{31} )。

- ( 2^{32} )表示相位累加器容量。

由于四个通道共用一个系统时钟,它们本质上是同步的。

DDS内核架构还支持对输出信号进行相位偏移的功能,这通过通道相位偏移字(CPOW)实现。CPOW是一个14位寄存器,存储一个相位偏移值。该值会加到相位累加器的输出上,以偏移输出信号的当前相位。每个通道都有自己的通道相位偏移字寄存器。此功能可用于将所有通道置于已知相位关系中。相位偏移的确切值由以下公式给出:

数模转换器(DAC)

AD9959集成了四个10位电流输出DAC。DAC将数字码(幅度)转换为离散模拟量。DAC电流输出作为具有高输出阻抗(通常为100 kΩ )的电流源运行。与许多DAC不同,这些电流输出无需端接电阻或中心抽头变压器即可实现预期的电流流动。

每个DAC具有互补输出,可提供组合的满量程输出电流(( I_{OUT} + I_{overline{OUT}} ))。输出始终吸收电流,并且它们的总和在任何时间点都等于满量程电流。满量程电流通过外部电阻(( R_{SET} ))和可缩放的DAC电流控制位(在工作模式部分讨论)进行控制。电阻( R_{SET} )连接在DAC_RSET引脚与模拟地(AGND)之间。满量程电流与( R_{SET} )的阻值成反比,如下所示:

组合DAC输出的最大满量程输出电流为15 mA,但将输出限制为10 mA可提供最佳的无杂散动态范围(SFDR)性能。

DAC输出电压摆幅额定值为AVDD + 0.5 V至AVDD - 0.5 V。超出此范围的电压可能会导致过度谐波失真。应注意负载端接,使输出电压保持在合规范围内。超出此范围可能会潜在损坏DAC输出电路。

-

DDS

+关注

关注

22文章

683浏览量

156073 -

AD9959

+关注

关注

4文章

8浏览量

14094 -

数字频率合成器

+关注

关注

0文章

31浏览量

6641

发布评论请先 登录

GM4920:双通道800MSPS 14位直接数字频率合成器(DDS)

AD9164BBCZ 直接数字频率合成器

采用AD9914 3.5 GSPS直接数字频率合成器的AD9914/PCBZ评估板

AD9959 内置四通道10 bit DAC的500 MSPS直接数字频率合成器

四通道高速直接数字频率合成器AD9959的功能特点和应用

AD9164 16位、12 GSPS、RF DAC和直接数字频率合成器技术手册

AD9911 500 MSPS直接数字频率合成器,内置10位DAC技术手册

AD9958内置双通道10 bit DAC的500 MSPS直接数字频率合成器技术手册

AD9959内置四通道10 bit DAC的500 MSPS直接数字频率合成器技术手册

AD9959内置四通道10 bit DAC的500 MSPS直接数字频率合成器技术手册

评论