深度解析LMK00306:3 - GHz 6输出超低附加抖动差分时钟缓冲器

大家好,今天来深入解析一款高性能的时钟缓冲器——LMK00306。在高速电子设计中,稳定且低抖动的时钟信号是系统可靠运行的关键,而LMK00306在这方面表现出色,下面将详细介绍它的特点、性能及应用要点。

文件下载:lmk00306.pdf

1. 产品概述

LMK00306是一款3 - GHz、6输出的差分扇出缓冲器,专为高频、低抖动的时钟/数据分配和电平转换而设计。它能够从两个通用输入或一个晶体输入中选择输入时钟,并将其分配到两组3差分输出和一个LVCMOS输出。该产品采用3.3 V核心电源和3个独立的3.3 V/2.5 V输出电源,具有高性能、多功能和高能效的特点。

2. 核心特性

输入特性

- 3:1输入复用器:拥有两个通用输入,可接受LVPECL、LVDS、CML、SSTL、HSTL、HCSL或单端时钟,工作频率最高可达3.1 GHz;还有一个晶体输入,可接受10 - 40 MHz的晶体或单端时钟。这种丰富的输入接口,使得它在不同的时钟源选择上具有很大的灵活性。在实际设计中,大家是否会根据不同的应用场景优先选择不同类型的输入呢?

- 输入时钟选择:通过CLKin_SEL[1:0]输入控制,可以方便地在不同输入源之间切换。当选择CLKin0或CLKin1时,晶体电路会自动断电;选择OSCin时,晶体振荡器电路启动并将时钟分配到所有输出。

输出特性

- 双输出组:有两个输出组,每组各有3个差分输出,输出类型可独立配置为LVPECL、LVDS、HCSL或Hi - Z。对于LVPECL输出,在156.25 MHz时钟源下,10 kHz - 1 MHz频段的附加抖动低至20 fs RMS,12 kHz - 20 MHz频段的附加抖动为51 fs RMS。如此低的抖动,对于对时钟精度要求极高的应用来说是非常关键的。

- LVCMOS输出:REFout提供一个LVCMOS参考输出,可通过REFout_EN引脚控制其启用或禁用。该输出的同步启用输入功能可确保在启用或禁用时无窄脉冲输出,提高了时钟信号的稳定性。

电源与配置特性

- 电源供应:采用3.3 V核心电源(VCC)和3个独立的3.3 V/2.5 V输出电源(VCCOA、VCCOB、VCCOC),输出电源工作在2.5 V时可降低功耗,同时与2.5 V接收器设备兼容。

- 引脚控制配置:输入选择和输出缓冲器模式通过引脚绑定进行控制,这种方式使得设计更加简单直观,便于工程师进行配置。

其他特性

- 高PSRR:在156.25 MHz时,LVPECL/LVDS的电源抑制比(PSRR)可达 - 65 / - 76 dBc,能够有效抑制电源纹波对时钟输出的影响。

- 宽温度范围:工业温度范围为 - 40°C 到 + 85°C,适用于各种恶劣的工业环境。

- 小型封装:采用36引脚的WQFN(6 mm × 6 mm)封装,节省了电路板空间。

3. 关键参数与性能表现

绝对最大额定值与推荐工作条件

了解器件的绝对最大额定值和推荐工作条件对于保证器件的正常运行至关重要。LMK00306的结温最大为 + 150°C,推荐环境温度范围为 - 40°C 到 + 85°C,核心电源电压范围为3.15 V - 3.45 V,输出电源电压范围为3.3 V ± 5% 或2.5 V ± 5%,且Vcco应小于或等于Vcc。

电气特性

- 电流消耗:不同的输出类型和配置下,核心电源电流和输出电源电流有所不同。例如,当所有输出禁用时,核心电源电流(ICC_CORE)在CLKinX选择时最大为8.5 mA,OSCin选择时最大为13.5 mA。在实际应用中,需要根据具体的输出配置来准确计算电流消耗,以评估电源设计是否合理。

- 功率供应纹波抑制:通过PSRR测试可以看出,该器件在不同的时钟频率和纹波条件下,对电源纹波具有良好的抑制能力。例如,在156.25 MHz时钟频率下,LVDS输出的纹波诱导相噪抑制比可达 - 76 dBc。

- 时钟输入与输出特性:输入频率范围可达DC - 3.1 GHz,不同输出类型的最大输出频率和抖动特性也各有不同。如LVPECL输出在全VOD摆幅(VOD ≥ 600 mV)、Vcco = 3.3 V ± 5%、RT = 160 Ω 到GND的条件下,最大输出频率为1.0 - 1.2 GHz。

典型特性

文档中给出了一系列典型特性曲线,如LVPECL和LVDS输出摆幅与频率的关系、噪声地板与输入摆率的关系、RMS抖动与输入摆率的关系等。从这些曲线中可以直观地看出器件在不同工作条件下的性能变化。例如,噪声地板会随着输入摆率的降低而恶化,因此在设计中应尽量保证输入具有较高的摆率(3 V/ns 或更高),以获得更好的相位噪声和抖动性能。那么,在实际操作中,大家是如何确保输入摆率满足要求的呢?

4. 应用与实现要点

驱动时钟输入

- 信号类型与条件:LMK00306的两个通用输入可以接受多种类型的信号,包括AC或DC耦合的3.3V/2.5V LVPECL、LVDS、CML、SSTL等。为了获得最佳的相位噪声和抖动性能,输入应具有3 V/ns(差分)或更高的高摆率。

- 单端输入处理:虽然推荐使用差分信号输入,但在符合单端输入规格的情况下,也可以使用单端时钟输入。对于大的单端输入信号,如3.3V或2.5V LVCMOS,应在输入附近放置50 Ω负载电阻进行信号衰减和线路端接,以防止输入过驱动和减少反射。同时,单端输入摆率应尽可能高,以减少性能下降。

晶体接口

- 晶体选择与参数计算:该器件支持基模、AT切割晶体,负载电容(CL)通常在18 - 20 pF之间。在实际设计中,需要根据晶体的参数和OSCin输入电容(典型值为4 pF)以及PCB杂散电容来计算离散负载电容C1和C2的值,以确保晶体振荡器能够正常启动。

- 晶体驱动水平控制:要注意晶体的功率消耗不能超过制造商规定的最大驱动水平,否则可能导致晶体过早老化、频率偏移甚至最终失效。可以通过调整外部电阻RLIM来限制晶体的驱动水平,建议的起始值为1.5 kΩ。

终端和时钟驱动器的使用

- 差分操作的终端:在直流耦合的差分操作中,LVDS驱动器应使用100 Ω终端电阻靠近接收器,HCSL驱动器应使用50 Ω终端电阻接地,LVPECL驱动器应使用50 Ω终端电阻连接到Vcco - 2 V。在交流耦合的差分操作中,需要注意为驱动器和接收器建立合适的直流偏置点。

- 单端操作的转换:可以使用巴伦将LVDS或LVPECL驱动器的平衡差分信号转换为不平衡单端信号。在使用LVPECL驱动器进行单端操作时,要注意对未使用的驱动器进行适当的终端处理。

5. 电源供应建议

电源顺序

当从单独的电源轨为Vcc和Vcco引脚供电时,建议在电源上升时同时达到调节点,或在下降时同时达到地电位。这样可以防止在Vcc先于Vcco供电时,Vcc到Vcco引脚出现内部电流流动。

电流消耗与功耗计算

根据电气特性中规定的电流消耗值,可以计算出任何设备配置下的总功耗和IC功耗。在计算过程中,需要考虑不同输出类型和负载条件下的电流消耗,以及外部终端电阻和LVPECL终端电压的功耗。通过合理的电源设计和功耗计算,可以确保器件在正常工作的同时,避免因过热而影响性能。

电源旁路

为了减少电源噪声,Vcc和Vcco电源应在每个电源引脚附近放置高频旁路电容(如0.1 uF或0.01 uF),并在设备附近的电源和接地层之间放置1 uF - 10 uF的去耦电容。所有旁路和去耦电容应通过短走线或过孔与电源和接地层短连接,以最小化串联电感。

电源纹波抑制

电源纹波会对时钟输出产生影响,LMK00306通过测量单端边带相位噪声来评估其电源纹波抑制能力(PSRR)。从测试结果来看,该器件在不同的时钟频率和纹波条件下表现出良好的PSRR特性。在实际应用中,可以通过增加电源滤波和旁路电容来进一步降低电源纹波的影响。

6. 热管理

由于LMK00306的功率消耗可能较高,需要注意热管理。为了保证器件的可靠性和性能,芯片温度应限制在最高125°C。可以通过在PCB上设计散热焊盘和多个过孔连接到接地层,以及在PCB另一侧设置铜面积较大的散热区域来提高散热效率。

7. 总结

LMK00306是一款功能强大、性能优异的时钟缓冲器,具有丰富的输入输出接口、低抖动、高PSRR等特点。在设计过程中,需要充分考虑其输入输出特性、电源供应、热管理等方面的要求,以确保器件能够在各种应用场景下稳定可靠地工作。希望通过本文的介绍,能够帮助大家更好地理解和应用这款器件。大家在使用LMK00306或其他类似器件时,遇到过哪些问题呢?欢迎在评论区交流分享。

-

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

低抖动

+关注

关注

0文章

76浏览量

6124

发布评论请先 登录

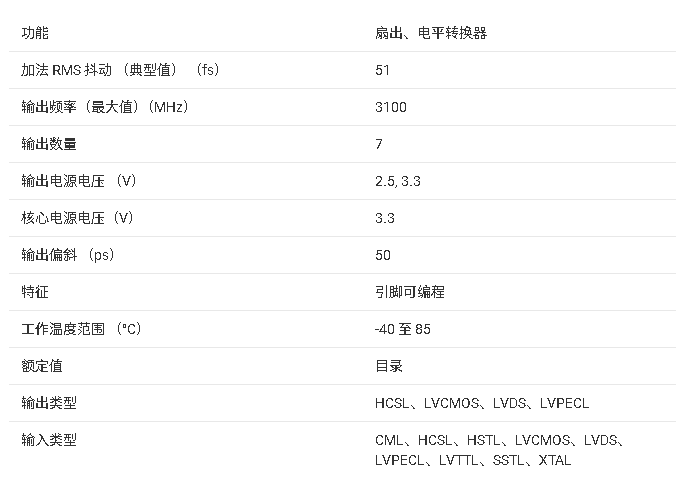

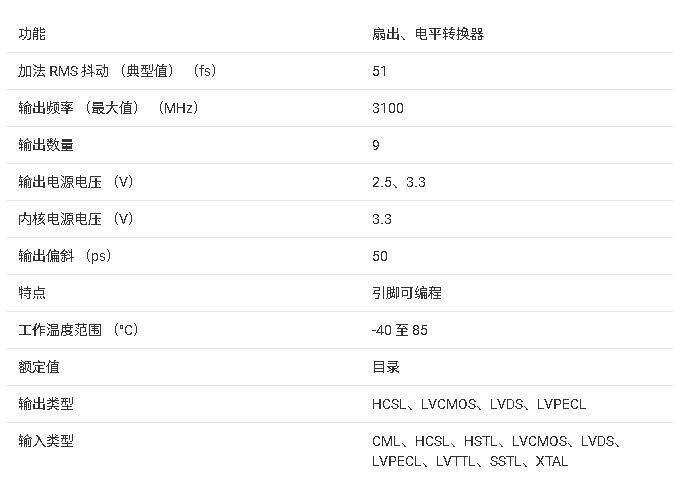

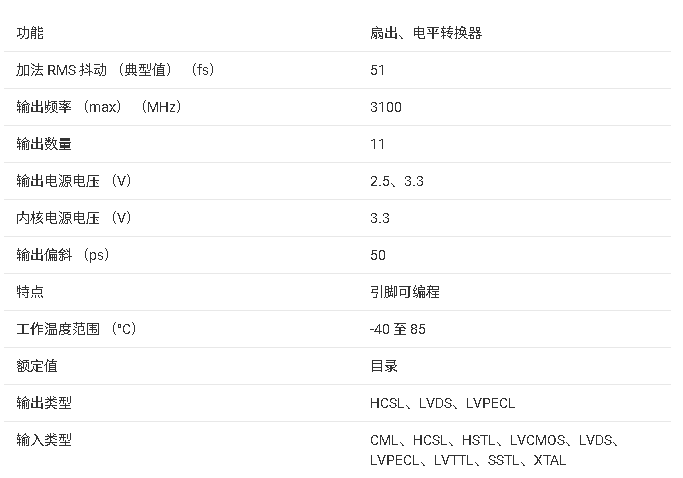

LMK00301 3GHz 10路输出超低附加抖动差动时钟缓冲器和电平转换器数据表

LMK00304 3GHz 4路输出超低附加抖动差动时钟缓冲器/电平转换器数据表

深度解析LMK00306:3 - GHz 6输出超低附加抖动差分时钟缓冲器

深度解析LMK00306:3 - GHz 6输出超低附加抖动差分时钟缓冲器

评论