MAX5062/MAX5063/MAX5064:125V/2A高速半桥MOSFET驱动器深度解析

在电子工程领域,MOSFET驱动器的性能对于电源转换和电机控制等应用至关重要。今天,我们就来详细探讨一下MAXIM公司的MAX5062/MAX5063/MAX5064这三款125V/2A高速半桥MOSFET驱动器。

文件下载:MAX5063.pdf

一、产品概述

MAX5062/MAX5063/MAX5064是为高压应用设计的高频、125V半桥n沟道MOSFET驱动器,能够独立控制高端和低端MOSFET。其输入到输出的典型传播延迟为35ns,且驱动器之间的传播延迟匹配在3ns(典型值)以内。这种低且匹配的传播延迟,加上高源/灌电流能力和热增强封装,使这些器件非常适合用于高功率、高频的电信电源转换器。125V的最大输入电压范围,为电信标准中100V的输入瞬态要求提供了充足的余量。此外,片上可靠的自举二极管连接在VDD和BST之间,无需外部离散二极管。

二、产品特性亮点

2.1 高电压与宽电压范围

-

高达125V的输入操作能力,8V至12.6V的VDD输入电压范围,能适应多种复杂的电源环境。

2.2 强大的驱动能力

-

2A的峰值源和灌电流驱动能力,可快速驱动MOSFET,提高开关速度。

2.3 低延迟与匹配性

-

典型35ns的传播延迟,且驱动器之间保证8ns的传播延迟匹配,确保高端和低端MOSFET的同步性。

2.4 可编程功能

-

MAX5064具有可编程的先断后通(BBM)时序,可在16ns至95ns之间进行编程,有效避免直通电流。

2.5 高频性能

-

MAX5064在驱动100nC栅极电荷时,组合开关频率可达1MHz。

2.6 多种逻辑输入类型

-

提供CMOS(VDD / 2)或TTL逻辑电平输入,并带有迟滞功能,适应不同的控制信号。

2.7 低功耗与小尺寸

- 低200µA的电源电流,且有8引脚SO、热增强SO和12引脚薄QFN等多种封装可供选择。

三、应用场景广泛

3.1 电信电源领域

-

适用于电信半桥电源、全桥转换器、有源钳位正激转换器等,其高电压、低延迟和高驱动能力能够满足电信设备对电源稳定性和高效性的要求。

3.2 电力转换领域

-

可用于双开关正激转换器和电源模块,提高电源转换效率,减少能量损耗。

3.3 电机控制领域

- 能够快速准确地控制电机的开关,实现电机的高效运行。

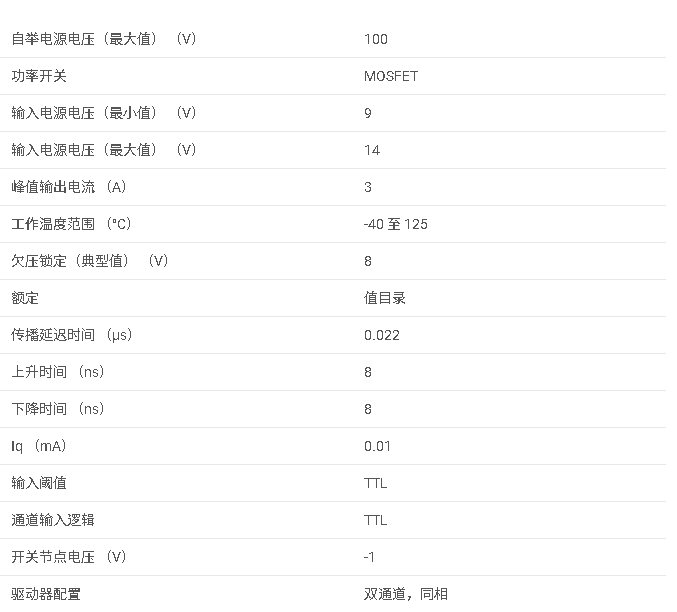

四、电气特性详解

4.1 电源供应特性

- 工作电压范围:其工作电源电压范围为 8V 至 12.6V,能适应多种电源环境。不过要注意,VDD 到地或 BST 到 HS 的电压不能超过 13.2V,否则可能损坏器件。

- 静态和工作电流:不同型号在静态(无开关动作)和工作(500kHz 开关频率、VDD = +12V 等条件下)时的电源电流有所差异。例如,MAX5062/MAX5063 的 VDD 静态电流典型值为 70µA,最大值 140µA;而 MAX5064_ 的 VDD 静态电流典型值为 120µA,最大值 260µA。工作电流方面,当开关频率为 500kHz、VDD = +12V 时,VDD 和 BST 的工作电流最大值均为 3mA。

- 欠压锁定(UVLO):高低侧驱动器都具备欠压锁定功能。低侧驱动器的 UVLO_LOW 阈值以地为参考,当 VDD 低于 6.8V 时,两个驱动器输出拉低;高侧驱动器有自己的 UVLO_HIGH 阈值,以 HS 为参考,当 BST 相对于 HS 低于 6.4V 时,DH 拉低。UVLO 典型滞回值为 0.5V。这一特性在实际应用中能有效防止设备在低电压下不稳定工作,提高了系统的可靠性。但在选择外部电容时要谨慎,比如选择约为 MOSFET 总栅极电容 20 倍的电容,避免 DH 输出在开关时出现意外振荡。

4.2 逻辑输入特性

- 输入逻辑电平:MAX5062/MAX5064A 采用 CMOS (VDD / 2) 逻辑输入,而 MAX5063/MAX5064B 具有 TTL 兼容逻辑输入。逻辑输入信号独立于 VDD,可承受最高 15V 的电压尖峰,能适配不同的逻辑信号源,为设计带来了很大的灵活性。

- 输入滞后:TTL 和 CMOS 逻辑输入分别具有 400mV 和 1.6V 的滞后,能够有效避免信号转换过程中的双脉冲问题,提高了系统的抗干扰能力。

- 输入阻抗和电容:逻辑输入为高阻抗引脚,输入电容低至 2.5pF,减少了负载,提高了开关速度。同时非反相输入通过 1MΩ 电阻内部下拉至地,反相输入通过 1MΩ 电阻内部上拉至 VDD,避免输入引脚浮空导致的不稳定。

4.3 驱动器输出特性

- 输出电阻:高低侧驱动器输出级采用低 RDS_ON 的 p 通道和 n 通道器件(图腾柱结构),在不同温度和负载条件下,输出电阻有所不同。例如,当 VDD = 12V、驱动 100mA 电流时,在 +25°C 和 +125°C 下,高侧驱动器的源极输出电阻 RON_HP 分别典型为 2.5Ω 和 3.3Ω,漏极输出电阻 RON_HN 分别典型为 2.1Ω 和 2.8Ω;低侧驱动器类似。较低的输出电阻意味着更高的源极和漏极电流以及更快的开关速度。

- 峰值输出电流:典型峰值源极和漏极电流为 2A,能够为 MOSFET 提供足够的驱动能力,确保 MOSFET 快速开关。

- 击穿前导通逻辑:内部 p 通道和 n 通道 MOSFET 具有 1ns 的击穿前导通逻辑,避免了它们之间的交叉导通,减少了直通电流,降低了工作电源电流以及 VDD 上的尖峰,提高了系统效率和稳定性。

4.4 内部自举二极管特性

- 内部二极管连接在 VDD 和 BST 之间,与外部连接在 BST 和 HS 之间的自举电容配合使用。当 DL 低侧开关导通时,二极管从 VDD 为电容充电;当高侧驱动器导通,HS 被拉高时,二极管隔离 VDD。其典型正向压降为 0.9V,典型关断/导通时间为 10ns。若需要更低的 VDD 到 BST 压降,可以在 VDD 和 BST 之间连接外部肖特基二极管。

4.5 开关特性

- 上升和下降时间:在不同负载电容下,驱动器的上升和下降时间不同。例如,当负载电容 CL = 1000pF 时,上升和下降时间典型值约为 7ns;当 CL = 5000pF 时,变为约 33ns;CL = 10000pF 时,约为 65ns。

- 导通和关断传播延迟时间:对于 CMOS 和 TTL 输入类型,在 CL = 1000pF 条件下,导通和关断传播延迟时间不同。CMOS 输入时典型为 30ns,最大值 55ns;TTL 输入时典型为 35ns,最大值 63ns。并且驱动器之间的延迟匹配在 8ns 以内,确保了高低侧驱动器的同步性。

- 击穿前导通时间调整(仅 MAX5064):该功能可将高低侧开关之间的延迟(击穿前导通时间 tBBM)从 16ns 调整到 95ns,通过连接 10kΩ 到 100kΩ 的电阻到 BBM 引脚实现。计算公式为 (t{BBM}=8 ns times(1 + R{BBM} / 10 kΩ)),延迟匹配误差计算公式为 (t_{BBMERROR } = 0.15 × t{BBM}+t{MATCH }) ,其中 (t{MATCH }) 为传播延迟匹配。这一功能有效避免了半桥和同步降压拓扑中高低侧开关同时导通产生的直通电流问题,但在低 tBBM 值时,由于 BBM 模块中固定比较器延迟的存在,会有较高的百分比误差。

4.6 最小脉冲宽度

- 采用单触发电平转换器架构来实现低传播延迟,但会导致输出端出现最小(高或低)脉冲宽度。为避免在低占空比窄脉冲时无外部 BBM 延迟情况下出现直通,DH 最小高脉冲宽度要低于 DL 最小低脉冲宽度;在高占空比(接近 100%)时,DH 最小低脉冲宽度必须高于 DL 最小低脉冲宽度以避免重叠和直通。在没有外部 BBM 延迟的情况下,MAX5062/MAX5063/MAX5064 可能会有大约 40ns 的重叠,因此建议在 INH 路径中添加外部延迟,确保 INH 处看到的最小低脉冲宽度始终长于 tPW - MIN 。

五、设计注意事项

5.1 电源旁路和接地

-

电源旁路和接地处理不当,会导致电源下降和接地偏移,影响驱动器的延迟和过渡时间,甚至干扰其他共享交流接地回路的电路。因此,要在尽可能靠近器件的位置并联一个或多个 0.1µF 陶瓷电容,将 VDD 旁路到地(MAX5062/MAX5063)或 PGND(MAX5064),并使用接地平面来减小接地回路电阻和串联电感。同时,将外部 MOSFET 尽可能靠近 MAX5062/MAX5063/MAX5064 放置,以进一步减小电路板电感和交流路径电阻。

5.2 功率耗散

-

器件的功率耗散主要来自内部升压二极管、nMOS 和 pMOS FET 的功率损耗。对于电容性负载,总功率耗散计算公式为 (P{D}=(C{L} × V{D D}^{2} × f{S W})+(I{D D O}+I{B S T O}) × V{D D}) ,使用内部升压二极管时的功耗与使用外部肖特基二极管时不同。在实际应用中,要根据不同的封装规格,将总功耗控制在最大允许值以下,例如 12 引脚 TQFN 封装在 (T{A}=+70^{circ}C) 环境下最大允许功耗为 1.951W。

5.3 电路板布局

- 由于驱动器在开关 MOSFET 栅极处产生大电流以形成快速上升和下降沿,高 di/dt 效应会导致严重的振铃问题。因此在设计 PCB 时,要确保 VDD 电压(相对于地)或 BST 电压(相对于 HS)不超过 13.2V,在 VDD 到地(MAX5062/MAX5063)或 PGND(MAX5064)以及 BST 到 HS 之间尽可能靠近器件放置一个或多个低 ESL 的 0.1µF 去耦陶瓷电容,且电容值至少为所驱动栅极电容的 20 倍。同时,要注意减小器件与驱动的 MOSFET 栅极之间的交流电流回路的物理距离和阻抗,并将 TQFN(MAX5064)或 SO(MAX5062C/D 和 MAX5063C/D)封装的外露焊盘焊接到大面积铜平面上,以实现额定功率耗散。

综上所述,MAX5062/MAX5063/MAX5064 系列高速半桥 MOSFET 驱动器凭借其出色的性能和广泛的应用场景,为电子工程师在设计各类电源和电机控制电路时提供了强大的工具。但在实际应用中,工程师需要深入理解其各项特性和设计注意事项,才能充分发挥其优势,设计出高效、稳定的电路系统。你在使用这些驱动器的过程中遇到过哪些挑战呢?欢迎在评论区分享。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MOSFET驱动器

+关注

关注

4文章

221浏览量

26836 -

电气特性

+关注

关注

0文章

324浏览量

10312

发布评论请先 登录

相关推荐

热点推荐

探索MAX5062:高性能半桥MOSFET驱动器的卓越之选

组件,其性能直接影响着整个系统的效率、稳定性和可靠性。今天,我们将深入探讨MAXIM推出的MAX5062/MAX5063/MAX5064系列125V/

MAX20050:2A同步降压LED驱动器的全面解析

MAX20050–MAX20053:2A同步降压LED驱动器的全面解析 在汽车外部照明等领域,高亮度LED

UCC27211A:高性能半桥驱动器的深度解析与应用指南

UCC27211A:高性能半桥驱动器的深度解析与应用指南 在电子工程师的日常工作中,选择合适的

深度解析UCC27301A:高性能半桥驱动器的理想之选

深度解析UCC27301A:高性能半桥驱动器的理想之选 在电子工程师的日常工作中,选择合适的器件

汽车级高速半桥栅极驱动器 UCC2773x-Q1:设计与应用解析

汽车级高速半桥栅极驱动器 UCC2773x-Q1:设计与应用解析 在电子工程领域,高速、高效且可

LM25101 具有 8V UVLO 和 TTL 输入的 3A、2A 或 1A 半桥栅极驱动器数据手册

LM25101 高压栅极驱动器设计用于驱动高压侧和 采用同步降压或半桥配置的低侧 N 沟道 MOSFET。

MAX5063:125V/2A高速半桥MOSFET驱动器深度解析

MAX5063:125V/2A高速半桥MOSFET驱动器深度解析

评论