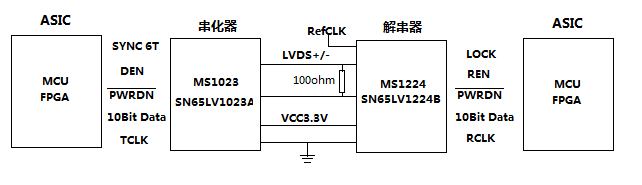

SN65LV1023A、SN65LV1224B为TI公司推出的基于BLVDS技术的串化与解串器,替代已经停产的DS90LV1023E、DS90LV1224E套片。

MS1023与MS1224是瑞盟公司基于BLVDS SerDes技术推出的并串/串并转换器,MS1023能够Pin to Pin替代DS90LV1023E、SN65LV1023A,MS1224 Pin to Pin替代DS90LV1224E、SN65LV1224B!但有关MS1023、MS1224应用文章稀缺,瑞盟未提供“用户应用手册”,今天就MS1023、MS1224应用做简单分享,欢迎开发及应用工程师积极交流。

MS1023 串化器和 MS1224解串器是一对 10bit并串/串并转换芯片,用于在 LVDS差分底板上传输和接收10MHz-80MHz的并行速率的串行数据。起始/停止位加载后,转换为负载编码输出,串行数据速率120Mbps-960Mbps。上电时,这一对芯片可通过内部产生的 SYNC样本信号同步模式进行初始化或者解串器与随机数据同步。通过使用同步模式,解串器可在特定的、更短的时间参数内建立锁定。

关于SYNC同步:

快速同步模式:SYNC样本信号传输与否由串化器的SYNC1和SYNC2输入决定。在SYNC1或SYNC2保持高电平至少6T(T=1个Refclk周期)后,SYNC模式在串行线上生成1026T。在这个1026周期的SYNC模式传输期间,不需要SYNC1或SYNC2保持高电平。

当连续收到有效的SYNC1或SYNC2脉冲(时间宽度超过6个时钟周期),SYNC样本信号将会发送由6个1和6个0组成特定的SYNC样本信号。当MS1224解串器在LVDS输入上检测到边沿传输, PLL锁定来自串化器的SYNC样本信号,此时LOCK由高转为低电平,解串器输出开始恢复输入的LVDS数据。

随机同步模式:MS1224可以工作在开环应用中,且支持热插拔。在开环应用中,MS1224解串器可从数据流中获取时钟,而不需要串化器发送特定的同步模式信号。MS1224解串器在LVDS输入上检测到边沿传输,将尝试锁定到内嵌的时钟信息, 当PLL锁定输入的内嵌的时钟,LOCK由高转为低电平,解串器输出开始恢复输入的LVDS数据。

MS1224在开环或热插拔情况下,数据流在本质上是随机的,由于锁定时间根据数据流特征而变化,所以准确时间是不可能预知的。当MS1224启动随机锁定,受RMT重复性多级传输影响,解串器会检测到潜在的错误时钟,而延长随机锁定时间。在随机同步模式下,PLL锁定前,LOCK输出为高电平,ROUT(0:9)、RCLK为高阻态。

总结:

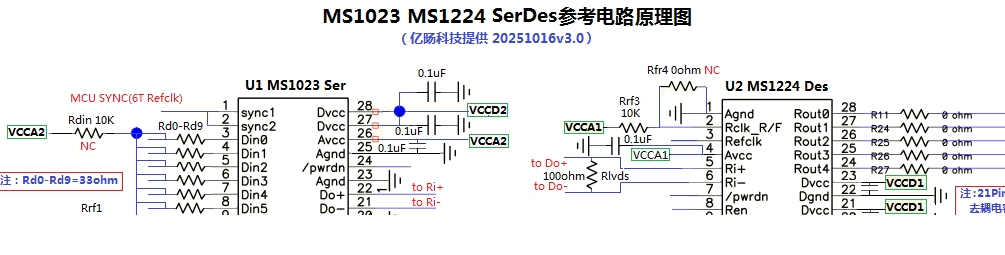

⑴、不管是快速同步模式或是随机同步模式,用户系统最好监控MS1224 LOCK状态,以防MS1224失锁。当检测到“失锁”,如果在特定的时间内无法复位锁定,系统可重新发送SYNC同步样本信号。因此,最好将解串器 LOCK输出直接连接到SYNC1、SYNC2。

⑵、将SYNC1、SYNC2短接后连接到MCU/FPGA 输出的SYNC同步触发电路,输出的SYNC同步高电平触发保持6T。

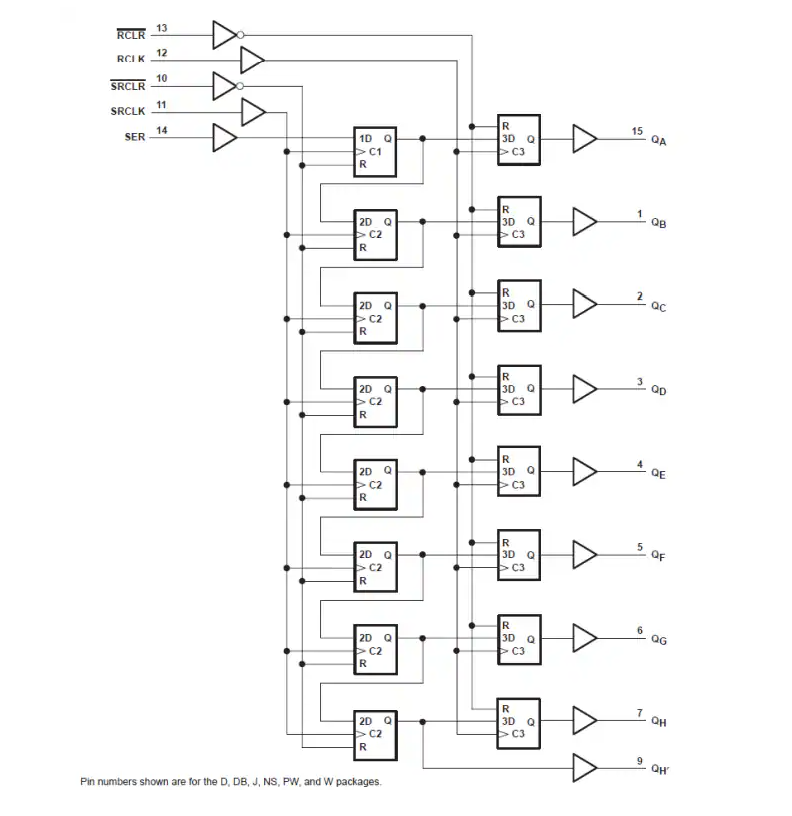

2、TCLK与LVDS数据流速率:

串化器以TCLK的12倍频传输串行数据及内嵌时钟位,每一帧串行数据流为10bit数据,并嵌入1bit起始位+1bit停止位到每一帧数据的寄存器中,起始位恒定为高,停止位恒定为低,在串行数据流中,起始/停止位为嵌入的时钟信息。

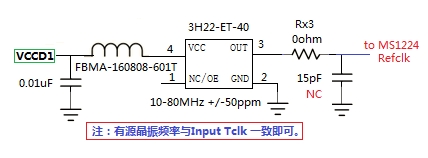

例如 TCLK为40MHz,串行速率为 40×12=480Mbps,由于仅有10bit输入数据,有效数据速率实际为10倍的TCLK频率,所以有效数据速率40×10=400Mbps。提供给MS1023之TCLK的数据源要求在10MHz至80MHz之间。而提供给MS1224之RefCLK也应与MS1023一致,例如 MS1023 TCLK为40MHz,则MS1224 RefCLK为40MHz,RefCLK建议用外挂有源晶振,减少PCB板载连线。参考如下:

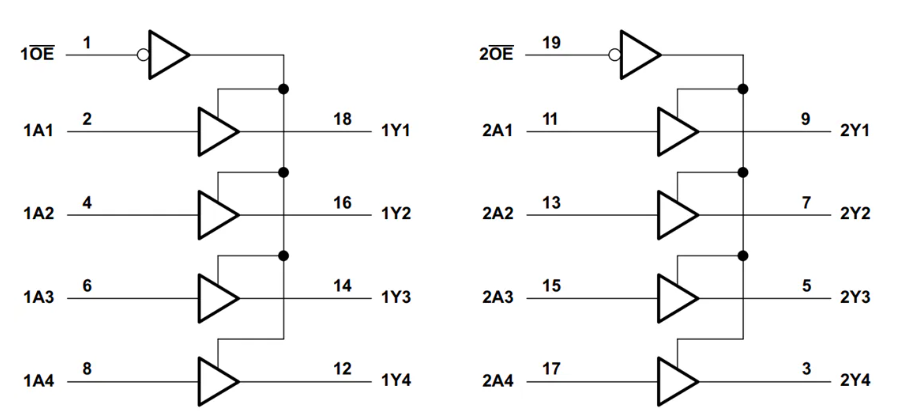

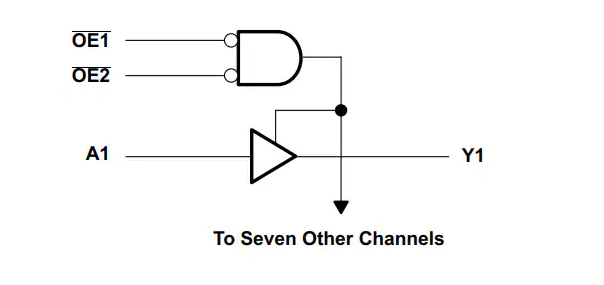

3、关于DEN、REN控制(高阻态模式):

当DEN被置低时,串化器进入高阻模式。这将使所有输出脚(DO+和 DO-)进入高阻状态。当驱动DEN为高 , 串化器恢复到先前的状态 ,同时其他所有控制引脚保持静态(SYNC1,SYNC2, PWRDN ,TCLK_R/F)。

当REN脚被置低时,解串器进入高阻模式,解串器的输出脚(ROUT0-ROUT9)和 RCLK进入高阻状态。 LOCK保持有效(Active),用来跟踪PLL的状态。因此,DEN、REN可与MCU/FPGA建立逻辑控制,待机时,DEN、REN设置为低电平。

4、MS1023 MS1224应用参考原理图

以下为展示的简易原理图,如果你是终端应用工程师,可以联系我们,已获得详细原理图及技术支持。

审核编辑 黄宇

-

SerDes

+关注

关注

8文章

229浏览量

36564 -

SN65LV1023A

+关注

关注

0文章

3浏览量

8379 -

SN65LV1224B

+关注

关注

0文章

2浏览量

6584

发布评论请先 登录

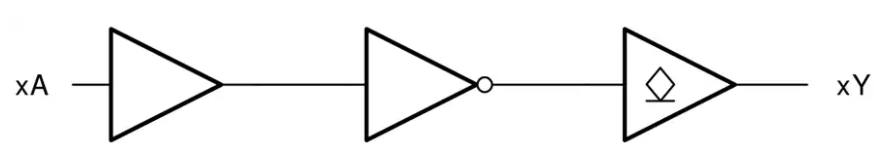

SN65LVDS33和SN65LVDS34高速差分接收器数据手册

SN74LV244A Octal Buffer/Driver技术解析:高速3态输出的多功能解决方案

SN74LV541A:2-5.5V八路3态缓冲器/驱动器技术解析

SN74LV594A:2-5.5V带输出寄存器的8位移位寄存器技术解析

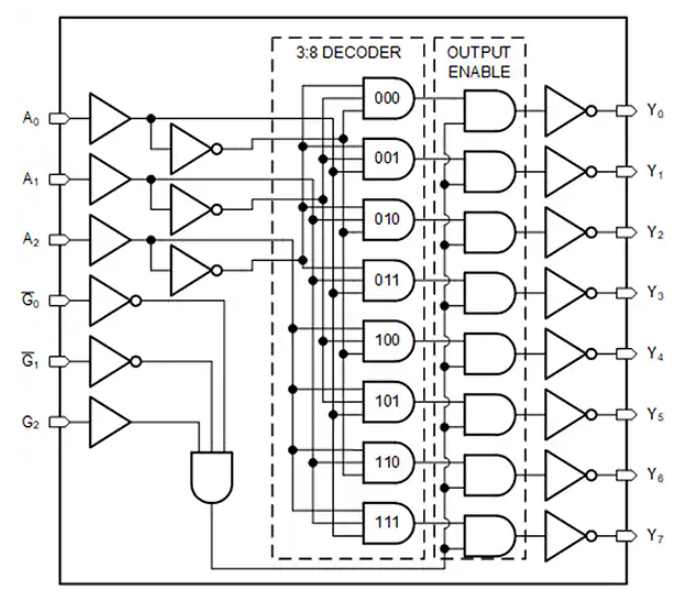

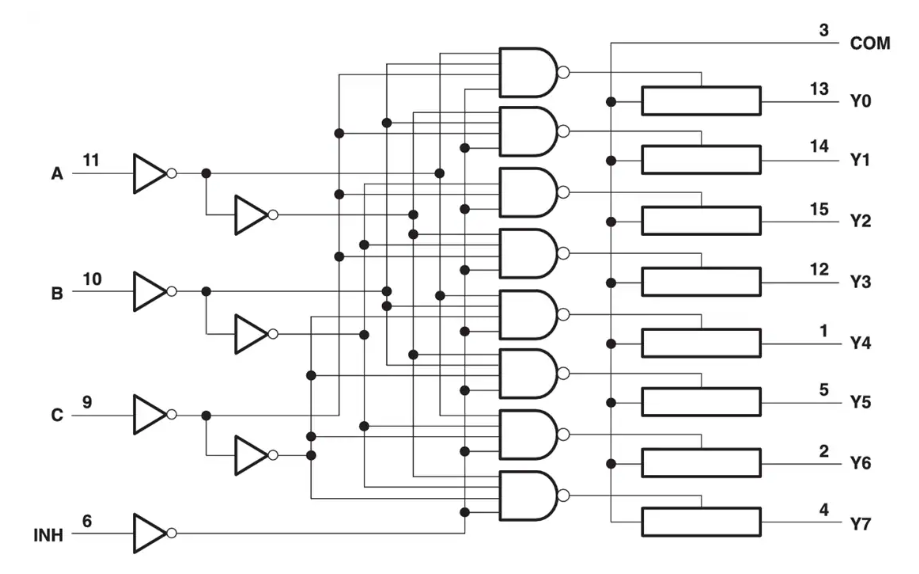

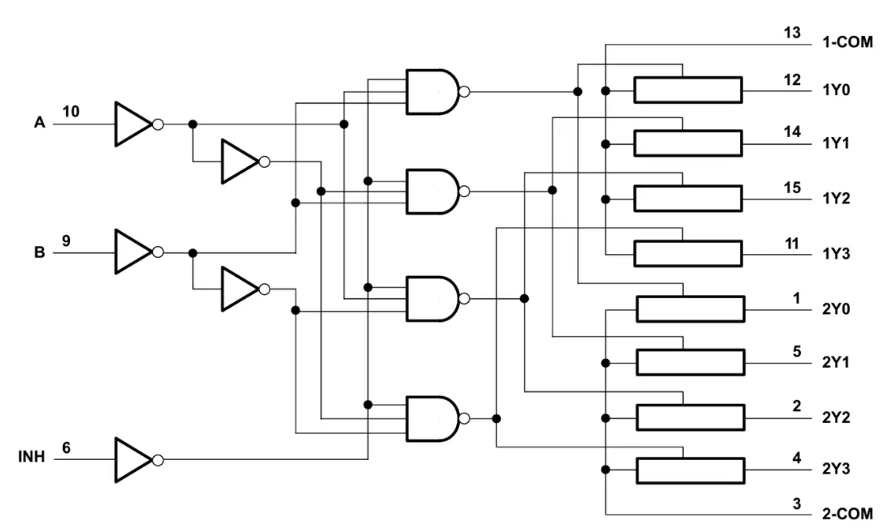

SN74LV138A 3-8线解码器/解复用器技术解析与应用指南

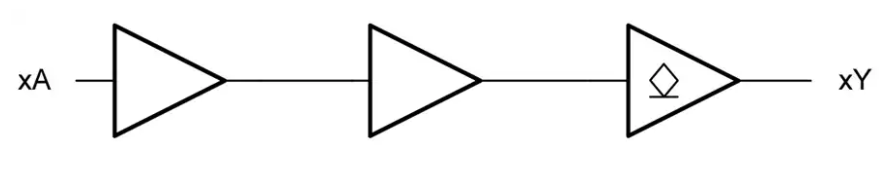

SN74LV6T07 Hex开漏缓冲器技术解析与应用指南

SN74LV6T06/SN74LV6T06-Q1六通道开漏逆变器数据手册

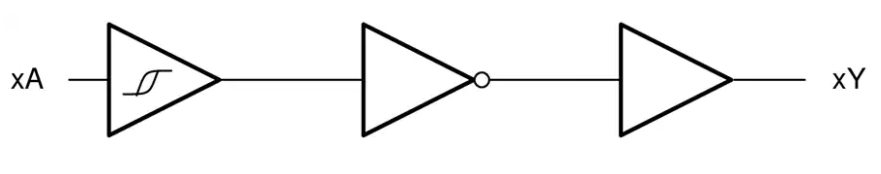

德州仪器SN74LV14B-EP六通道施密特触发反相器技术解析

Texas Instruments SN74LV4051A/SN74LV4051A-Q1模拟多路复用器和解复用器数据手册

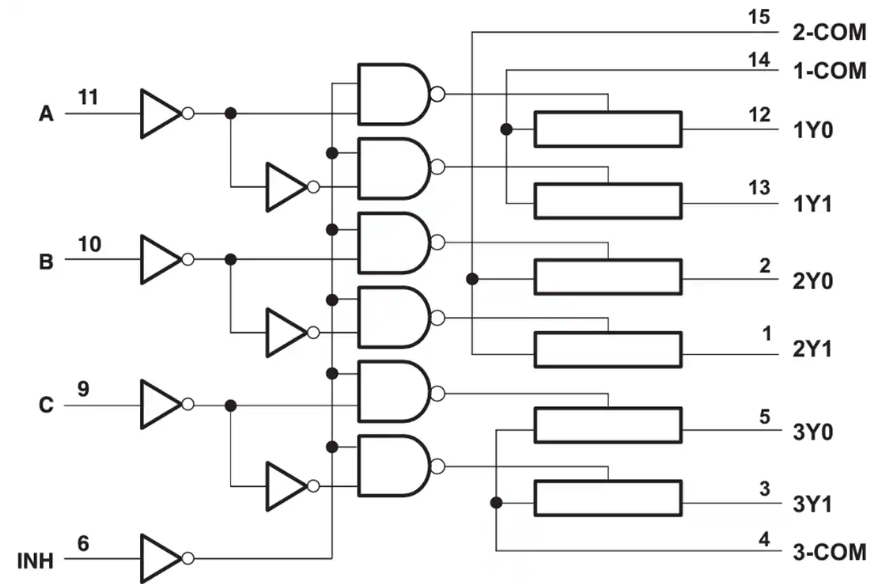

Texas Instruments SN74LV4053A/SN74LV4053A-Q1模拟多路复用器和解复用器数据手册

Texas Instruments SN74LV4052A/SN74LV4052A-Q1双模拟多路复用器和解复用器数据手册

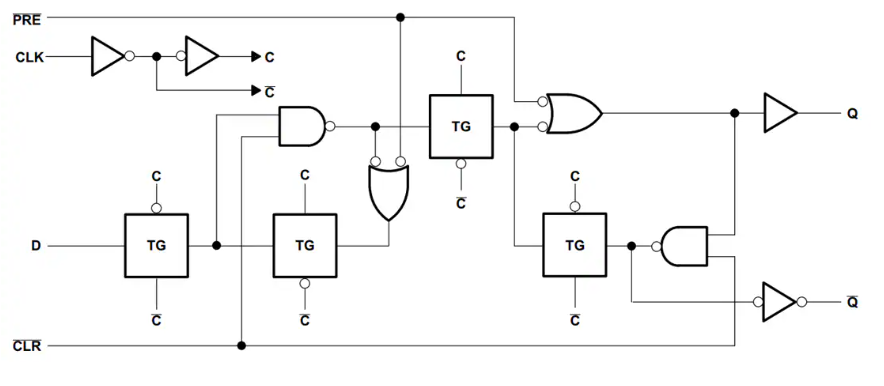

Texas Instruments SN74LV74A/SN74LV74A-Q1双通道D型触发器数据手册

MS1023、SN65LV1023A串化器与MS1224、SN65LV1224B解串器应用

MS1023、SN65LV1023A串化器与MS1224、SN65LV1224B解串器应用

评论