为实现更高性能目标,AI与HPC芯片设计正加速向芯粒架构演进。但是传统单片机SOC已经很难在尺寸上继续扩张,异构集成已成为推动半导体创新的核心动力。然而,它也增加了芯片设计的复杂性,需要更先进的测试方法和经过改进的自动化测试设备(ATE),才能保持信号的完整性、准确性和性能。

随着半导体复杂性的增加,器件的结构测试变得更具挑战性,既要求配备高带宽测试数据接口进行高速测试、确认真正良裸晶粒(KGD),也要在合理的时间范围内实现高测试覆盖率和低DPPM数。在将芯粒集成到复杂的异构集成封装中之前,必须确保单个芯粒达到最高测试覆盖率,否则将导致将多个芯粒封装到一起时遇到良率问题。

测试复杂器件时必须用到的向量数量大幅增加,而用于执行测试的通用IO(GPIO)引脚数量其实非常有限。GPIO速度限制了测试数据吞吐量,降低了有效测试当今设计时的整体覆盖率,尽管传统的高速I/O协议(PCIe/USB)满足带宽要求,但它需要昂贵的硬件设置。

复杂的异构芯片导致测试成本不断增加

HPC和AI计算芯片的功能变得越来越复杂,验证步骤的数量也随之显著增加。在IO引脚数量有限的场景下,验证时间成为关键瓶颈,不仅会延长开发周期,更使测试成本居高不下。

高带宽测试访问端口的可用性有限,尤其是在Multi-Die设计中,这凸显了对特定IO的需求——既要求其运行速度远高于传统GPIO,不能增加额外的硬件,也不能让支持初始化/校准顺序的接口协议变得更复杂,同时更要兼容先进制程的信号完整性要求。

为应对种种挑战,新思科技优化了高速测试GPIO(HSGPIO)设计,可满足这些高速测试要求。新思科技的这款多功能产品确保单个IO可以根据其在制造过程中作为“测试端口”的用途进行多路复用;支持调试期间的“高速时钟观测”;在量产阶段还可以配置为“GPIO”。这种创新设计可以有效支持全面测试需求,在业内独树一帜。

高速测试IO有利于实现简单可靠测试

与其他测试IO相比,新思科技高速测试GPIO IP大幅提高了数据速率,可以高效匹配先进测试设备的需求,支持无协议要求的高速可靠性测试。其主要优势还表现在可以简化测试过程,免除了初始化、校准或训练序列等环节。经过精心设计,其IO在最大速率下仍能保障稳定性和信号完整性。

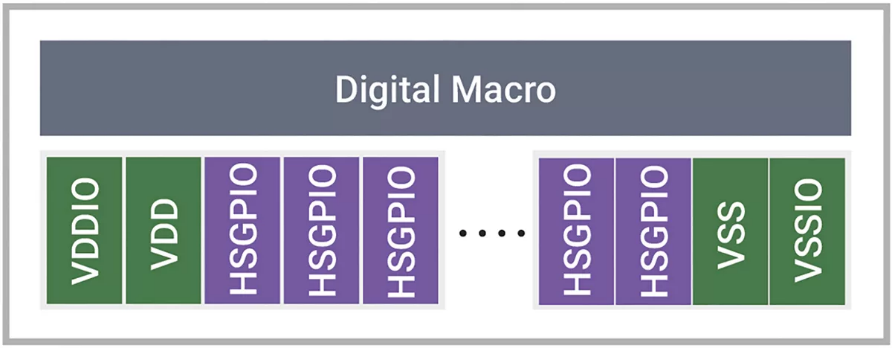

此外,该解决方案节省了GPIO模式和非测试场景下消耗的能源,这种超低功耗特性对于HPC应用至关重要。单端IO设计有助于实现小尺寸、低成本解决方案。得益于其可扩展性,HSGPIO的实现高度灵活,对IO的数量或位置布局没有限制,可以放置在芯片的左侧、右侧或周围。这种灵活性让IO可以更紧临被测电路,从而提高验证效率和便利性。

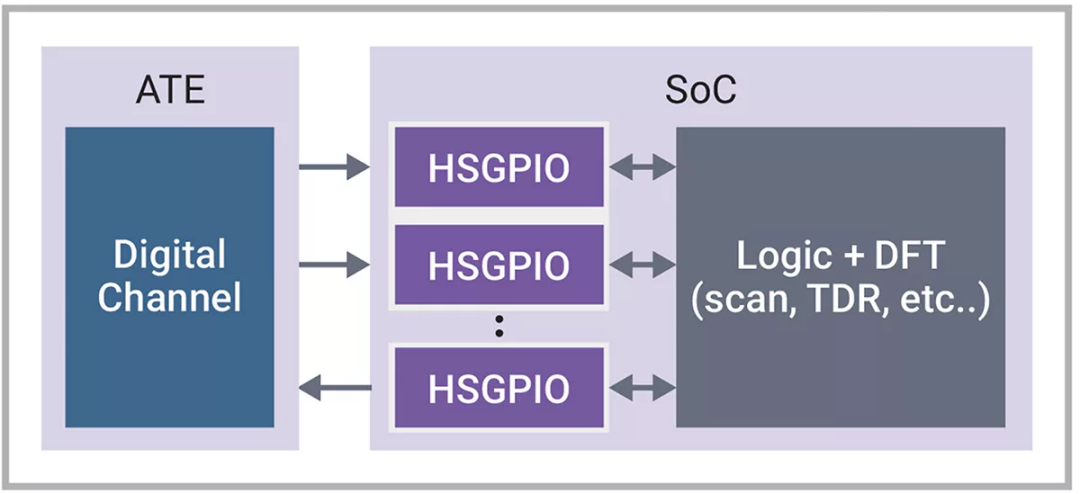

▲图1:用于测试和实施的新思科技高速测试GPIO(HSGPIO)

通过多种模式增强IO性能并优化功耗

在向芯粒架构演进的过程中,许多常规高速接口在单个芯粒上的可用性显著降低。UCIe等Die-to-Die接口负责处理芯粒之间的通信,并占用了大多数连接端口,导致可用于外部测试的接口数量变得有限。考虑到封装引脚非常宝贵,在现场操作中,新思科技高速测试IO支持重复使用与低功耗GPIO相同的高速测试引脚。该解决方案用途广泛,支持各种测试场景,包括BIST和扫描测试,测试覆盖率非常高。此外只需要一个单端PAD即可进行信号传输和测试。总之,相关设计可以简化电路板布局,有效减少PAD数量,提高利用率。

该架构不仅保障了高效的测试性能,还增强了SoC验证阶段的可测试性和可维护性:

测试:高速测试IO在制造过程中充当测试端口,在ATE和SoC之间传输高达3GBPS的数据,适配裸片(晶圆级)和封装级测试要求

观测:IO可复用为参考验证平台(RVP)板上的高速时钟观测器,以便观测CLK

节能模式:同一端口在量产环节可配置为GPIO,常规工作频率高达200MHz,支持低功耗模式

结语

随着SoC复杂性的增加,解决测试中的挑战已成为保障功能性和高产量的关键。新思科技高速测试IO IP采用创新设计,在有限的封装引脚下支持高速测试,在量产模式下实现了低功耗GPIO,有助于高速、高效地测试复杂半导体。相关产品不仅大幅缩短测试时间,更在先进ATE测试仪上实现了高吞吐量,无需复杂的接口协议,同时仍能满足严苛的高速要求。新思科技IO团队将持续为台积公司的先进节点提供高速测试IO IP支持。

-

晶圆

+关注

关注

53文章

5445浏览量

132713 -

封装

+关注

关注

128文章

9317浏览量

149024 -

新思科技

+关注

关注

5文章

977浏览量

52985

原文标题:新思科技测试IO方案:晶圆级到封装级 3Gbps带宽,加速HPC和AI芯片高质量量产

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

2026新思科技IP技术开放日精彩回顾

新思科技首届Converge大会隆重举行

AI服务器量产关键:高效安规测试方案解决多点测试挑战

格罗方德收购新思科技处理器 IP 解决方案业务, 扩充实力以加速物理 AI 应用落地

新思科技以AI驱动EDA加速Multi-Die创新

新思科技旗下Ansys仿真和分析解决方案产品组合已通过台积公司认证

威宏科技加入Arm Total Design生态系统,携手推动AI与HPC芯片创新

思科Cisco 8223:51.2Tbps P200芯片助力AI数据中心

新思科技邀您相约2025上海汽车测试及质量监控博览会

普迪飞携AI测试解决方案与爱德万测试V93000平台高效集成,加速提升测试效能

新思科技测试IO方案加速HPC和AI芯片量产

新思科技测试IO方案加速HPC和AI芯片量产

评论