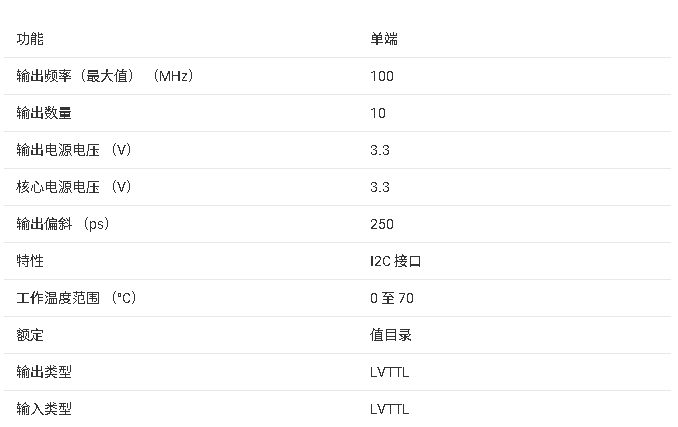

CDC319 是一款高性能时钟缓冲器,可将一个输入 (A) 分配到 10 个输出 (Y),最小 时钟分布的倾斜。CDC319采用3.3 V电源供电,其工作特性 从 0°C 到 70°C。

该器件提供标准模式(100K-bits/s)I^2^用于设备控制的 C 串行接口。执行 是作为从属/接收器。设备地址在 I^2^C 设备地址表。两个我^2^C 输入 (SDATA和SCLOCK)提供集成上拉电阻(典型值为140 k),并且具有5 V容差。

*附件:cdc319.pdf

三个 8 位 I^2^C 寄存器为每个输出提供单独的使能控制。所有输出默认为启用 在通电时。当低电平控制位时,每个输出都可以置于低电平输出的禁用模式 写入控制寄存器。寄存器是仅写的,必须按顺序访问(即 不支持寄存器的随机访问)。

CDC319 提供 3 态输出,用于测试和调试目的。输出可以放置在 通过输出使能 (OE) 输入实现高阻抗状态。当OE为高电平时,所有输出都处于工作状态。 当OE为低电平时,输出处于高阻抗状态。OE 提供集成上拉电阻器。

特性

- 用于SDRAM(同步DRAM)时钟缓冲应用的高速、低偏斜1-10时钟缓冲器

- 输出倾斜,t

SK(O),小于 250 ps - 脉冲偏斜,t

SK(p),小于 500 ps - 支持多达两个无缓冲 SDRAM DIMM(双列直插式内存模块)

- 我^2^C 串行接口为每个输出提供单独的使能控制

- 工作电压为 3.3 V

- 分布式V

CC接地引脚可降低开关噪声 - ESD 保护超过 2000 V,符合 MIL-STD-883,方法 3015

- 采用 28 引脚热缩小外形 (DB) 封装

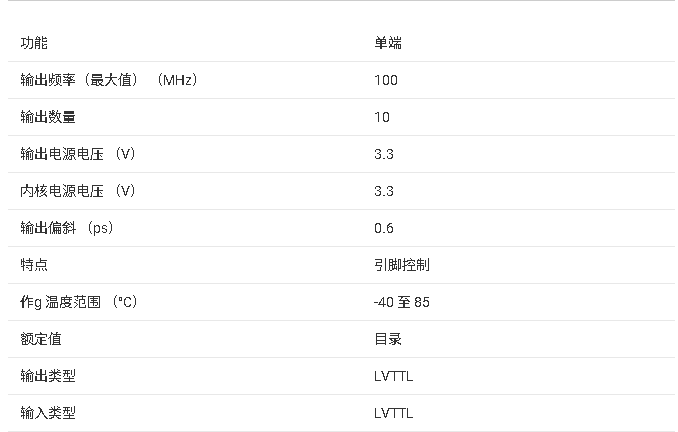

参数

1. 产品概述

CDC319是德州仪器(TI)设计的高性能时钟缓冲器,专为SDRAM时钟分配应用优化。核心功能包括:

- 1输入转10输出:单时钟输入(A)分配至10路低偏移输出(Y0-Y9)

- 关键性能指标:输出偏移(tsk(o))<250ps,脉冲偏移(tsk(p))<500ps

- 工作电压:3.3V,温度范围0°C至70°C

2. 核心特性

- I²C控制接口:

- 支持标准模式(100kbps)串行通信

- 3个8位寄存器独立控制每路输出使能(默认上电全启用)

- 地址固定为0b1101000X(X为R/W位)

- 输出管理:

- 输出使能(OE)引脚可全局置高阻态(集成140kΩ上拉电阻)

- 通过I²C可单独禁用输出(强制拉低)

3. 封装与引脚

- 28引脚SSOP封装(DB)

- 分布式VCC/GND引脚设计降低开关噪声

- 输出分组:

- 1Y0-1Y3:SDRAM字节0时钟

- 2Y0-2Y3:SDRAM字节1时钟

- 3Y0-3Y1:外部PLL反馈时钟

4. 电气特性

- 最大时钟频率:

- 140MHz(CL=15pF @70°C)

- 125MHz(CL=20pF @70°C)

- ESD防护:超过2000V(MIL-STD-883方法3015)

- 功耗:典型值0.5mA(静态)

5. 应用设计要点

- 时序控制:

- 传播延迟1.2-3.6ns(输入到输出)

- 启用/禁用时间4.7ns(OE控制)

- 布局建议:

- 每路输出负载电容≤30pF以保证高频稳定性

- 需考虑传输线匹配(典型阻抗50Ω)

6. 生产与认证

- 符合TI标准质保条款

- 封装选项包括管装(50片/管)和卷带(2000片/卷)

- RoHS兼容(无铅工艺)

该器件适用于需要精确时钟分配的高可靠性系统,如服务器内存模块、通信设备时钟树等关键应用场景。

-

接收器

+关注

关注

15文章

2651浏览量

77493 -

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

串行接口

+关注

关注

3文章

523浏览量

45325 -

电源供电

+关注

关注

0文章

217浏览量

23010

发布评论请先 登录

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

CDC319带I2C控制接口的1线至10线时钟驱动器数据表

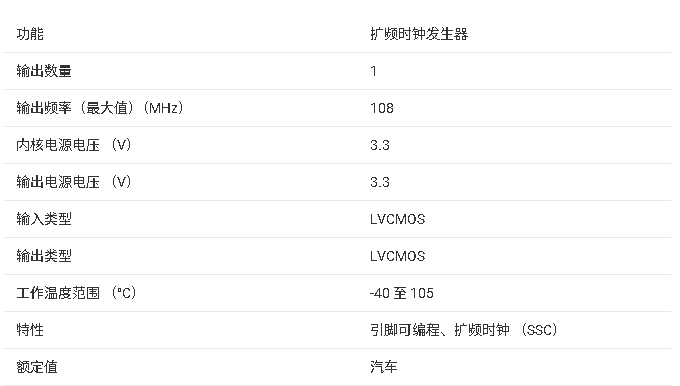

CDCS503-Q1 时钟缓冲器/时钟倍频器技术文档总结

CDC319 1-to-10时钟缓冲器技术文档总结

CDC319 1-to-10时钟缓冲器技术文档总结

评论