高性能时钟缓冲器 CDC318A:特性、参数与应用解析

在电子设计领域,时钟缓冲器对于确保系统时钟信号的稳定和准确传输至关重要。今天,我们就来详细探讨一下德州仪器(Texas Instruments)的 CDC318A 时钟缓冲器,它在同步动态随机存取存储器(SDRAM)时钟缓冲应用中表现出色。

文件下载:cdc318a.pdf

一、CDC318A 概述

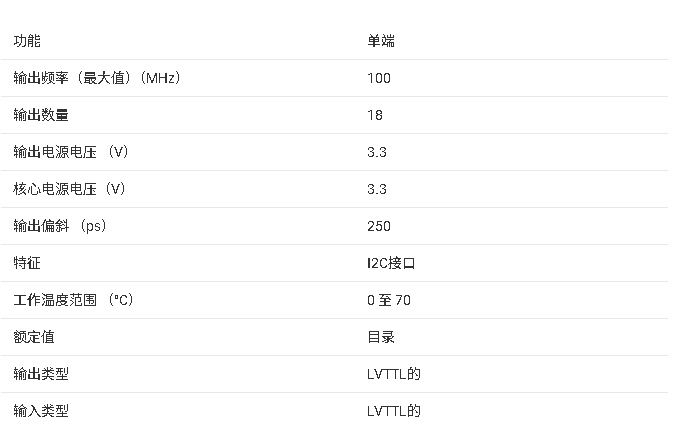

CDC318A 是一款专门为 PC 应用设计的高性能时钟缓冲器,它能够以最小的偏移将一个输入时钟信号分配到 18 个输出端。该器件采用 3.3V 电源供电,工作温度范围为 0°C 至 70°C。

主要特性

- 低偏移性能:输出偏移 (t{sk(o)}) 小于 250ps,脉冲偏移 (t{sk(p)}) 小于 500ps,确保了时钟信号的高精度传输。

- 多模块支持:最多可支持四个未缓冲的 SDRAM 双列直插式内存模块(DIMMs)。

- I²C 串行接口:为每个输出提供独立的使能控制,方便用户进行灵活配置。

- 低噪声设计:分布式 (V_{CC}) 和接地引脚减少了开关噪声,提高了系统的稳定性。

- 高速运行:能够在 100MHz 的频率下稳定工作。

- ESD 保护:静电放电(ESD)保护超过 2000V,符合 MIL - STD - 883 标准的 3015 方法。

- 封装形式:采用 48 引脚收缩小外形(DL)封装。

二、功能与接口

(一)功能表

CDC318A 的功能表清晰地展示了输入信号(OE 和 A)与输出信号(1Y0 - 1Y3、2Y0 - 2Y3 等)之间的逻辑关系。当 OE 为低电平时,所有输出处于高阻态;当 OE 为高电平时,输出状态取决于输入 A 的状态。同时,需要注意的是,如果通过 I²C 配置寄存器位禁用了某个输出,无论输入 A 的状态如何,该输出都将被驱动为低电平。

(二)I²C 接口

I²C 串行接口是 CDC318A 的重要特性之一。它通过三个 8 位的 I²C 寄存器为每个输出提供独立的使能控制。每个寄存器的位定义对应着不同的输出使能状态,默认情况下,所有位的值为高,即所有输出均处于使能状态。此外,I²C 接口的 SCLOCK 和 SDATA 引脚内部集成了标称值为 140kΩ 的上拉电阻,方便与其他设备进行连接。

(三)引脚功能

CDC318A 的引脚功能丰富多样,涵盖了时钟输入、输出使能、电源、接地等多个方面。其中,1Y0 - 1Y3、2Y0 - 2Y3 等引脚为 3.3V SDRAM 时钟输出;A 引脚为时钟输入;OE 引脚用于输出使能控制;SCLOCK 和 SDATA 引脚用于 I²C 串行通信。同时,需要注意 NC 引脚为无内部连接,保留用于未来扩展。

三、电气与开关特性

(一)绝对最大额定值

在使用 CDC318A 时,必须严格遵守其绝对最大额定值,以避免对器件造成永久性损坏。这些额定值包括电源电压范围、输入电压范围、输出电压范围、电流限制、温度范围等。例如,电源电压范围为 - 0.5V 至 4.6V,输入电压范围在 - 0.5V 至 4.6V 之间(部分引脚可达 - 0.5V 至 6.5V)。

(二)推荐工作条件

为了确保 CDC318A 能够在最佳状态下工作,推荐遵循其推荐工作条件。这些条件包括电源电压、输入电压、输出电流、时钟频率等。例如,3.3V 核心电源电压的推荐范围为 3.135V 至 3.465V,SCLOCK 频率为 100kHz。

(三)电气特性

CDC318A 的电气特性包括输入钳位电压、高低电平输出电压、输入输出电流等。这些特性反映了器件在不同工作条件下的性能表现。例如,在 VCC = 3.135V 时,高电平输出电流在不同输出电压下有不同的取值范围。

(四)开关特性

开关特性对于时钟信号的传输至关重要。CDC318A 的开关特性包括传播延迟时间、上升时间、下降时间、偏移时间等。例如,从输入 A 到输出 Y 的低到高电平传播延迟时间 (t{PLH}) 在 1.2ns 至 4.5ns 之间,输出偏移 (t{sk(o)}) 小于 250ps。

四、ESD 与热信息

(一)ESD 保护

CDC318A 具有良好的 ESD 保护性能,其人体模型(HBM)ESD 保护超过 2000V,机器模型(MM)为 200V,充电器件模型(CDM)为 2000V。这使得器件在实际应用中能够更好地抵抗静电干扰,提高了系统的可靠性。

(二)热信息

了解器件的热特性对于确保其在不同环境下的稳定工作至关重要。CDC318A 的封装热阻 (theta_{JA}) 为 84°C/W,在特定的 PCB 布局下,如使用带有铜层的 PCB 板,热阻可以显著降低。这意味着在设计散热方案时,需要考虑 PCB 的布局和散热措施,以保证器件的温度在合理范围内。

五、封装与订购信息

(一)封装形式

CDC318A 采用 48 引脚收缩小外形(DL)封装,这种封装形式具有体积小、集成度高的特点,适合在空间有限的 PCB 板上使用。

(二)订购信息

CDC318A 有多种可订购的型号,如 CDC318ADL、CDC318ADLR 等。不同型号在包装数量、载体形式等方面可能有所不同。例如,CDC318ADL 采用 TUBE 包装,每包 25 个;CDC318ADLR 采用 LARGE T&R 包装,每包 1000 个。同时,这些型号都符合 RoHS 标准,并且具有相同的工作温度范围和引脚数。

六、设计建议与注意事项

(一)PCB 布局

在进行 PCB 设计时,应注意分布式 (V_{CC}) 和接地引脚的布局,以减少开关噪声。同时,尽量缩短时钟信号的走线长度,避免信号干扰。此外,根据应用布局,在大多数情况下,可能不需要在时钟输出端串联阻尼电阻,这有助于简化设计。

(二)I²C 通信

在使用 I²C 接口进行通信时,要确保 SCLOCK 和 SDATA 引脚的信号质量。同时,注意 I²C 总线的时序要求,如总线空闲时间、起始建立时间、起始保持时间等,以保证通信的稳定性。

(三)散热设计

考虑到 CDC318A 的热特性,在设计散热方案时,可以采用带有铜层的 PCB 板,以降低热阻。此外,还可以根据实际情况添加散热片或风扇,以确保器件在高温环境下的正常工作。

CDC318A 作为一款高性能的时钟缓冲器,具有低偏移、多模块支持、I²C 控制等诸多优点,在 SDRAM 时钟缓冲应用中具有广泛的应用前景。电子工程师在设计过程中,需要充分了解其特性和参数,合理进行 PCB 布局和散热设计,以确保系统的稳定和可靠运行。你在使用类似时钟缓冲器时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

SDRAM

+关注

关注

7文章

458浏览量

57849 -

时钟缓冲器

+关注

关注

2文章

273浏览量

51956

发布评论请先 登录

高性能时钟缓冲器 CDC318A:特性、参数与应用解析

高性能时钟缓冲器 CDC318A:特性、参数与应用解析

评论