低噪声时钟抖动清除器LMK04610:技术拆解与应用设计

在电子设备的世界里,时钟信号就如同心脏的跳动,稳定而精准的时钟对于各类系统的正常运行至关重要。今天,我们要深入探讨的就是一款在时钟处理领域表现卓越的器件——LMK04610。

文件下载:lmk04610.pdf

一、LMK04610简介

LMK04610是一款超低噪声、低功耗的JESD204B兼容时钟抖动清除器,采用双环路PLL架构,拥有出色的性能和广泛的应用场景。

1.1 关键特性

- 超低噪声性能:在不同频率下展现出极低的抖动。例如在1966.08MHz时,RMS抖动低至48fs;983.04MHz时为50fs;122.88MHz时为61fs。其在122.88MHz的噪声基底可达 -165dBc/Hz。

- JESD204B支持:具备单触发、脉冲和连续SYSREF功能,能满足多种数据传输协议的需求。

- 多输出灵活配置:拥有10个差分输出时钟,分布在8个频率组中,输出摆幅可在700mVpp至1600mVpp之间进行编程设置。

- 丰富的输入和功能模式:提供两个参考输入,具备保持模式、自动和手动切换模式以及信号丢失(LOS)检测功能。

- 低功耗运行:典型功耗仅为0.88W(10个输出激活时),采用1.8V(输出、输入)和3.3V(数字、PLL1、PLL2_OSC、PLL2核心)电源供电。

1.2 应用领域

- 无线基础设施:如LTE基站、小基站和远程无线电单元(RRU),确保信号处理和传输的精准性。

- 数据转换和集成收发器时钟:为数据采集和转换系统提供稳定的时钟源。

- 网络通信:适用于SONET/SDH、DSLAM等网络设备,保障数据的高速稳定传输。

- 测试测量:在高精度的测试和测量仪器中,提供可靠的时钟信号。

二、技术细节剖析

2.1 双环路PLL架构

LMK04610的双环路PLL架构是其实现低抖动性能的关键。PLL1由外部参考时钟驱动,采用窄环路带宽,通常在10Hz至200Hz之间,用于保留参考时钟输入信号的频率准确性,同时抑制高频段的相位噪声。PLL2则使用内部低噪声VCO,采用宽环路带宽,一般在90kHz至500kHz之间,以充分利用内部VCO的高频相位噪声优势和参考VCXO的低频相位噪声优势,最终实现超低抖动输出。

2.2 参考输入切换

该器件有两个参考时钟输入(CLKin0和CLKin1),可通过CLKin_SEL_MODE进行三种不同的输入切换模式设置:

- 寄存器选择模式(Register Select Mode):通过寄存器SW_REFINSEL[3:0]来选择CLKin0或CLKin1。若在此模式下进入保持模式,设备在保持模式退出后会重新锁定到所选的CLKin。

- 引脚选择模式(Pin Select Mode):通过CLKin_SEL引脚选择激活的时钟输入,其极性可通过CLKinSEL1_INV位进行反转。

- 自动模式(Automatic Mode):通过编程CLKINx_PRIO[1:0]设置每个输入时钟的优先级。系统启动时会锁定优先级最高的输入时钟,当某个时钟丢失时,内部PLL会自动切换到下一个可用的时钟。为确保切换过程中输出时钟的最小干扰,建议同时使用保持模式。

2.3 时钟输出特性

- 输出格式:所有CLKoutX输出可编程为HSDS或HCSL类型,OSCout还可选择LVCMOS输出类型。HSDS输出类型可设置为800、1200或1600mVpp的差分幅度水平。

- 输出延迟:时钟输出具备模拟和数字延迟功能,用于相位调整。模拟延迟步长通常为60ps,总延迟范围可达0 - 1.2ns;数字延迟可使输出通道延迟1 - 255个VCO周期,延迟步长最小可为时钟分配路径周期的一半。

- 同步功能:使用SYNC输入可使所有活动时钟输出在固定数字延迟编程的上升沿上同步,确保时钟信号的一致性。

2.4 其他重要特性

- 数字锁定检测:PLL1和PLL2都支持数字锁定检测功能,通过比较参考路径(R)和反馈路径(N)的相位,当时间误差小于指定窗口大小时,锁定检测计数递增。当计数达到用户指定的值时,锁定检测被断言为真。

- 保持模式:当PLL1的参考输入时钟失效时,保持模式可使PLL2保持锁定,频率漂移最小。在此模式下,PLL1电荷泵被三态化,设置固定的调谐电压以实现开环操作。

三、应用设计指南

3.1 典型应用示例

以一个远程无线电头(RRU)类型的应用为例,此应用需要为ADC、DAC、FPGA、SERDES和LO提供时钟,输入时钟为需要抖动清除的恢复时钟,FPGA时钟需要在上电时就有输出。具体时钟输入和输出要求如下:

- 时钟输入:122.88MHz的恢复时钟。

- 时钟输出:1个245.76MHz时钟用于ADC;2个983.04MHz时钟用于DAC;2个122.88MHz时钟用于FPGA;1个122.88MHz时钟用于SERDES。

3.2 设计步骤

- 设备选择:根据所需输出频率确定所需的VCO频率,所选设备必须能够产生可分频至所需输出频率的VCO频率。可利用德州仪器提供的时钟设计工具,考虑特定设备的VCO频率范围,辅助进行设备选择。

- 设备配置

- PLL环路滤波器设计:联系德州仪器,根据具体应用要求获取优化的环路滤波器设置。

- 时钟输出分配:在选择最终时钟输出位置时,需考虑每个时钟输出之间以及与其他PLL电路的接近程度。建议将相同频率的时钟分组,对于需要低近端相位噪声的时钟目标,优先使用基于VCXO的PLL1输出(如OSCout/OSCout*);对于需要出色噪声基底性能的时钟目标,选择由内部LC-VCO驱动的输出(如用于ADC或DAC的输出)。

- 计算LCM:在本例中,计算LCM(245.76MHz, 983.04MHz, 122.88MHz) = 983.04MHz,而LMK04610的有效VCO频率为5898.24MHz = 6 × 983.04MHz,因此该设备可用于产生这些输出频率。

- 设备编程:使用TICS Pro EVM编程软件将设备设置为所需配置,然后导出适合应用使用的十六进制寄存器映射。同时,还可使用WEBENCH Clock Architect Tool,输入所需频率和格式,筛选出使用LMK04610的解决方案。

3.3 注意事项

- 电源连接:所有(V_{CC})引脚必须始终连接,建议使用低噪声LDO和DC - DC转换器,如文档中推荐的电源连接方式。

- 引脚使用:未使用的时钟输出应保持悬空并断电;未使用的时钟输入可以悬空。

- 布局设计:考虑到器件的功耗较高,需要注意热管理。器件封装的暴露焊盘是主要的散热路径,应将其焊接到PCB上的接地层,同时在PCB的封装 footprint内添加热焊盘和多个过孔以增强散热。CLKin和OSCin的差分输入应紧密耦合布线,单端输入应与其他RF走线保持至少3倍走线宽度的距离;CLKout的差分信号也应紧密耦合,根据输出类型设计合适的走线阻抗和端接。

四、总结

LMK04610凭借其卓越的低噪声性能、灵活的配置选项和丰富的功能特性,成为了众多电子系统中时钟处理的理想选择。无论是在无线通信、数据采集还是测试测量等领域,都能为系统提供稳定、精准的时钟信号。在实际应用设计中,我们需要深入理解其技术细节,按照合理的设计步骤进行操作,并注意布局和电源等方面的问题,以充分发挥其性能优势,为我们的电子设计带来更可靠的保障。

希望通过本文的分享,能让大家对LMK04610有更深入的了解,在实际工作中能够更加得心应手地运用这款优秀的器件。大家在使用过程中有任何问题或经验,欢迎在评论区留言交流!

发布评论请先 登录

请问LMK04610可以单端输出吗?

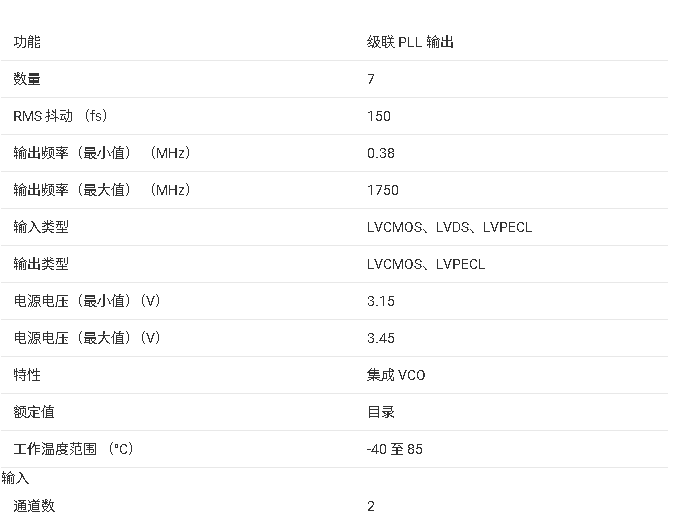

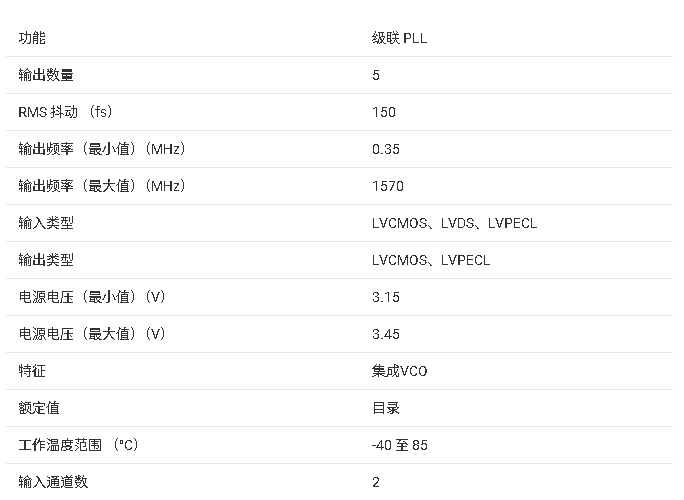

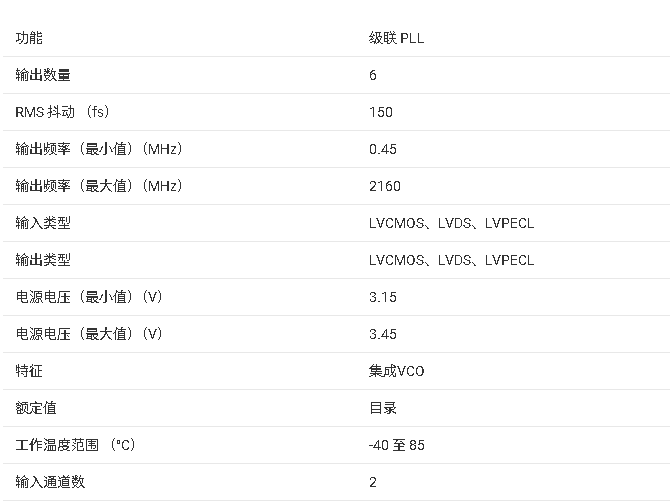

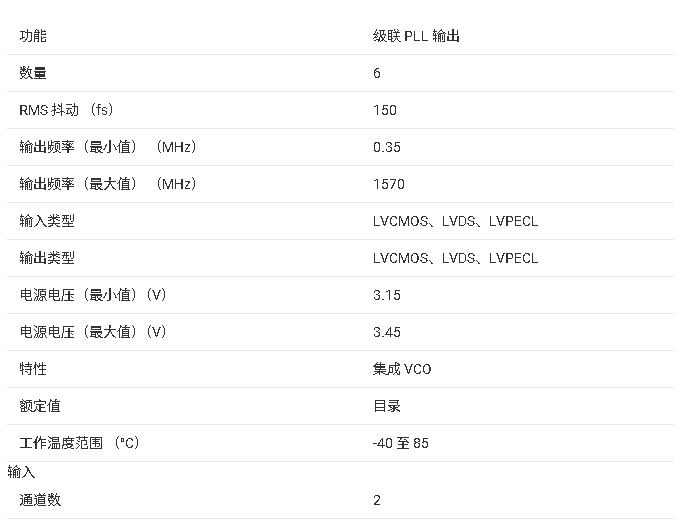

LMK04610 LMK0461x 符合 JESD204B 标准的超低噪声和低功耗时钟抖动消除器

LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表

LMK04832-SEP符合JESD204B/C标准的航天级、超低噪声、双环路时钟抖动清除器数据表

带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表

LMK04906带6路可编程输出的,超低噪声时钟抖动清除器和乘法器数据表

具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表

低噪声时钟抖动清除器LMK04610:技术拆解与应用设计

低噪声时钟抖动清除器LMK04610:技术拆解与应用设计

评论