电子发烧友网综合报道,NEO Semiconductor宣布推出全球首款用于AI芯片的超高带宽内存 (X-HBM) 架构。该架构旨在满足生成式AI和高性能计算日益增长的需求,其32Kbit数据总线和单芯片高达512 Gbit的容量,带宽提升16倍,密度提升10倍,显著突破了传统HBM的局限性。

关键特性和优势包括,可扩展性,使GPU和内存之间的数据传输更快,从而实现更高效的AI扩展;高性能,解锁未开发的GPU能力以提升AI工作负载;可持续性,通过整合AI基础设施减少电力和硬件需求。

X-HBM 的两大技术基础是超高密度 I/O 通道和X-DRAM高容量 3D 内存。该企业宣称可通过 0.5μm(500nm)间距超精细混合键合在 HBM 所需 DRAM Die 上创造 32000-bit 超宽 I/O,而目前即将进入商业化的 HBM4 内存也仅有 2048-bit。

而在容量方面,NEO Semiconductor 称其现有技术可通过 300 层堆叠技术在单层 DRAM Die 上实现 300Gb 容量,这已经是当下 HBM 领域所用 24Gb Die 的 12.5 倍。而未来 X-HBM 中的单 Die 将可实现 500+ 层阵列堆叠,单 Die 容量随之提升到 512Gb (64GB)。

基于NEO的专有3D X-DRAM架构,X-HBM在内存技术上实现了重大突破,消除了在带宽和密度方面长期存在的限制。相比之下,仍处于开发阶段、预计于2030年左右面世的HBM5,预计仅能支持4K位数据总线和每芯片40 Gbit。

韩国高等科技学院(KAIST)最近的一项研究预测,即便是预计于2040年左右问世的HBM8,也仅能提供16K位总线和每芯片80Gbit。相比之下,X-HBM则提供32K位总线和每芯片512 Gbit,使得AI芯片设计师能够绕开与传统的HBM技术相关的整整十年的渐进式性能瓶颈。

NEO半导体研发的3D DRAM与水平放置存储单元的传统DRAM不同,3D DRAM垂直堆叠存储单元大大增加单位面积的存储容量并提高效率,成为下一代DRAM关键发展方向。

NEO表示,动态随机存取存储器(DRAM)用于支持处理器,使DRAM在电子设备中的使用更加普遍。然而,处理器速度的增长速度比多代内存速度更快,由此产生的“性能差距”逐年扩大。像云数据中心这样的功耗敏感环境越来越依赖更高功率的处理器来满足性能要求,但这会减少可用于内存的功率。

采用X-DRAM架构可以降低功耗,降低延迟,并增加吞吐量,以克服使用传统DRAM时遇到的这些和其他挑战。这为商业系统(例如服务器)提供了更高的性能,为移动设备(例如智能手机)提供了更长的电池寿命,为边缘计算设备(例如路由器)提供了更多的功能,并为物联网对象(例如网关)提供了新的部署选项。

3D X-DRAM的单元阵列结构类似于3D NAND Flash,采用了FBC(无电容器浮体单元)技术,它可以通过添加层掩模形成垂直结构,从而实现高良率、低成本和显著的密度提升。NEO表示, 3D X-DRAM 技术可以生产230层的128Gbit DRAM 芯片,是当前 DRAM 密度的八倍。

-

DRAM

+关注

关注

41文章

2402浏览量

189573 -

存储

+关注

关注

13文章

4891浏览量

90290 -

HBM

+关注

关注

2文章

434浏览量

15884

发布评论请先 登录

内存要取代GPU?HBM之父警告:以英伟达GPU为核心的架构要被颠覆

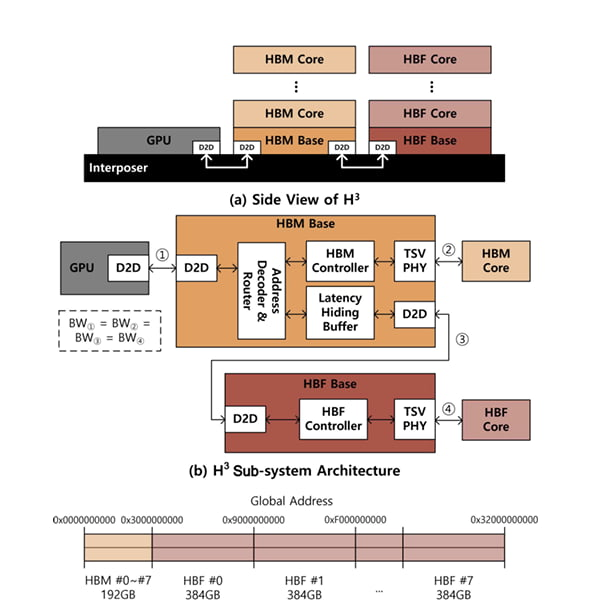

KV缓存黑科技!SK海力士“H³存储架构”,HBM和HBF技术加持!

不同于HBM垂直堆叠,英特尔新型内存ZAM技术采用交错互连拓扑结构

JEDEC制定全新内存标准,将取代HBM?

AI大算力的存储技术, HBM 4E转向定制化

美光确认HBM4将在2026年Q2量产

HBM技术在CowoS封装中的应用

全球首款HBM4量产:2.5TB/s带宽超越JEDEC标准,AI存储迈入新纪元

传英伟达自研HBM基础裸片

突破堆叠瓶颈:三星电子拟于16层HBM导入混合键合技术

性能优于HBM,超高带宽内存 (X-HBM) 架构来了!

性能优于HBM,超高带宽内存 (X-HBM) 架构来了!

评论