电子发烧友网综合报道

随着人工智能算力需求的指数级爆发,数据中心对内存的性能、容量与成本平衡提出了前所未有的严苛要求。HBM凭借1024-bit甚至2048-bit的超高位宽,成为AI加速卡的核心配套组件,其无可匹敌的带宽与能效比,支撑着大模型训练、自动驾驶等密集型计算任务的推进。

但与此同时,HBM的超高位宽设计也带来了显著短板,大量占用宝贵的芯片面积,限制了单颗芯片的堆叠数量与封装容量,进一步制约了AI加速卡的性能上限,且依赖昂贵的中介层技术,成本居高不下,难以在中高端需求场景中大规模普及。

正是在这一背景下,全球半导体标准组织JEDEC着手制定全新的“SPHBM4”(标准封装高带宽内存第四代)内存标准,试图在高性能与高性价比之间找到平衡点,为AI内存生态注入新的活力。

SPHBM4最核心的技术突破,在于通过4:1串行技术重构了数据传输架构,将传统HBM4需要的2048-bit位宽大幅缩减至512-bit,却依然能保持同等的HBM4级别带宽,且性能表现远超当前主流的DDR5内存。

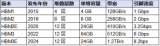

相较于传统DDR系列,SPHBM4展现出碾压性的性能优势。以DDR5为例,尽管后者凭借16Gb颗粒和3200MT/s速率在消费级市场备受欢迎,但其单条容量上限仅为64GB,理论带宽也停留在819GB/s。

反观SPHBM4,借助独特的堆叠设计和TSV硅通孔技术,单颗芯片即可实现64GB容量,堆叠后容量更可突破256GB,带宽更是可以超过2TB/s。这种跨越式的提升,使得SPHBM4在面对AI集群、超算中心等高负载场景时,展现出传统内存难以企及的吞吐能力。

从市场定位来看,SPHBM4清晰地站在了DDR与HBM之间的中间地带,填补了当前内存市场的关键空白。

一方面,相较于DDR5内存,SPHBM4的带宽优势显著,能够满足AI推理、中小型模型训练等对数据传输速度有较高要求的场景,解决了DDR5在高密度计算中带宽瓶颈的问题;另一方面,与HBM4相比,SPHBM4成本更低、封装更灵活,无需承担硅中介层带来的额外开支,适合对性能有要求但无需追求极致算力的场景,比如边缘AI服务器、工业级智能设备等。

不过,这种定位也决定了SPHBM4并非万能解决方案,它不会取代GDDR显存成为显卡的新选择。原因在于,SPHBM4虽成本低于HBM4,但仍采用堆叠式设计,且需要配套的基片接口、TSV技术与先进封装工艺,成本远高于普通GDDR芯片;若用单颗SPHBM4替代多颗GDDR6/7,不仅会大幅增加显卡成本,性能提升效果却并不明显,不符合消费级显卡的成本效益逻辑。

值得注意的是,SPHBM4的落地离不开关键技术的支撑,其中TSV硅通孔技术与先进封装集成技术是核心。TSV技术能够实现芯片内部垂直方向的高效数据传输,为多Die堆叠提供稳定的连接基础,而先进封装则确保了在缩减位宽的同时,内存模块的散热效率与信号完整性不受影响。这些技术并非全新突破,但SPHBM4通过对现有技术的整合优化,实现了性能、容量与成本的协同提升,体现出JEDEC在标准制定过程中对产业实际需求的深度洞察。

对于整个内存行业而言,SPHBM4的出现并非简单的技术迭代,更标志着AI时代内存技术开始向多元化细分方向发展。未来,随着SPHBM4标准的逐步完善与量产落地,预计将与DDR5、HBM4、GDDR等形成互补,共同构建更具弹性的AI内存生态,为不同层级的算力需求提供精准支撑,进一步加速人工智能技术在各行业的渗透与应用。

随着人工智能算力需求的指数级爆发,数据中心对内存的性能、容量与成本平衡提出了前所未有的严苛要求。HBM凭借1024-bit甚至2048-bit的超高位宽,成为AI加速卡的核心配套组件,其无可匹敌的带宽与能效比,支撑着大模型训练、自动驾驶等密集型计算任务的推进。

但与此同时,HBM的超高位宽设计也带来了显著短板,大量占用宝贵的芯片面积,限制了单颗芯片的堆叠数量与封装容量,进一步制约了AI加速卡的性能上限,且依赖昂贵的中介层技术,成本居高不下,难以在中高端需求场景中大规模普及。

正是在这一背景下,全球半导体标准组织JEDEC着手制定全新的“SPHBM4”(标准封装高带宽内存第四代)内存标准,试图在高性能与高性价比之间找到平衡点,为AI内存生态注入新的活力。

SPHBM4最核心的技术突破,在于通过4:1串行技术重构了数据传输架构,将传统HBM4需要的2048-bit位宽大幅缩减至512-bit,却依然能保持同等的HBM4级别带宽,且性能表现远超当前主流的DDR5内存。

相较于传统DDR系列,SPHBM4展现出碾压性的性能优势。以DDR5为例,尽管后者凭借16Gb颗粒和3200MT/s速率在消费级市场备受欢迎,但其单条容量上限仅为64GB,理论带宽也停留在819GB/s。

反观SPHBM4,借助独特的堆叠设计和TSV硅通孔技术,单颗芯片即可实现64GB容量,堆叠后容量更可突破256GB,带宽更是可以超过2TB/s。这种跨越式的提升,使得SPHBM4在面对AI集群、超算中心等高负载场景时,展现出传统内存难以企及的吞吐能力。

从市场定位来看,SPHBM4清晰地站在了DDR与HBM之间的中间地带,填补了当前内存市场的关键空白。

一方面,相较于DDR5内存,SPHBM4的带宽优势显著,能够满足AI推理、中小型模型训练等对数据传输速度有较高要求的场景,解决了DDR5在高密度计算中带宽瓶颈的问题;另一方面,与HBM4相比,SPHBM4成本更低、封装更灵活,无需承担硅中介层带来的额外开支,适合对性能有要求但无需追求极致算力的场景,比如边缘AI服务器、工业级智能设备等。

不过,这种定位也决定了SPHBM4并非万能解决方案,它不会取代GDDR显存成为显卡的新选择。原因在于,SPHBM4虽成本低于HBM4,但仍采用堆叠式设计,且需要配套的基片接口、TSV技术与先进封装工艺,成本远高于普通GDDR芯片;若用单颗SPHBM4替代多颗GDDR6/7,不仅会大幅增加显卡成本,性能提升效果却并不明显,不符合消费级显卡的成本效益逻辑。

值得注意的是,SPHBM4的落地离不开关键技术的支撑,其中TSV硅通孔技术与先进封装集成技术是核心。TSV技术能够实现芯片内部垂直方向的高效数据传输,为多Die堆叠提供稳定的连接基础,而先进封装则确保了在缩减位宽的同时,内存模块的散热效率与信号完整性不受影响。这些技术并非全新突破,但SPHBM4通过对现有技术的整合优化,实现了性能、容量与成本的协同提升,体现出JEDEC在标准制定过程中对产业实际需求的深度洞察。

对于整个内存行业而言,SPHBM4的出现并非简单的技术迭代,更标志着AI时代内存技术开始向多元化细分方向发展。未来,随着SPHBM4标准的逐步完善与量产落地,预计将与DDR5、HBM4、GDDR等形成互补,共同构建更具弹性的AI内存生态,为不同层级的算力需求提供精准支撑,进一步加速人工智能技术在各行业的渗透与应用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

热点推荐

AI大算力的存储技术, HBM 4E转向定制化

在积极配合这一客户需求。从HMB4的加速量产、HBM4E演进到逻辑裸芯片的定制化等HBM技术正在创新中发展。 HBM4 E的 基础裸片 集成内存控制器 外媒报道,台积电在近日的

基于JEDEC标准的闩锁效应测试方法

作为半导体器件的潜在致命隐患,Latch Up(闩锁效应)一直是电子行业可靠性测试的重点。今天,SGS带你深入揭秘这个“隐形杀手”,并详解国际权威标准JEDEC JESD78F.02如何通过科学的测试方法,为芯片安全筑起坚固防线。

如何制定电能质量在线监测装置的数据校验标准?

制定电能质量在线监测装置(以下简称 “监测装置”)的数据校验标准,需以 确保数据准确性、可靠性、一致性 为核心目标,结合国际 / 国内通用规范、实际应用场景(如工业、民用、电网侧)及监测装置的技术

全球首款HBM4量产:2.5TB/s带宽超越JEDEC标准,AI存储迈入新纪元

海力士 HBM4 内存的 I/O 接口位宽为 2048-bit,每个针脚带宽达 10Gbps,因此单颗带宽可高达 2.5TB/s。这一里程碑不仅标志着 AI 存储器正式迈入 “2TB/s 带宽时代

发表于 09-17 09:29

•5809次阅读

性能优于HBM,超高带宽内存 (X-HBM) 架构来了!

电子发烧友网综合报道,NEO Semiconductor宣布推出全球首款用于AI芯片的超高带宽内存 (X-HBM) 架构。该架构旨在满足生成式AI和高性能计算日益增长的需求,其32Kbit数据总线

美光12层堆叠36GB HBM4内存已向主要客户出货

随着数据中心对AI训练与推理工作负载需求的持续增长,高性能内存的重要性达到历史新高。Micron Technology Inc.(美光科技股份有限公司,纳斯达克股票代码:MU)宣布已向多家主要客户送样其12层堆叠36GB HBM4内存

Cadence推出HBM4 12.8Gbps IP内存系统解决方案

需求。Cadence HBM4 解决方案符合 JEDEC 的内存规范 JESD270-4,与前一代 HBM3E IP 产品相比,内存带宽翻了

比肩HBM,SOCAMM内存模组即将商业化

参数规模达数百亿甚至万亿级别,带来巨大内存需求,但HBM内存价格高昂,只应用在高端算力卡上。SOCAMM则有望应用于AI服务器、高性能计算、AI PC以及其他如游戏、图形设计、虚拟现实等领域。 SOCAMM利用高I/O密度和

HBM技术的优势和应用场景

近年来随着人工智能浪潮的兴起,数据中心和服务器市场对于内存性能的要求达到了前所未有的高度。HBM(高带宽内存)凭借其卓越的性能优势,如高带宽、低功耗、高集成度和灵活的架构,成为了这一领域的“香饽饽”,炙手可热。

三星电子将供应改良版HBM3E芯片

三星电子在近期举行的业绩电话会议中,透露了其高带宽内存(HBM)的最新发展动态。据悉,该公司的第五代HBM3E产品已在2024年第三季度实现大规模生产和销售,并在第四季度成功向多家GPU厂商及数据中心供货。与上一代

美光加入16-Hi HBM3E内存竞争

近日,全球DRAM内存巨头之一的美光科技公司宣布,将正式进军16-Hi(即16层堆叠)HBM3E内存市场。目前,美光正在对最终设备进行评估,并计划在今年内实现量产。 这一消息标志着美光

美光新加坡HBM内存封装工厂破土动工

光在亚洲地区的进一步布局和扩张。 据美光方面介绍,该工厂将采用最先进的封装技术,致力于提升HBM内存的产能和质量。随着AI芯片行业的迅猛发展,HBM

SK海力士加速16Hi HBM3E内存量产准备

近日,SK海力士正全力加速其全球首创的16层堆叠(16Hi)HBM3E内存的量产准备工作。这一创新产品的全面生产测试已经正式启动,为明年初的样品出样乃至2025年上半年的大规模量产与供应奠定了

美光发布HBM4与HBM4E项目新进展

近日,据报道,全球知名半导体公司美光科技发布了其HBM4(High Bandwidth Memory 4,第四代高带宽内存)和HBM4E项目的最新研发进展。 据悉,美光科技的下一代HBM

JEDEC制定全新内存标准,将取代HBM?

JEDEC制定全新内存标准,将取代HBM?

评论