文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了在柔性混合电子领域中使用的扇出晶圆级封装技术。

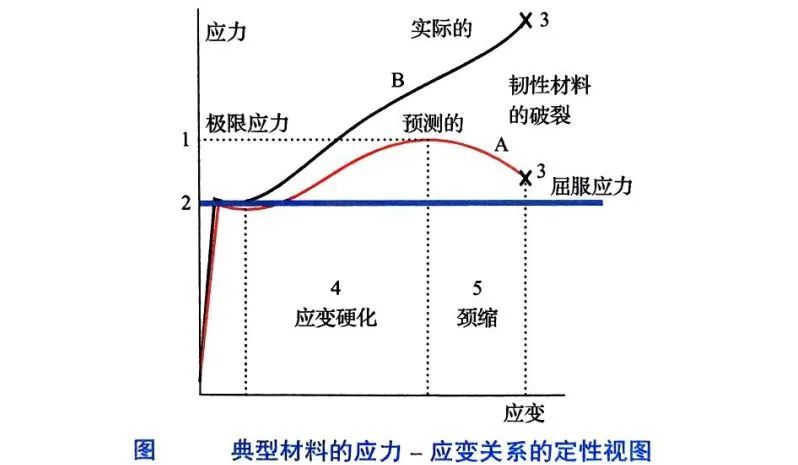

在柔性混合电子(FHE)系统中,柔性实现的难点在于异质材料的协同工作。硅基芯片、金属互连、聚合物基板等组件的弹性模量差异巨大,硅的脆性与金属的延展性形成鲜明对比,而聚合物的低模量虽有利于弯曲,却可能因黏弹性导致性能衰减。

复合体系弯曲应力的分布规律:基板与薄膜的厚度比、曲率半径共同决定薄膜中的应力水平,当弯曲半径缩小至毫米级时,硅芯片需减薄至70微米以下方可避免屈服失效,但减薄工艺本身会降低材料刚度,甚至引发DRAM数据保留时间缩短、CMOS载流子迁移率下降等电学性能退化。

这种矛盾促使转向芯片级封装(CSP)技术,通过聚合物包封为薄型芯片提供机械保护,虽牺牲了部分轻薄优势,却有效平衡了柔性与可靠性。

封装的发展

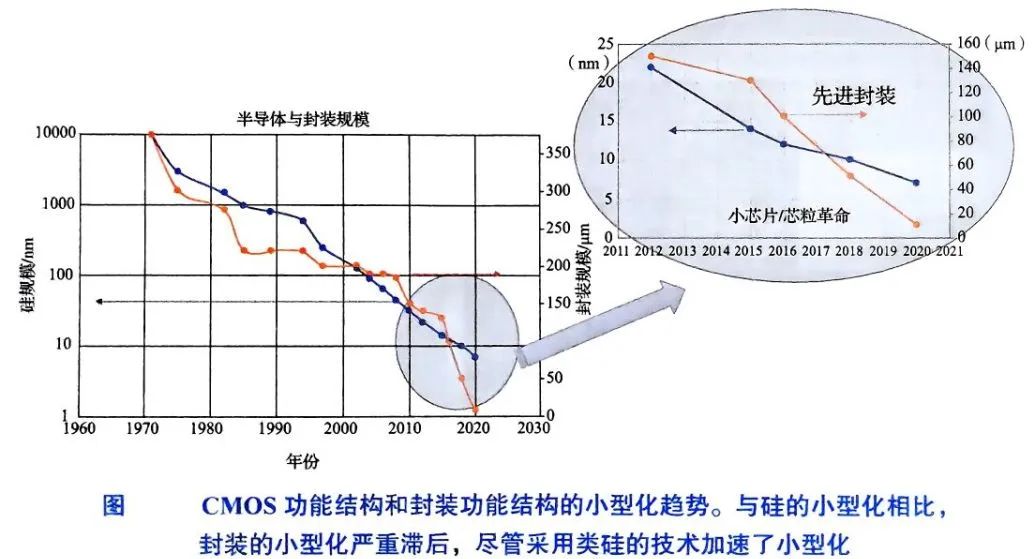

近年来,微电子领域正经历一场封装技术的深刻变革,其发展轨迹虽曾滞后于摩尔定律驱动的硅工艺缩放,但如今已呈现出加速追赶的态势。回顾历史,摩尔定律的核心在于通过晶体管尺寸的持续缩小实现集成度与性能的指数级提升,这一趋势在下图中以纳米级特征尺寸的缩放为标志,功能结构尺寸缩减超千倍,晶体管密度突破百万级。

然而,封装技术长期停留在微米级尺度,直到近年才通过技术创新实现与硅工艺的协同演进。

封装技术加速发展的驱动力主要源于两方面:其一,借鉴硅工艺的加工方法对封装材料进行精细化处理,例如硅转接板的引入,将半导体制造中的光刻、蚀刻技术应用于封装基板,实现了互连节距的显著缩小;其二,扇出晶圆级封装(FO-WLP)的成熟,该技术通过重构晶圆工艺,将芯片嵌入模塑材料后直接构建互连层,突破了传统封装中芯片与基板连接的物理限制,大幅提升了封装密度与电气性能。

扩展封装技术的重要性在于其对系统级性能的关键影响。封装尺寸通常是芯片尺寸的10至100倍,直接影响设备的整体尺寸、重量与功耗(SWaP)。尤为关键的是,芯片间通信功耗占系统总功耗的30%-40%,而封装技术的进步能有效缩短互连长度、降低信号延迟与功耗,这一提升对SWaP的优化效果远超单纯依赖硅工艺缩放。对于柔性混合电子(FHE)而言,这一变化尤为重要——FHE设备多为可移动式,依赖电池供电,封装技术的进步直接决定了其能否在保持柔性的同时,实现更紧凑的尺寸、更低的功耗与更高的集成度。

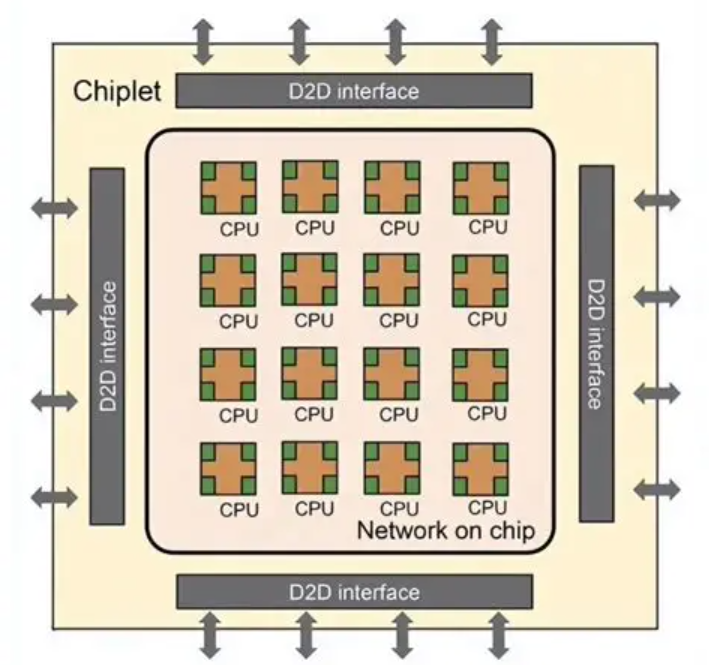

在此背景下,异构集成(HI)成为先进封装的核心特征。尽管传统封装早已通过基板集成多芯片实现“异构”,但先进封装中的HI特指一级封装层面的裸芯片直接集成,即通过有机、陶瓷或硅转接板作为基底,以超细节距(≤50μm)、短芯片间距(≤2mm)与精细布线节距(≤5μm)实现芯片间的高密度互连。这种集成方式不仅简化了信号路径,更突破了传统封装中芯片与基板连接的物理瓶颈,为高性能计算、人工智能引擎与内存模拟计算等边缘应用提供了硬件基础。

与HI紧密关联的是“小芯片”(Chiplet)与“芯粒”概念。复杂系统或大型芯片被分解为多个小型实体(小芯片),每个小芯片独立设计并实例化为芯粒,再通过细节距凸点与短间距互连重新集成为子系统或模块。这种模块化设计不仅降低了单颗芯片的制造难度与成本,更通过灵活组合实现了功能定制化——例如将高性能处理器芯粒与低功耗内存芯粒集成,满足边缘计算对能效的严苛要求。

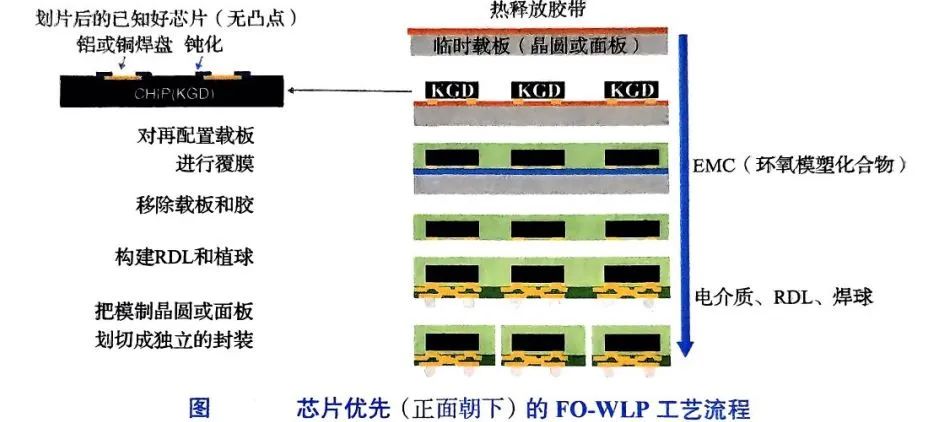

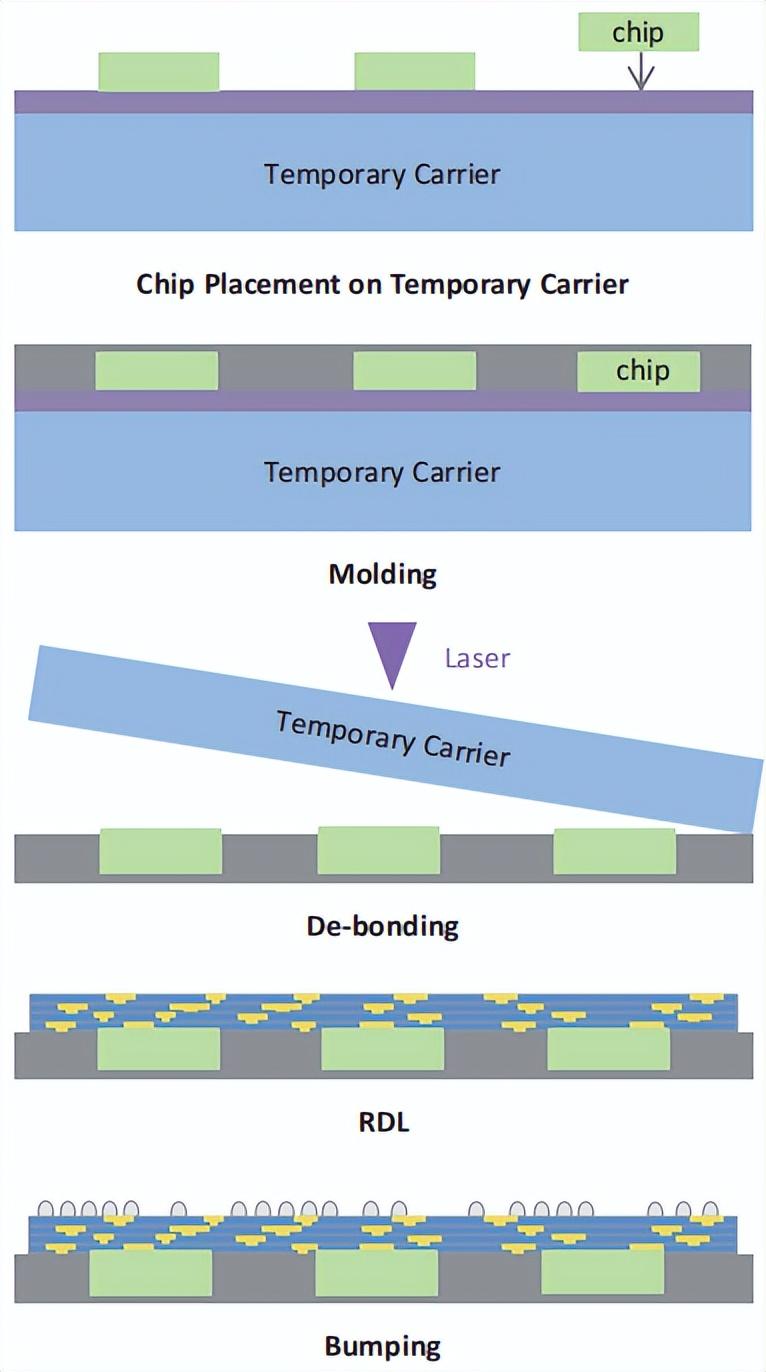

值得关注的是,扇出晶圆级封装(FO-WLP)正是实现上述扩展的关键技术路径。该技术通过模塑工艺重构晶圆,将芯片嵌入高分子材料后直接构建互连层,无需传统基板即可实现芯片间的超细间距互连。对于FHE而言,FO-WLP的优势在于其兼容柔性基材的特性——通过调整模塑材料与互连工艺,可在聚酰亚胺等柔性基板上实现细节距互连,同时保持封装整体的柔性与可靠性。此外,FO-WLP的晶圆级加工模式天然适合规模化生产,为FHE从原型走向量产提供了工艺基础。

封装技术的演进将进一步推动FHE的应用边界。随着HI、小芯片与FO-WLP的深度融合,FHE设备有望在保持柔性的同时,集成更高性能的处理器、更密集的传感器阵列与更高效的能源管理模块。这不仅将优化SWaP参数,更可能催生全新的应用场景——例如生物医学领域中,集成AI引擎的柔性可穿戴设备可实时处理本地数据,减少云端依赖;工业物联网中,柔性传感器网络可贴合复杂曲面,实现更精准的环境监测。这些变革的背后,正是封装技术从“滞后者”向“驱动者”的角色转变,为柔性电子的未来打开了无限可能。

FO-WLP的FHE—FlexTrate

FlexTrate工艺作为扇出晶圆级封装(FO-WLP)在柔性混合电子(FHE)领域的典型应用,其技术路径紧密围绕着“高密度集成”与“柔性适配”两大核心目标展开。从设计到制造的全流程,每一步都体现了对传统封装技术的突破与对柔性需求的针对性优化。

工艺的起点是系统级设计考量。与传统封装不同,FHE系统往往需要集成多类异质芯片——如传感器、处理器、无线通信模块等,这些芯片的电气特性、尺寸差异显著,因此平面布局需兼顾信号完整性、电源传输效率及热管理。设计规则检查(DRC)与布图到原理图(LVS)验证在此阶段尤为重要,尤其当芯片间距缩小至毫米级以下时,微小的布局偏差都可能导致互连失效或电磁干扰。值得关注的是,尽管异构集成(HI)的概念已被广泛讨论,但FlexTrate的独特性在于其将HI从“概念”落地为“可制造的实体”,通过细节距(≤50μm)与短芯片间距(≤2mm)的物理实现,真正实现了多芯粒在柔性基板上的紧密协作。

进入制造环节,第一层临时载板的制备是工艺的基础。选用玻璃载板的优势在于其透明性——当芯片以正面朝下的方式贴装时,光学对准系统可通过载板直接观测芯片与基板的标记,实现亚微米级的贴装精度。这种“所见即所得”的对准方式,对后续互连的可靠性至关重要。临时胶黏剂层的应用则暗含巧思:热释胶带通过温度控制实现分层,既保证了贴装阶段的粘附力,又避免了固化后难以剥离的问题。不过,胶带的表面粗糙度曾是技术瓶颈——在显示屏等对表面平整度要求极高的应用中,需额外引入平面化层以消除粗糙度对光刻工艺的影响,这体现了工艺对不同应用场景的适配能力。

芯片贴装环节的核心是精度与效率的平衡。双面红外相机系统可同时检测芯片与载板的对准标记,实现1μm级的贴装精度。这一精度不仅满足了细线宽互连的需求,更从根本上减少了后续工艺中的修正需求。值得注意的是,芯片厚度的控制(通常≤300μm)在此阶段同样关键——过厚的芯片易在压缩成型时产生应力集中,导致偏移或翘曲,而过薄的芯片则可能因机械强度不足在贴装过程中破损。

基板重构是FlexTrate工艺中最具创新性的步骤之一。选用PDMS(聚二甲基硅氧烷)作为成型材料,既利用了其柔性与生物相容性,又通过低温固化(室温24小时)显著降低了芯片偏移的风险。压缩成型过程中,特氟龙环的引入巧妙解决了基板尺寸控制的问题——通过调整环的高度与形状,可精确控制重构基板的厚度与边缘轮廓,这对后续多层金属化的堆叠至关重要。实践数据显示,通过优化PDMS的固化参数与压缩压力,芯片偏移可控制在6μm以内,这一水平已能满足大多数FHE应用的需求。

应力缓冲层的沉积是解决柔性基板与刚性金属互连矛盾的关键。PDMS表面因临时胶黏剂剥离产生的粗糙度,若直接进行光刻,易导致光刻胶开裂。通过化学气相沉积(CVD)保形涂覆聚氯代对二甲苯(一种生物相容性聚合物),并在其上旋涂SU-8层,既实现了表面的平面化,又通过复合结构的应力缓冲作用,避免了金属化层在柔性变形时的开裂。这一步骤的巧妙之处在于,它并未试图“消除”柔性基板的特性,而是通过材料与结构的协同设计,让刚性金属互连“适应”基板的柔性变形。

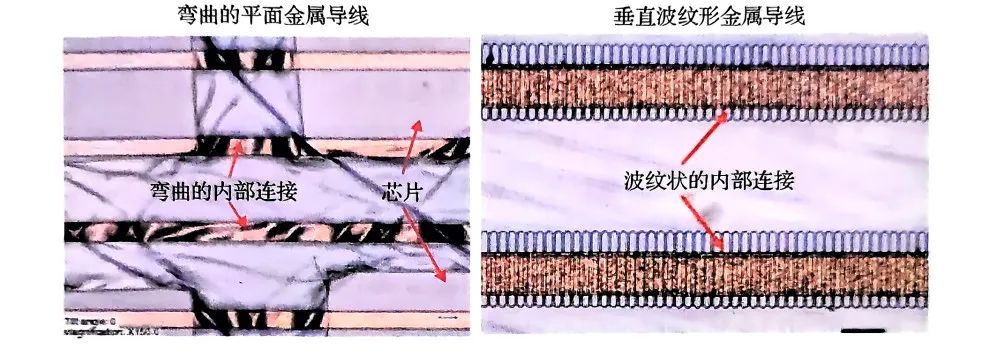

SU-8波纹结构的引入,则是针对金属导线在柔性基板上易弯曲问题的创新解决方案。当PDMS从第二层载板剥离时,其因粘附力产生的拉伸应力会突然释放,导致金属导线承受压缩应力。传统长导线在此场景下易发生弯曲甚至断裂,而通过将长导线分解为垂直波纹的短段,有效缩短了导线的有效长度,将临界弯曲应力提升了数倍。实验表明,这种波纹结构可使弯曲振幅降低5倍,显著提高了导线的机械可靠性。这一设计思想,本质上是通过“预变形”抵消后续应力,体现了对材料力学特性的深刻理解。

RDL(再分布层)制造环节,FlexTrate展现了其在高密度互连上的技术优势。通过半加成电镀(SAP)工艺,结合防反射层与基板感知掩模技术,已实现40μm节距互连,并探索了10μm以下节距的可能性。两层金属化的设计(铜/钛种子层+电镀铜),配合SU-8介质层通孔,为复杂系统(如集成AI引擎的传感器阵列)提供了足够的布线资源。值得注意的是,这种高密度互连并非单纯追求线宽的缩小,而是通过工艺优化(如电镀参数调整、光刻胶选择)在柔性基板上实现了传统刚性封装才具备的电气性能。

钝化与最终释放步骤,则聚焦于FHE的长期可靠性。聚氯代对二甲苯的CVD沉积不仅增强了基板的生物相容性(这对可穿戴设备至关重要),更通过其致密结构阻挡了水分与腐蚀性离子的渗透。在此基础上叠加氧化铝或二氧化硅无机层,进一步提升了防潮性能。最终释放时,通过精确控制热释胶带的温度(170℃),既保证了载板的顺利剥离,又避免了高温对已成型金属互连的影响。

回顾整个工艺流程,FlexTrate的成功在于其对“柔性”与“高性能”矛盾的精准把握。通过材料选择(如PDMS的柔性与SU-8的刚性)、结构设计(如波纹导线)、工艺创新(如细节距贴装与应力缓冲层),该技术实现了在柔性基板上集成高密度、高性能异构芯粒的目标。对于FHE而言,这种工艺不仅提升了系统的集成度与柔韧性,更通过降低芯片间通信功耗(占系统总功耗的30%-40%),显著优化了SWaP参数。

FlexTrate的应用

FlexTrate技术作为扇出晶圆级封装在柔性电子领域的集大成者,其应用场景的拓展正深刻改变着多个行业的技术边界。从消费级可穿戴设备到医疗植入物,从高密度显示到环境监测,这项技术通过材料创新与工艺优化,将"柔性"与"高性能"的矛盾转化为协同优势,其应用实践可归纳为五大方向,每个方向均体现了对传统电子制造范式的突破。

在可折叠显示领域,FlexTrate首次实现了毫米级弯曲半径下的可靠运行。通过将市售InGaN LED与自研硅芯片集成于0.5mm厚基板,七段式显示屏在1mm半径折叠1000次后仍保持零分层、零性能衰减。这一成就得益于40μm节距垂直波纹互连的机械强化设计——波纹结构将金属导线有效长度缩短至微米级,使临界弯曲应力提升5倍,即便在极端变形时也能避免导线断裂。更值得注意的是,LED与硅芯片的异构集成通过亚微米级对位精度实现,这种精度在柔性基板上达成,标志着封装技术从"被动适配"向"主动设计"的转型。

柔性无机uLED显示器的突破则体现在材料与工艺的双重创新。采用激光剥离(LLO)技术从蓝宝石基板转移GaN LED至FlexTrate基板,通过镍镀层缓冲应力,实现99%良率的单步转移。200PPI像素密度在5mm弯曲半径下仍保持稳定发光,证明该技术可同时满足高分辨率与柔性的双重需求。这一成果的意义不仅在于显示性能的提升,更在于其构建了"剥离-转移-集成"的全流程解决方案,为未来全彩柔性显示的大规模生产奠定了工艺基础。

无线大脑植入系统的开发则凸显了FlexTrate在生物电子领域的潜力。系统集成无线供电线圈、二极管、电容阵列与LED,通过40μm节距互连实现无焊料集成,总厚度仅535μm,直径20mm。在10mm耦合距离下,15%的功率传输效率虽低于刚性植入物,但5mm弯曲半径下的千次循环测试证明其可靠性,这为光遗传学等需要长期植入的医疗应用提供了新选择。值得注意的是,该系统的成功依赖于PDMS基板的生物相容性与应力缓冲层的协同作用——聚氯代对二甲苯与SU-8的复合结构既阻挡了体液侵蚀,又缓解了金属互连的应力集中。

个人环境监测器的案例则展示了FlexTrate在传感器集成方面的优势。通过将MEMS气体传感器与模数转换器、蓝牙模块集成于同一基板,系统厚度控制在1mm以内,重量仅5g。关键技术创新在于聚合物保护层的引入,使传感器良率从10%提升至90%,同时5V加热器电压下的300秒恢复时间与50秒响应时间,验证了柔性基板对微热管理的有效性。这种高度集成的系统设计,本质上是通过扇出工艺将分立元件转化为"系统级芯片",为可穿戴设备的小型化提供了新范式。

最后,FlexsEMG多通道表面肌电系统的开发,揭示了FlexTrate在医疗监测领域的扩展能力。20通道金包铜电极以12mm间距排布,通过40μm互连与处理芯片连接,系统总重5g,却能采集与商用Ag/AgCl电极相当的信号质量。8通道评估肌肉参数的能力,结合无线传输设计,使其在脊柱手术监测等场景中具有替代传统有线系统的潜力。这一应用的突破点在于,通过垂直波纹互连与柔性基板的结合,解决了多电极阵列的信号完整性与机械柔性的矛盾。

纵观这些应用,FlexTrate的核心价值在于其构建了"材料-工艺-设计"三位一体的创新体系:PDMS基板提供本质柔性,垂直波纹互连解决机械可靠性,细节距集成提升系统密度,而生物相容性涂层则拓展了应用边界。

这种体系化的创新,不仅推动了柔性电子从"概念验证"向"产品落地"的跨越,更预示着未来电子系统将更深度地融入人体与环境,实现真正的"人机物"三元共融。

-

芯片

+关注

关注

462文章

53592浏览量

459820 -

晶圆

+关注

关注

53文章

5349浏览量

131758 -

封装技术

+关注

关注

12文章

595浏览量

69168

原文标题:采用扇出晶圆级封装的柔性混合电子

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

采用扇出晶圆级封装的柔性混合电子

采用扇出晶圆级封装的柔性混合电子

评论