共读好书

随着铜的有效性不断降低,芯片制造商对新互连技术的关注度正在不断提高,为未来节点和先进封装的性能提升和减少热量的重大转变奠定了基础。

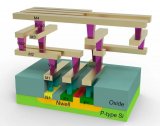

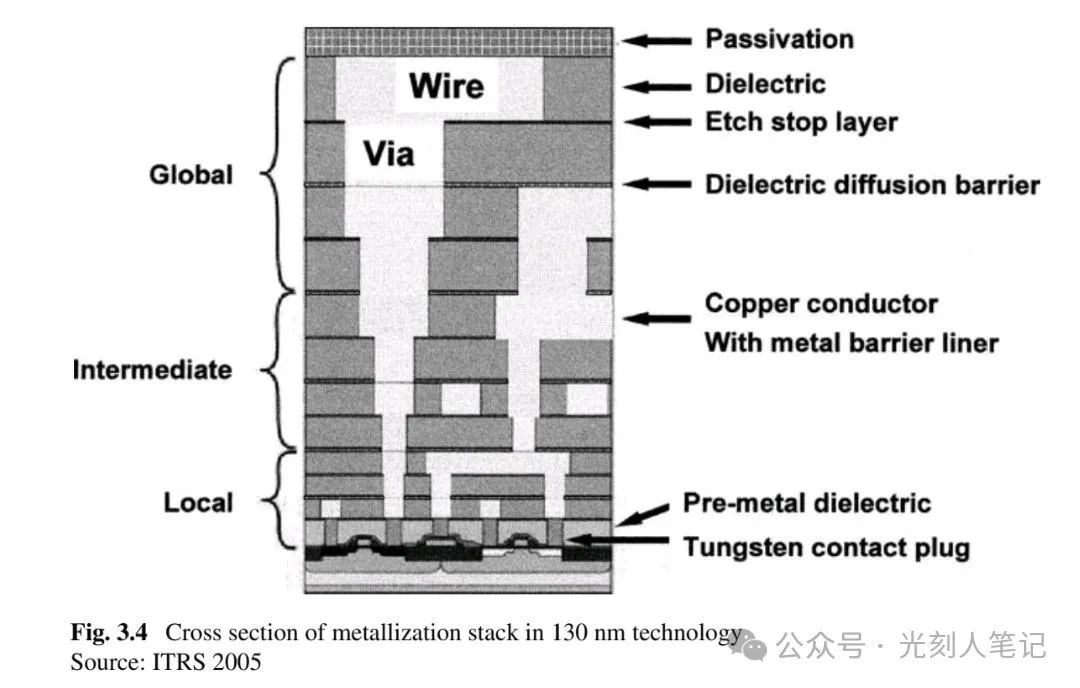

1997 年引入铜互连颠覆了当时标准的钨通孔/铝线金属化方案。双镶嵌集成(Dual damascene integration schemes )方案用电镀和 CMP 等“湿”工艺取代了等离子蚀刻和沉积等“干”步骤。当时,制造商正努力在更复杂的互连结构面前尽量减少 RC 延迟。

近三十年后,半导体行业也处在类似的十字路口。不断缩小的线路尺寸正在接近铜的电子平均自由程(electron mean free path)。阻挡层(Barrier layers)正在消耗总可用线路宽度的更大份额。对铜替代品的需求正在增长。然而,与大多数根本性变化一样,制造商希望尽可能推迟这一变化。

在最近的 IEEE 互连技术会议上公布的结果表明,铜的优化机会仍然存在。

铜互连的历史

互连线,即在晶体管之间传输电流的导线,是一个特别令人担忧的领域。随着芯片变得越来越紧密,互连线在更小的尺寸下需要承担更大的任务。在通线面世之前,铝是互连线的理想材料,也是当时的行业标准,但它的导电能力正迅速接近极限。此外,铝线更容易断裂。

铜线恰逢其会面世了。

其实大家对铝的局限在很早就知道,所有人也知道铝的时代显然已经屈指可数,但尽管经过了几十年的研究,仍然没有人找到如何安全地将铜融入芯片设计的方法。主要的障碍是克服铜与硅相互作用产生的令人不安的副产品。与铝不同,铜会有效地泄漏原子并破坏硅的电性能,从而可能导致硅无法使用。“铜被认为是半导体器件的杀手,”IBM 院士兼铜应用专家 Lubomyr Romankiw 在IBM 研究杂志中说道。“传统观点是尽可能远离铜。”

要使铜互连可行,需要解决三个问题:确定如何最好地将其化学沉积在晶圆上,如何保护硅免受毒害,以及如何在芯片上物理布置铜。

IBM 测试了几种施加铜的方法,包括从气体悬浮液中沉积固体铜,以及使用电荷将液体中的铜离子吸收到硅上,这一过程称为化学镀。虽然前一种方法(称为溅射)最初看起来很有希望,但科学家们最终选择了第三种选择,即电解镀,这是一种不切实际但很熟悉的方法——而且出人意料地成功了。

为了保护硅片,IBM 科学家采用了该公司在 20 世纪 80 年代中期研究的一种稳定金属作为阻挡杂散铜离子的扩散屏障。该公司设计了一种将扩散屏障与铜一起沉积在晶圆上的方法。研究人员借用了 IBM 在 20 世纪 80 年代初为其DRAM项目发明的一种蚀刻技术。

这项技术以叙利亚大马士革古冶金学家的名字命名,他们完善了金属镶嵌工艺,这种用于蚀刻铜互连线和通孔的所谓双镶嵌方法对该项目的成功至关重要。通过从典型制造工艺中去除沉积和抛光步骤,这种方法为寻求可行的铜解决方案创造了巨大的经济激励。

于是,到了1997 年,IBM 推出了一种由铜制成的新型半导体,震惊了世界。铜这种金属在芯片制造领域的成功应用,是科学家们 30 多年来一直未能实现的。这一突破带来了速度更快、成本更低的芯片,并为微处理器的发展开辟了新的路线图。由于铜线的耐用性更强、可靠性高出 100 倍,而且可以缩小到更小的尺寸,因此,从智能手机到汽车,铜线的替代带来了具有计算能力的设备爆炸式增长。

充分利用铜

不过,在面试近三十年后,问题凸显。

随着互连线缩小,接口及其特性与电气性能的关系比本体材料特性更密切。三星半导体高级工程师 Jongmin Baek 和他的同事专门研究了如何优化铜所需的阻挡层和蚀刻停止层来提高整体性能。例如,在接触金属间隔测试工具中(contact metal-spacer test vehicle),该团队使用侧壁等离子预处理(sidewall plasma pre-treatment )将侧壁阻挡层(sidewall barrier )厚度减少了三分之一,从而将接触电阻提高了 2%。

三星研究人员特别关注了通孔底部屏障(via bottom barrier)。由于金属通孔位于金属线上,因此不需要该屏障作为电绝缘体(electrical insulator )或扩散屏障(diffusion barrier)。它仅作为侧壁沉积的产物而存在,但它可以占通孔电阻的 60% 以上。选择性沉积方法通常用于减少通孔底部沉积。在 Baek 的工作中,聚合物抑制剂相对于常用的自组装单层提高了选择性,使电阻降低了 20%。

现代互连方案依赖于各种掺碳氧化物来实现电路 RC 延迟的“C”部分。密度较低的材料具有较低的介电常数(k),因此具有吸引力。三星的 Kang Sub Yim 的其他工作考虑了等离子蚀刻导致电介质表面碳的消耗。低 k 电介质的蚀刻损伤会增加有效介电常数,从而增加电路的电容。密度较高的材料(通常 k 值高于 3.0)对等离子蚀刻损伤的抵抗力更强,这可能使它们在 30nm 以下特征中的有效 k 值更低。对于小于约 30nm 的特征,表面碳消耗的影响大于体积介电常数。

Yim 团队还利用表面硅化来修复蚀刻损伤。然而,Baek 指出,对电介质侧壁进行表面处理可能会污染通孔底部的裸露金属。相反,Baek 团队采用了专有化学方法的热恢复工艺,将蚀刻后的 Si-OH 终止表面恢复为 Si-CH3终止表面。

铜线的完全封装(Full encapsulation)包括一个金属盖层(通常是钴)以减少电迁移,然后是绝缘蚀刻停止层和阻挡层。由于间距缩小,这些层占总线厚度的比例越来越大。为了改善与盖层的界面,Baek 在蚀刻停止层沉积之前添加了等离子体预处理。结果,他们发现铜线中的应力减少了 30%,通孔电阻减少了 10%。另外,Yim 也取得了类似的结果。

钌通孔,然后是线路

虽然所有这些发展都很有希望,但仍需要一种长期的铜后继者。由于通孔尺寸小、数量多,它正在主导整体互连电阻。在前四五个互连层中,金属线非常短,不会产生太大的电阻。因此,一种替代方案是使用过渡混合金属化方案,将铜线与钨、钌或钼等材料结合起来用于通孔。

imec的模拟表明,在互连堆栈的前四层使用钌通孔可将总电阻降低多达 60%。为了将钌通孔与铜线集成,他们建议仅在介电侧壁上沉积 TaN 阻挡层,将钌直接置于裸露的铜上。任何此类方案都需要良好的介电表面钝化和对钌选择性的良好控制。集群工具工艺是首选,因为从裸露的铜上去除原生氧化物会损坏介电钝化。

由于钌可以通过多种方式沉积或蚀刻,并且不需要阻挡层,因此它为更灵活的集成方案打开了大门。例如,imec 研发工程师 Giulio Marti 和他的同事对三种不同的完全自对准通孔工艺进行了基准测试。

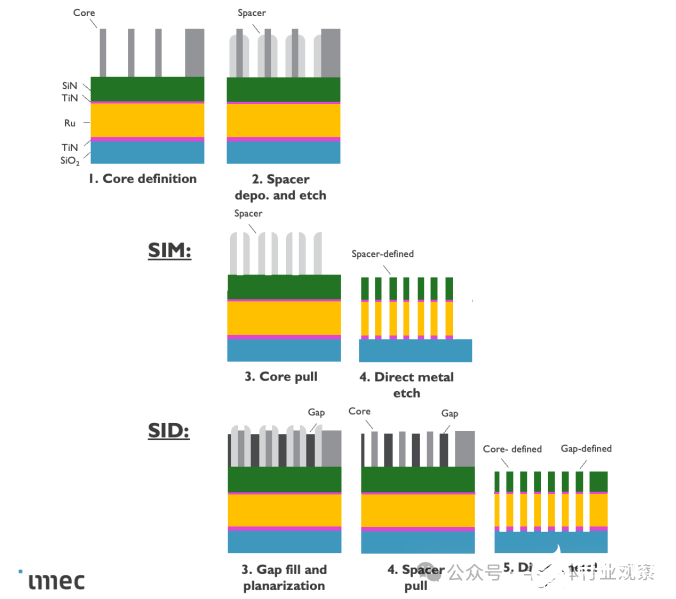

第一种也是最传统的工艺使用 EUV 自对准双重图案化,该工艺创建的间隔线用于定义金属线 (SADP-SIM)。将间隔图案转移到 SiN 硬掩模后,选择性 RIE 蚀刻对钌金属层进行图案化,然后进行 SiO2沉积。高选择性蚀刻将通孔开口与剩余的 SiN 特征对齐,然后进行 CVD 钌沉积以填充它们。

Marti 考虑的另外两种方案均基于柱通孔(pillar vias),在第一层上方沉积了第二层钌层,并用蚀刻停止层将两者隔开。在这些方案中,图案转移使用两步钌蚀刻。首先,高纵横比蚀刻在两层中切割出所需的金属线。然后,旋涂电介质填充这些沟槽,并在顶部放置硬掩模。色调反转 EUV 对硬掩模进行图案化以保护所需的通孔柱,而之前的蚀刻停止层则保护下面的金属线。Marti 发现,两个柱通孔方案增加了工艺步骤的数量,但增加了工艺窗口。特别是,这种方法可以防止通孔和相邻线之间的桥接。

另一位 imec 研发工程师 Chen Wu 及其同事提出了另一种替代方案,他们使用 SADP 间隔物(而不是金属)来定义介电特征。在这种 SADP-SID 方案中,在间隔柱之间沉积了硬掩模材料,然后将其移除。虽然这种方法增加了工艺复杂性,但这意味着金属特征直接由掩模定义,从而为设计人员提供了更大的灵活性和对特征尺寸的控制。

但无论具体方法如何,Wu强调,优化钌蚀刻和沉积工艺至关重要。锥形钌轮廓、钌特征底部的底座以及 TiN 粘附层的不完全去除会减小相邻线之间的间距,从而导致泄漏。

集成方案只是开始

成功的工艺集成方案需要仔细关注所有组件层。对于钌,优化过程才刚刚开始。杰克·罗杰斯 (Jack Rogers) 和 TEL 奥尔巴尼技术中心的同事研究了粘附层工艺条件对钌沉积行为的影响。PVD 和 ALD TiN 上的钌膜具有不同的晶粒取向、不同的晶粒取向分布和不同的电阻率。较大且更均匀的 Ru 晶粒似乎可以降低电阻率,至少当晶粒小于整体互连尺寸时是这样。

尽管钌互连所需的辅助层比铜少(这是重点的一部分),但金属蚀刻和电介质填充工艺的重新引入必将让工艺工程师在未来几年里忙碌不已。

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31279浏览量

266778 -

封装

+关注

关注

128文章

9339浏览量

149085

发布评论请先 登录

数据中心互连技术演变:光进铜退的完整路径

Co/TiN界面对钴互连电阻率的影响

MACOM公司推出高密度铜互连解决方案

如何正确选用Finisar AOC/DAC提升光互连性能

从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析

CMI500/CMI700系列铜厚测试仪的面铜探头、孔铜探头哪家好?

是德科技亮相448G全球高速铜缆创新技术与供应链大会

TSV工艺中的硅晶圆减薄与铜平坦化技术

立讯技术高速裸线技术如何抢占高速互连赛道

铜价疯涨下的连接器革命:铝代铜如何破局?

铜对芯片制造中的重要作用

从微米到纳米,铜-铜混合键合重塑3D封装技术格局

一文详解铜互连工艺

XSR芯片间互连技术的定义和优势

铜互连,尚能饭否?

铜互连,尚能饭否?

评论