文章来源:学习那些事

原文作者:小陈婆婆

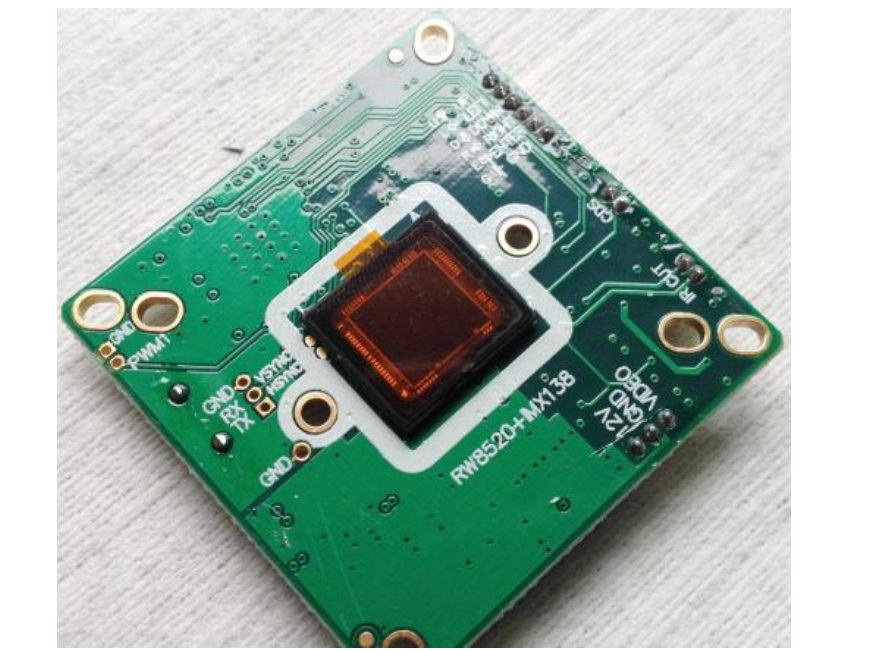

本文主要介绍CMOS集成电路基本制造工艺,特别聚焦于0.18μm工艺节点及其前后的变化,分述如下:前段工序(FrontEnd);0.18μmCMOS前段工序详解;0.18μmCMOS后段铝互连工艺;0.18μmCMOS后段铜互连工艺。

CMOS(互补金属氧化物半导体)技术自1963年由Wanlass和Sah提出以来,已发展成为半导体制造的主流工艺技术。随着硅的局部氧化工艺、离子注入技术、光刻技术等关键技术的不断发展和改进,CMOS工艺得以广泛应用,并遵循摩尔定律,持续缩小特征尺寸,提高集成度。

CMOS集成电路的基本制造工艺

前段工序(FrontEnd)

在0.18μm及以下工艺中,CMOS集成电路的前段工序主要形成器件的源漏区域。

隔离方式:

0.18μm以上:采用局部氧化(LOCOS)隔离。

0.18μm及以下:采用浅沟槽(STI)隔离,以减小隔离区的寄生电容,提高电路性能。

阱的形成:在0.18μm工艺中,阱采用倒退阱(Retrogradewell)技术,以优化器件性能。

后段工序(BackEnd)

后段工序完成器件的金属互连。

互连材料:

0.18μm以上:主要采用金属铝作为互连材料。

0.18μm及以下:虽然铝仍可用于互连,但为降低电阻率,提高电路性能,大都采用铜作为互连材料。

互连工艺:包括多层金属布线和通孔的形成,以及金属与硅之间的接触等。

0.18μmCMOS工艺的简化步骤

1.衬底准备:选择合适的硅衬底,进行清洗和预处理。

2.氧化层生长:在衬底上生长一层薄氧化层,作为后续工艺的掩蔽层。

3.光刻与刻蚀:利用光刻技术形成图形,并通过刻蚀工艺将图形转移到衬底上。

4.离子注入:根据器件需求,进行不同种类的离子注入,形成源漏区域和阱等。

5.退火:对注入的离子进行退火处理,以恢复晶格损伤并激活杂质原子。

6.STI隔离:在需要隔离的区域刻蚀出浅沟槽,并填充氧化硅等材料形成隔离区。

7.金属互连:形成多层金属布线和通孔,完成器件的金属互连。

8.钝化与封装:在器件表面形成钝化层,并进行封装处理,以保护器件并提高可靠性。

0.18μm CMOS前段工序

有源区的形成

衬垫氧化层与氮化硅层的沉积:在P型硅衬底或P型外延层上,首先通过热氧化生长一层二氧化硅(SiO₂),作为衬垫氧化层,用于缓解后续氮化硅(Si₃N₄)层与硅衬底之间的应力。接着,沉积一层氮化硅,作为硬掩模层,用于后续的刻蚀步骤。

光刻与刻蚀:使用1光刻版进行曝光和显影,去除器件隔离区域的光刻胶。随后,通过湿法或干法刻蚀,去除未被光刻胶覆盖的氮化硅、衬垫氧化层和部分硅,形成浅槽隔离(STI)的初步结构。

二氧化硅的热生长与平坦化:去除光刻胶后,通过热氧化在浅槽底部和侧壁生长一层二氧化硅,称为Roundingoxide,用于圆滑浅槽底部的尖角,减少击穿电压的降低和漏电的产生。接着,采用低压气相沉积(LPCVD)沉积一层二氧化硅,并进行致密化处理。最后,通过化学机械抛光(CMP)进行平坦化处理,确保后续工艺的顺利进行。

去除氮化硅与最终氧化层的生长:去除氮化硅层和部分二氧化硅层后,在900℃下生长一层二氧化硅,作为后续离子注入的阻挡层。

N阱和P阱的形成

N阱的形成:使用2光刻版进行曝光和显影,去除N阱区域的光刻胶。随后,进行高能大剂量磷(P)离子的注入,形成N阱。接着,以较低的能量注入砷(As),用于防止PMOS源漏之间的穿通。最后,低能量注入As,用于调节PMOS的开启电压。这种从高到低的能量与剂量分布,形成了所谓的倒退阱(Retrogradewell)。

P阱的形成:去除光刻胶后,使用3光刻版进行P阱的光刻。随后,进行高能大剂量硼(B)离子的注入,形成P阱。接着,以较低的能量注入B,用于防止NMOS源漏之间的穿通。最后,低能量注入B,用于调节NMOS的开启电压。

栅极的形成

栅氧化层的生长与多晶硅的沉积:在N阱和P阱形成后,去除氧化层并对硅片进行清洗。然后,在800℃下热生长栅氧化层。接着,沉积一层多晶硅作为栅极材料。

栅极光刻与腐蚀:使用4光刻版进行栅极光刻,通过干法腐蚀去除不需要的多晶硅,形成器件的栅极及多晶互连。

轻掺杂源漏(LDD)的形成

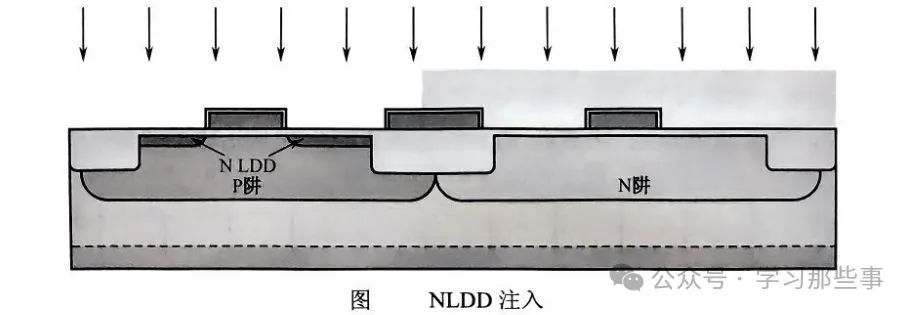

NMOSLDD的形成:在栅极形成后,进行多晶氧化,并在栅极多晶上热生长一层二氧化硅。使用5光刻版进行NMOSLDD的光刻,随后进行低能量As离子的注入,形成NMOS的轻掺杂源漏区域(NLDD)。

PMOSLDD的形成:去除光刻胶后,使用6光刻版进行PMOSLDD的光刻。接着,进行低能量B离子的注入,形成PMOS的轻掺杂源漏区域(PLDD)。由于B的扩散比As快,因此PLDD的注入能量要比NLDD的注入能量低。

Spacer的制作

沉积与腐蚀:在圆片上沉积一层TEOS(四乙氧基硅烷)作为Spacer的前驱体。随后进行各向同性的干法腐蚀,保留栅极多晶硅侧壁的TEOS,形成Spacer。

快速热退火:对注入后的LDD进行高温快速热退火(RTA),以激活注入的杂质原子并修复晶格损伤。Spacer的作用是为随后的源漏注入做阻挡,实现自对准工艺。

NMOS和PMOS源漏的形成

NMOS源漏的注入:在Spacer制作完成后,热生长一层薄氧化层作为注入阻挡层。使用7光刻版进行NMOS源漏的光刻,随后进行高能量As离子的注入,形成NMOS的源漏区域。

PMOS源漏的注入:去除光刻胶后,使用8光刻版进行PMOS源漏的光刻。接着,进行BF₂离子的注入(BF₂是B的一种化合物,用于提高PMOS源漏的掺杂浓度),形成PMOS的源漏区域。由于BF₂离子的质量较大,因此注入能量相对较低。

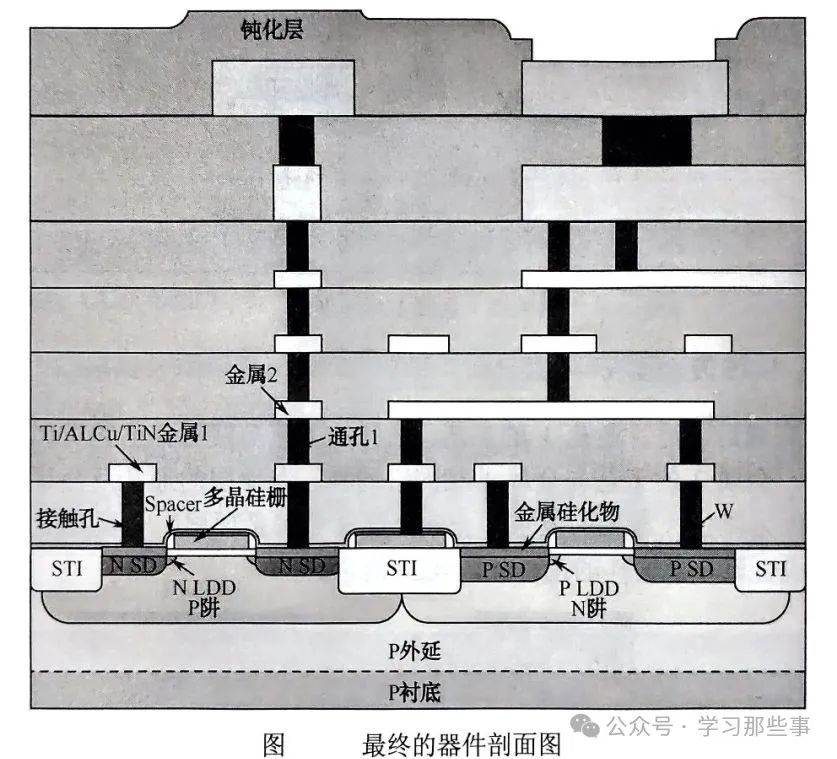

至此,0.18μmCMOS前段工序的主要步骤已完成,包括有源区的形成、N阱和P阱的制作、栅极的形成、轻掺杂源漏的形成、Spacer的制作以及NMOS和PMOS源漏的形成。这些步骤共同构成了CMOS集成电路的基本结构,为后续的后段工序(金属互连等)提供了基础。

0.18μmCMOS后段铝互连工艺

在后段铝互连工艺中,主要进行的是金属互连的制作,以下是6层铝互连的详细步骤:

接触孔(Contact)的制作

介质沉积与平坦化:首先,沉积一层TEOS(四乙氧基硅烷)作为基础介质层,随后沉积掺杂B和P的TEOS(BPSG),以提高介质的流动性和台阶覆盖率。最后,通过CMP(化学机械抛光)进行平坦化处理,使圆片表面更加平坦。

接触孔光刻与腐蚀:使用特定的光刻版进行接触孔的光刻,然后通过干法腐蚀去除未被光刻胶覆盖的介质层,形成接触孔。

接触孔填充:沉积Ti(钛)、TiN(氮化钛)和W(钨),其中Ti和TiN作为粘附层和阻挡层,W作为填充材料。通过W的CMP去除表面多余的W,只保留接触孔内的W,形成最终的接触孔结构。

第一层金属的制作

金属沉积:在接触孔制作完成后,沉积Ti、AlCu(铝铜合金)及TiN,其中AlCu作为主要的导电材料,Ti和TiN分别作为粘附层和阻挡层。

第一层金属光刻与刻蚀:使用第一层金属的光刻版进行光刻,然后通过刻蚀去除未被光刻胶覆盖的金属层,形成第一层金属的互连结构。

通孔与后续金属层的制作

通孔工艺:通孔的制作工艺与接触孔类似,用于连接不同金属层之间的电路。

金属层工艺:从第二层金属开始,每一层金属的制作都包括沉积金属、光刻、刻蚀等步骤。随着金属层数的增加,为了承受更大的电流和提供更好的散热性能,金属层的厚度也会相应增加。

最终金属层与剖片:在完成所有金属层的制作后,进行器件的剖片处理,将圆片切割成单个的芯片。

钝化与Pad的制作

钝化层沉积:在顶层金属完成后,沉积SiO₂和Si₃N₄作为钝化层,以保护芯片免受外界环境的损害。

Pad光刻与腐蚀:使用特定的光刻版进行Pad的光刻,然后通过腐蚀去除需要打引线的Pad上的钝化层,形成引线Pad区域。

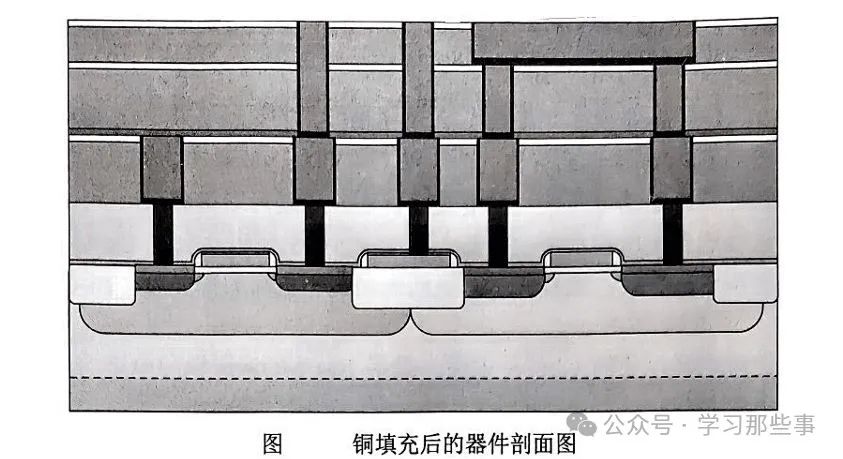

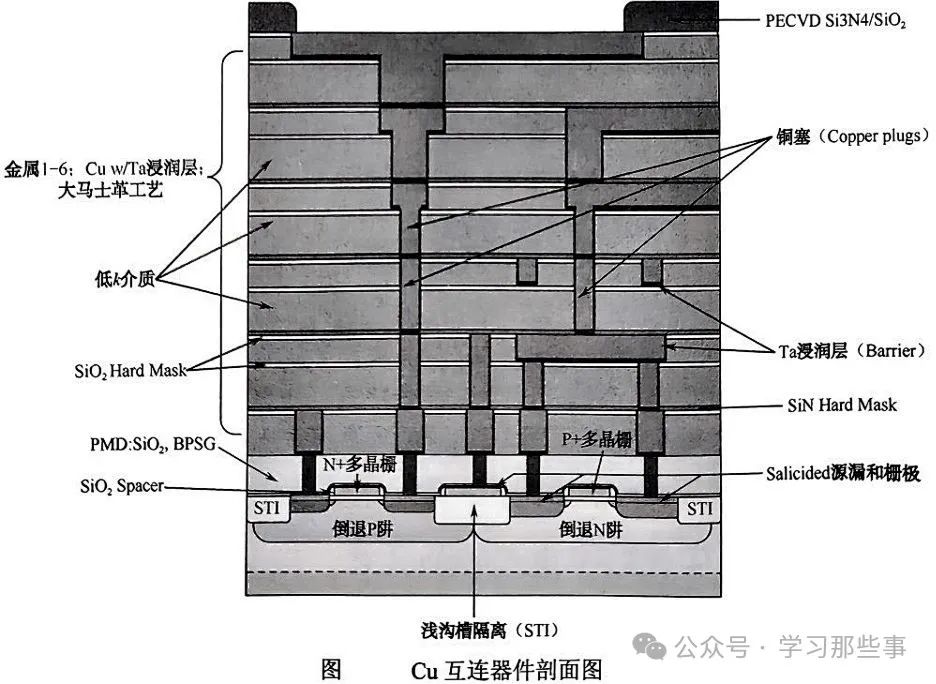

0.18μmCMOS后段铜互连工艺

与铝互连工艺相比,铜互连工艺的主要区别在于采用了铜作为金属互连材料,并使用了低k介质作为金属层间的隔离材料。以下是铜互连工艺的详细步骤:

金属前介质沉积

介质沉积与平坦化:首先沉积未掺杂的TEOS作为基础介质层,随后沉积BPSG并进行高温致密化和平坦化处理。接着再沉积一层未掺杂的TEOS作为最终的金属前介质层。

接触孔的制作

接触孔光刻与腐蚀:与铝互连工艺类似,使用特定的光刻版进行接触孔的光刻,然后通过腐蚀去除未被光刻胶覆盖的介质层。

接触孔填充:采用CVD(化学气相沉积)方法沉积一层薄的Ti和TiN作为粘附层和阻挡层,随后再沉积W进行填充。通过W的CMP去除表面多余的W,形成最终的接触孔结构。

金属层1的制作

低k介质沉积:涂覆低k介质以降低寄生电容。

金属层光刻与刻蚀:沉积SiO₂作为刻蚀的终点层,然后进行金属1的光刻和刻蚀,形成金属1填充的凹槽。

铜填充与CMP:沉积Ta作为铜的浸润层,然后采用CVD方法沉积铜填充凹槽。通过CMP去除表面多余的铜,形成金属1的互连结构。

金属层2的制作

刻蚀阻挡层与低k介质沉积:沉积SiN作为刻蚀阻挡层,然后涂覆低k介质和SiO₂作为刻蚀的终点层和填充层。

通孔与金属层光刻与刻蚀:进行通孔1的光刻和刻蚀,形成通孔结构。随后进行金属2的光刻和刻蚀,形成金属2的图形。

铜填充与CMP:采用PVD沉积Ta浸润层,然后采用CVD沉积铜填充凹槽。通过CMP去除表面多余的铜,形成金属2的互连结构。

多层金属互连与Pad的制作

后续金属层制作:金属3及其上层金属的制作过程与金属2类似,包括沉积刻蚀阻挡层、低k介质、SiO₂、光刻、刻蚀、铜填充和CMP等步骤。

钝化与Pad制作:在顶层金属完成后,采用PECVD方法沉积Si₃N₄和SiO₂作为器件的钝化保护层,再进行Pad的光刻和腐蚀处理,形成引线Pad区域。

通过以上步骤,完成了0.18μmCMOS后段铜互连工艺的全部制作流程。

-

集成电路

+关注

关注

5464文章

12669浏览量

375613 -

CMOS

+关注

关注

58文章

6229浏览量

243362 -

半导体

+关注

关注

339文章

31192浏览量

266339 -

制造工艺

+关注

关注

2文章

215浏览量

21315

原文标题:CMOS集成电路基本制造工艺

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CMOS集成电路的基本制造工艺

CMOS集成电路的基本制造工艺

评论