本文介绍了铜互连双大马士革工艺的步骤。

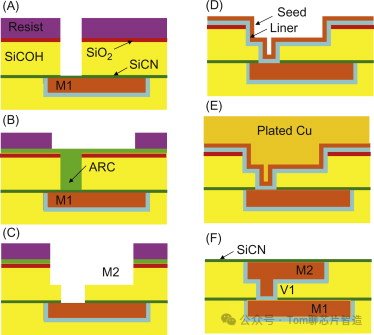

如上图,是双大马士革工艺的一种流程图。双大马士革所用的介质层,阻挡层材质,以及制作方法略有差别,本文以图中的方法为例。

(A) 通孔的形成 在介质层(如SiCOH)上沉积光刻胶(Resist),并使用光刻工艺做出掩模图形。通过干法刻蚀手段,得到通孔。

(B)制作沟槽所需的图形 完成通孔的刻蚀后,通常会去除原来的光刻胶。旋涂抗反射层,并将通孔填满,之后会再次涂布光刻胶,做出开槽所需的光刻胶图形。

(C) 开沟槽 干法刻蚀除去多余的抗反射层,介质层等,并去除晶圆表面光刻胶。

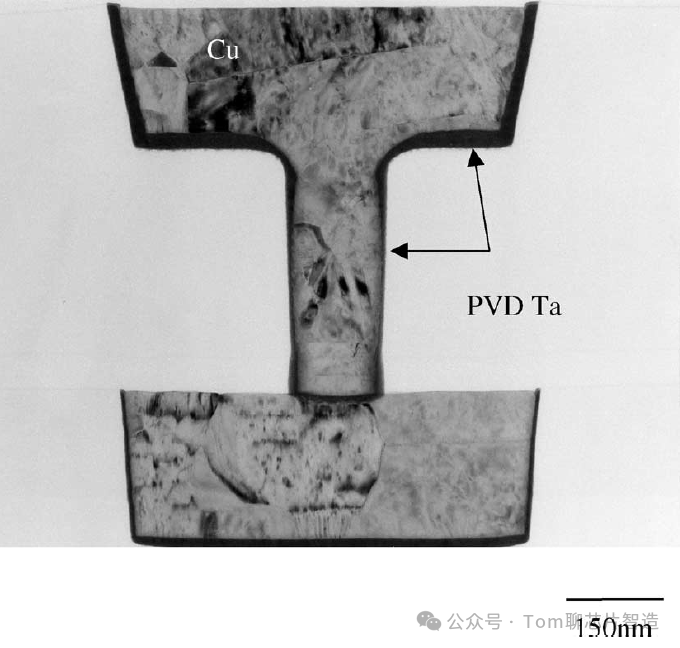

(D) 沉积种子层 在刻蚀好的沟槽和通孔内,使用PVD或CVD沉积Cu种子层和阻挡层。Cu种子层用于电镀的导电材料。阻挡层主要是Ta或TaN,用于防止铜扩散。

(E) 电镀铜 使用电镀工艺,将铜填充到通孔和沟槽中。铜完全填满后,表面会有过量的铜。使用CMP工艺去除多余的铜和种子层,只保留通孔和沟槽中的铜。

(F)cmp抛光 cmp抛光后,在表面覆盖阻挡层。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电镀铜

+关注

关注

0文章

27浏览量

9468 -

光刻工艺

+关注

关注

1文章

38浏览量

2129 -

铜

+关注

关注

0文章

3浏览量

1834

原文标题:铜互连双大马士革工艺步骤

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

一文详解铜大马士革工艺

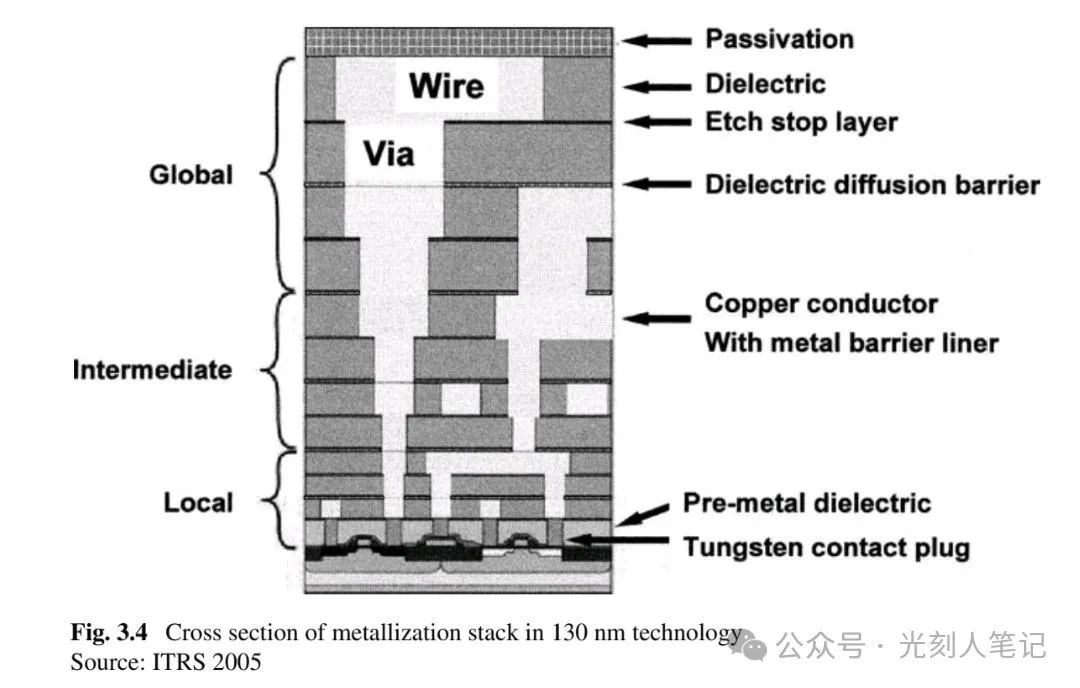

但随着技术迭代,晶体管尺寸持续缩减,电阻电容(RC)延迟已成为制约集成电路性能的关键因素。在90纳米及以下工艺节点,铜开始作为金属互联材料取代铝,同时采用低介电常数材料作为介质层,这一转变主要依赖于铜

如何采用铜互连单大马士革工艺制作超厚金属铜集成电感的概述

成功开发超厚介质膜的淀积和刻蚀工艺、超厚金属铜的电镀和化学机械研磨等工艺,采用与 CMOS 完全兼容的铜互连单

12吋晶圆集成电路芯片制程工艺与工序后端BEOL的详细资料说明

本文介绍集成电路芯片制造后端大马士革铜布线多层互联及测试等工艺。目的是科普集成电路芯片制造工艺(制程)知识,也可供第六代IGBT和汽车电子器件制造(

发表于 04-10 08:00

•46次下载

半大马士革集成中引入空气间隙结构面临的挑战

帮助imec确定使用半大马士革集成和空气间隙结构进行3nm后段集成的工艺假设 作者:泛林集团Semiverse™ Solution部门半导体工艺与整合工程师Assawer Soussou博士

发表于 12-25 14:40

•1231次阅读

通过工艺建模进行后段制程金属方案分析

及电阻率增加问题,半导体行业正在寻找替代铜的金属线材料。 l 在较小尺寸中,钌的性能优于铜和钴,因此是较有潜力的替代材料。 随着互连尺寸缩减,阻挡层占总体线体积的比例逐渐增大。因此,半导体行业一直在努力寻找可取代传统

半大马士革工艺:利用空气隙减少寄生电容

问题。为了应对这些挑战,人们提出了大马士革(semi-damascene)工艺,特别是在使用钌(Ru)作为互连材料时,这种工艺显示出了显著的优势,尤其是通过引入空气隙来减少寄生电容。

大马士革铜互连工艺详解

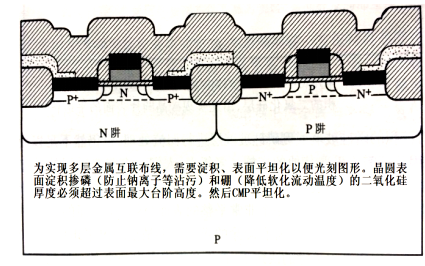

芯片制造可分为前段(FEOL)晶体管制造和后段(BEOL)金属互连制造。后段工艺是制备导线将前段制造出的各个元器件串连起来连接各晶体管,并分配时钟和其他信号,也为各种电子系统组件提供电源和接地。

芯片制造过程中的布线技术

从铝到铜,再到钌与铑,半导体布线技术的每一次革新,都是芯片性能跃升的关键引擎。随着制程进入2nm时代,传统铜布线正面临电阻与可靠性的极限挑战,而镶嵌(大马士革)工艺的持续演进与新材料的

半导体制造中大马士革工艺介绍

早期集成电路主要使用铝作为互连材料,但随着制程工艺迈入0.18微米时代,铝互连的局限性日益凸显。首先,铝与硅在577℃下会发生共熔,可能破坏浅结导致短路,即“结尖刺”现象。其次,随着导线尺寸缩小

无源TSV转接板的制作方法

无源TSV转接板作为先进封装的“交通枢纽”,是实现高密度异构集成的核心。本文深度解析TSV高深宽比刻蚀与填充工艺,详尽对比聚合物电镀与大马士革法RDL的制备差异,并拆解背面减薄、露铜及CoW组装全流程,带你攻克先进

铜互连双大马士革工艺的步骤

铜互连双大马士革工艺的步骤

评论