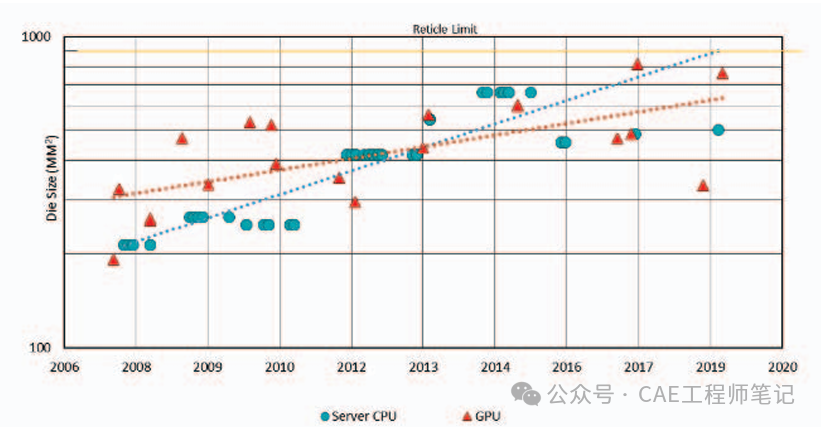

随着深度神经网络(DNN)和机器学习(ML)模型参数数量的指数级增长,AI训练和推理应用对计算资源(如CPU、GPU和内存)的需求不断增加。

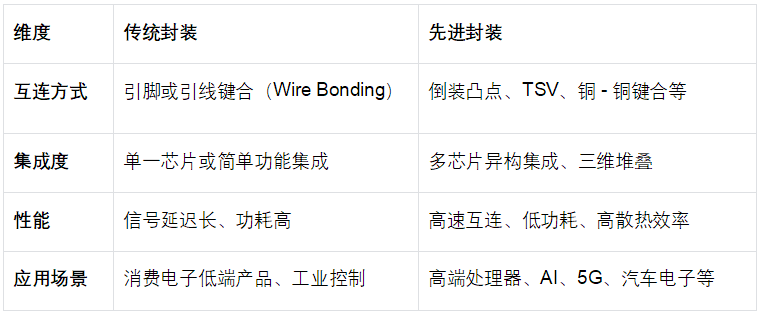

摩尔定律的放缓使得传统单片系统芯片(SoC)的性能提升受限,而芯片级架构通过将SoC分解为多个小芯片(chiplets),利用先进封装技术实现高性能和低成本。

芯片级架构通过将传统单片系统芯片(SoC)分解为多个小芯片(chiplets),利用先进封装技术实现高性能和低成本。

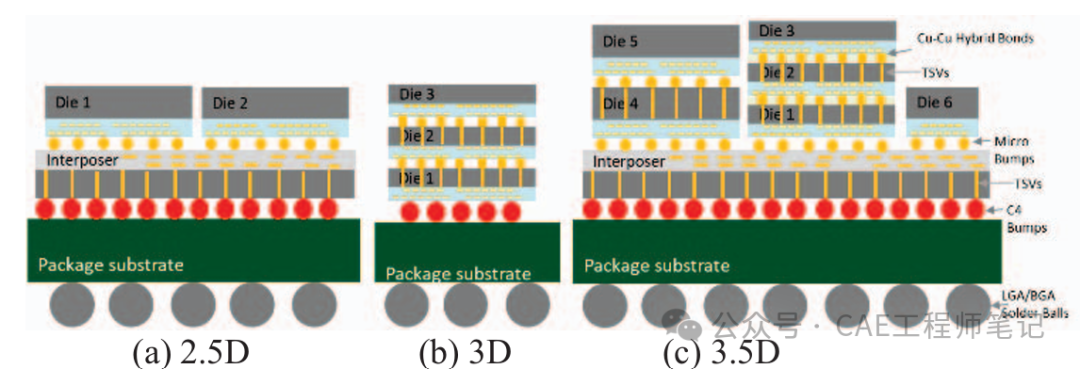

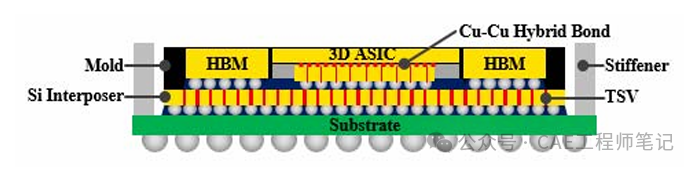

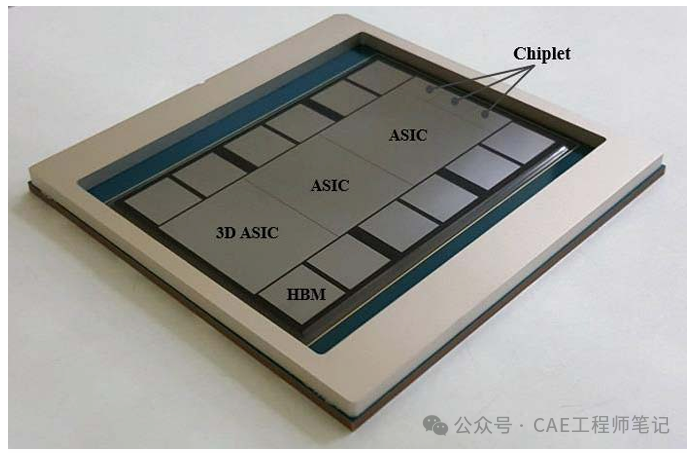

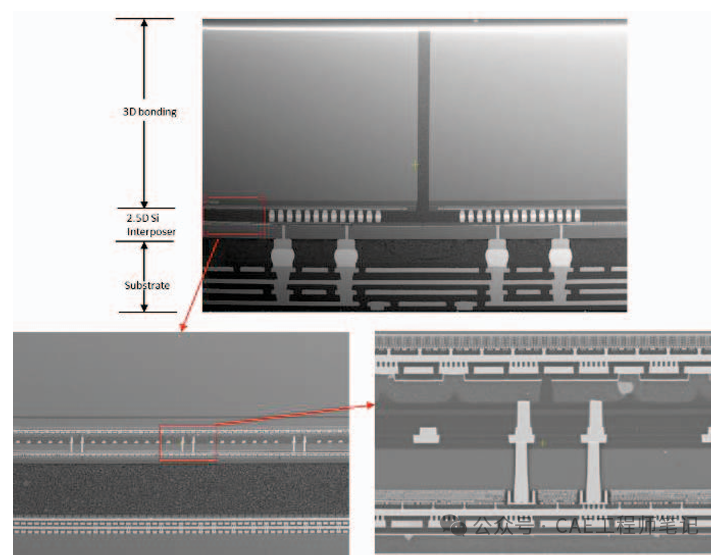

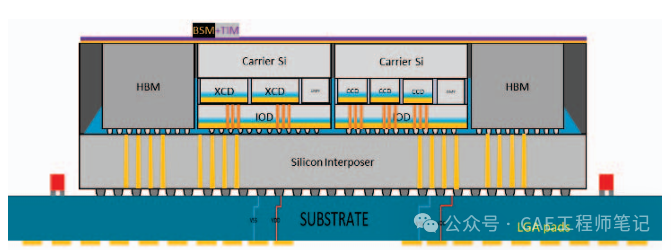

3.5D封装结合了2.5D和3D封装技术的优点,通过硅中介层将多个3D堆叠芯片(如CPU、GPU、HBM等)连接在一起。

3.5D封装技术最简单的理解就是3D+2.5D,通过垂直堆叠芯片并使用铜-铜混合键合技术,实现了更高的性能和密度,创造了一种新的架构。能够缩短信号传输的距离,大幅提升处理速度,这对于人工智能和大数据应用尤为重要。

2.5D封装:多个芯片并排放置,通过硅中介层或高密度桥接实现芯片间互连。

3D封装:多个芯片垂直堆叠,通过铜-铜混合键合或微凸点(μbump)实现互连。

3.5D创新:将3D堆叠芯片与2.5D硅中介层结合,实现更高密度的互连。

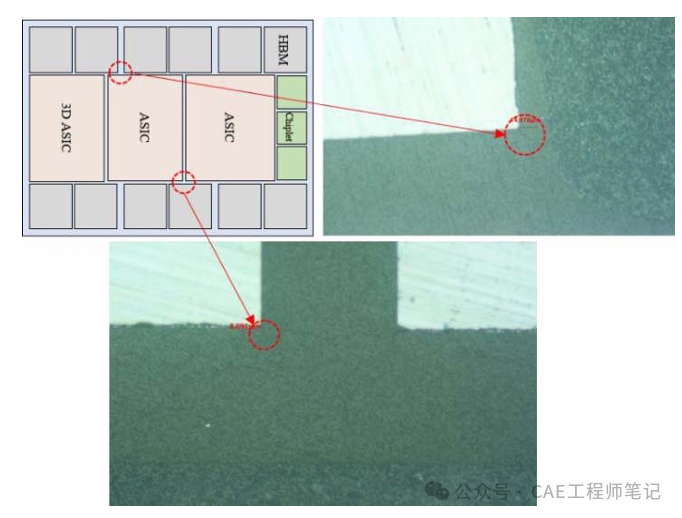

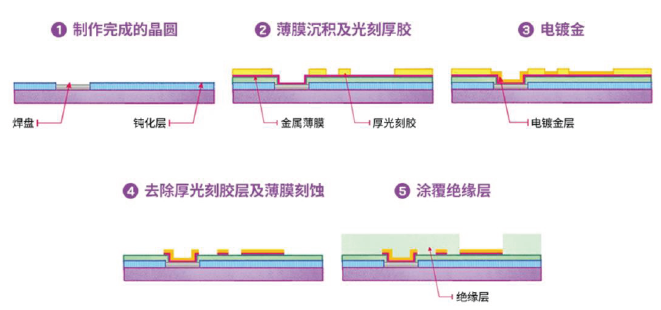

混合键合(Hybrid Bonding)技术成为关键使能者,其特点包括:

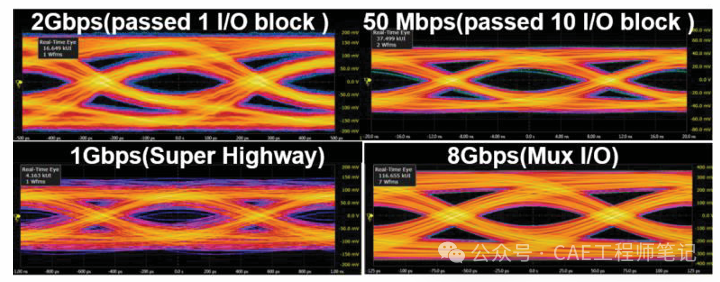

微缩互连间距:将传统40μm凸点间距缩小至1μm级

三维互连密度:单位面积互连通道提升10倍以上

热管理优化:减少界面材料层,提升散热效率

3.5D封装技术的关键优势在于:

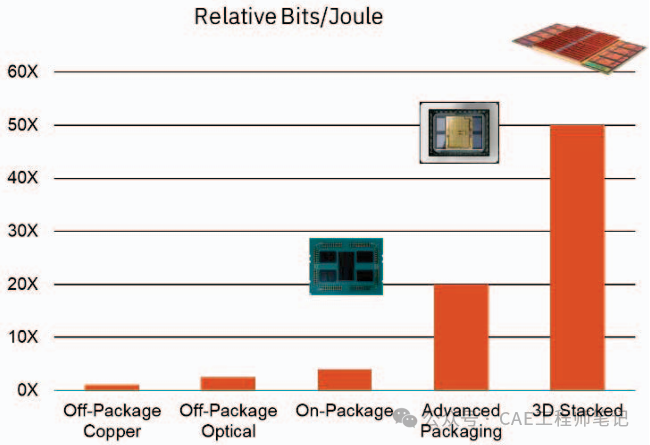

高带宽与低功耗:3D混合键合技术提供了比传统μbump互连更高的互连密度和更低的功耗。

系统级效率:通过紧密集成不同功能的芯片,减少了数据传输的延迟和功耗。

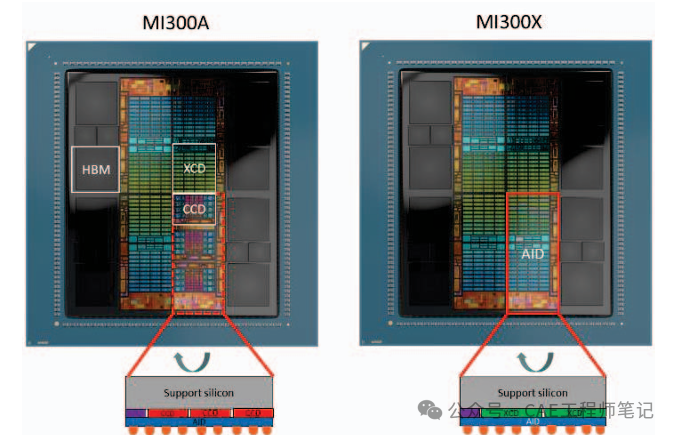

模块化设计:允许灵活配置不同的芯片组合,如MI300A(CPU+GPU)和MI300X(纯GPU)。

AMD的3.5D封装技术与AI加速器性能提升

AMD的3.5D技术通过结合2.5D和3D封装技术的优势,实现了高性能计算(HPC)和人工智能(AI)加速器的异构集成。具体来说,AMD的3.5D技术利用了以下三种关键技术来实现异构集成:

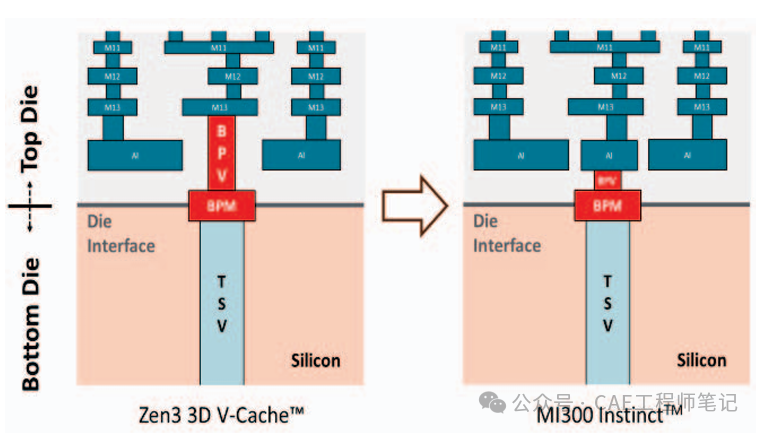

1.直接铜-铜混合键合(Cu-Cu Hybrid Bonding)

铜-铜混合键合技术是实现3D堆叠芯片之间高密度、低功耗互连的关键。AMD在MI300X Instinct加速器中使用了铜-铜混合键合技术,将多个CPU或GPU芯片垂直堆叠在一起。这种技术的主要优势包括:

高互连密度:相比传统的微凸点(μbump)技术,铜-铜混合键合可以实现更高的互连密度,从而显著提高芯片之间的数据传输速率。

低功耗:铜-铜混合键合技术能够降低互连的功耗,提高系统的能效。

低延迟:由于互连距离的缩短,数据传输延迟也相应降低。

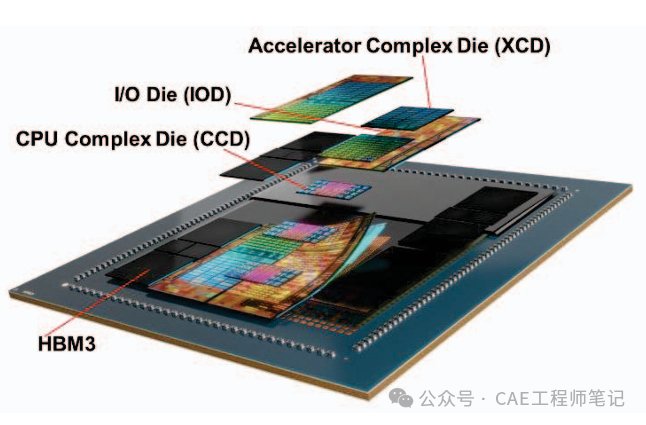

2.2.5D集成在大型硅中介层上

AMD开发了一种大型硅中介层(Silicon Interposer),用于连接多个3D堆叠芯片和其他组件。硅中介层的主要作用包括:

高带宽互连:通过硅中介层,可以实现多个芯片之间的高速互连。例如,AMD的MI300X加速器使用了2.5D硅中介层来连接3D堆叠的CPU/GPU芯片、高带宽存储器(HBM)和无源元件。

模块化设计:硅中介层允许将不同的功能模块(如CPU、GPU、HBM等)集成到一个封装中,从而实现灵活的系统设计。例如,MI300A和MI300X是两种不同的产品配置,分别针对高性能计算(HPC)和人工智能(AI)应用进行了优化。

扩展性:大型硅中介层可以容纳更多的芯片和组件,从而支持更复杂的系统集成。AMD的MI300X加速器使用了约3000mm²的硅中介层,是光刻掩模面积的3.6倍。

3.基于金属热界面材料(TIM)的冷却解决方案

为了确保高性能计算和人工智能应用中的散热需求,AMD采用了金属热界面材料(TIM)来提高散热效率。这种冷却解决方案的主要特点包括:

高效散热:金属TIM材料具有较高的热导率,能够有效传导热量,确保芯片在高负载下的稳定运行。

可靠性:金属TIM材料在高温和长时间运行中表现出良好的可靠性,能够满足高性能计算和人工智能应用的需求。

AMD的3.5D技术为高性能计算和人工智能应用提供了一种高效、灵活且可靠的解决方案,显著提升了系统的性能和能效。

高性能:通过高密度的铜-铜混合键合和2.5D硅中介层,实现了CPU、GPU和HBM之间的高速互连,显著提高了系统的性能。

高能效:铜-铜混合键合技术降低了互连功耗,提高了系统的能效。

灵活性:模块化设计允许根据不同的应用需求进行定制,如MI300A和MI300X分别针对HPC和AI应用进行了优化。

扩展性:大型硅中介层可以容纳更多的芯片和组件,支持更复杂的系统集成。

AMD的3.5D技术在AI加速器性能提升方面表现显著,主要体现在以下几个关键方面:

1.计算性能提升

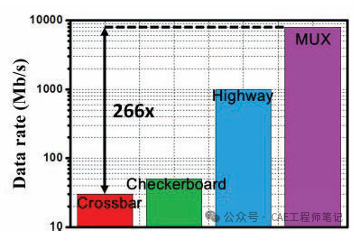

更高的互连密度:通过铜-铜混合键合技术,3.5D技术实现了比传统微凸点(μbump)技术更高的互连密度。这使得CPU、GPU和内存之间的数据传输速率大幅提高,从而显著提升了计算性能。

多芯片集成:3.5D技术允许将多个CPU或GPU芯片垂直堆叠在一起,形成3D堆叠结构。这种结构不仅提高了计算密度,还通过缩短互连距离降低了延迟。例如,AMD的MI300X加速器通过3D堆叠技术集成了多个GPU芯片,显著提升了并行计算能力。

2.内存带宽提升

高带宽存储器(HBM)集成:3.5D技术通过2.5D硅中介层将高带宽存储器(HBM)与CPU/GPU紧密集成在一起。HBM提供了极高的内存带宽,这对于AI训练和推理任务中的大规模并行数据操作至关重要。例如,MI300X加速器支持高达5324.8 GB/s的HBM3峰值内存带宽,相比上一代产品(如MI250X)提升了约62%。

统一内存架构:在MI300A加速器中,CPU和GPU共享统一的HBM内存空间,消除了传统APU中CPU和GPU使用不同内存类型导致的数据传输延迟和冗余内存拷贝问题。这种统一内存架构简化了HPC编程,提高了数据传输效率。

3.能效提升

低功耗互连:铜-铜混合键合技术不仅提高了互连密度,还显著降低了互连功耗。相比传统的μbump技术,铜-铜混合键合技术可以实现更高的能效比。

模块化设计:3.5D技术的模块化设计允许根据不同的应用需求进行灵活配置,从而在性能和功耗之间实现更好的平衡。例如,MI300A和MI300X分别针对HPC和AI应用进行了优化,以满足不同的性能和功耗需求。

4.系统级性能提升

紧密集成:3.5D技术通过将多个功能模块(如CPU、GPU、HBM等)紧密集成在一个封装内,减少了芯片之间的通信延迟,提高了系统的整体性能。

更高的计算密度:通过3D堆叠和2.5D硅中介层的结合,3.5D技术在相同的封装尺寸内集成了更多的计算资源,从而提高了计算密度和性能。

AI加速器性能提升具体数据:

矩阵FMA FP16 KOPS/CLK:MI300X加速器相比上一代MI250X加速器,矩阵FMA FP16 KOPS/CLK性能提升了2.5倍。

HBM容量和带宽:MI300X加速器的HBM容量和峰值带宽相比MI250X提升了1.5倍。

系统级性能:MI300X加速器在AI训练和推理任务中的整体性能显著提升,特别是在处理大规模并行数据操作时表现尤为突出。

AMD的3.5D技术通过高密度互连、多芯片集成、高带宽内存和模块化设计,显著提升了AI加速器的性能。具体来说,3.5D技术在计算性能、内存带宽和能效方面都取得了显著的提升,使得AI加速器能够更高效地处理复杂的AI训练和推理任务。这种技术不仅提高了系统的整体性能,还为未来的高性能计算和人工智能应用提供了强大的支持。

3.5D封装与AI训练降本

3.5D技术通过多种方式降低了AI训练的成本,主要体现在硬件设计、制造成本、功耗和运营成本等方面。

1.硬件设计与制造成本

模块化设计:3.5D技术采用模块化设计,允许将不同的功能模块(如CPU、GPU、HBM等)集成到一个封装中。这种设计不仅提高了系统的灵活性,还降低了开发和制造成本。例如,AMD的MI300A和MI300X加速器分别针对HPC和AI应用进行了优化,通过模块化设计,可以在不同的产品中复用相同的芯片模块,减少了开发成本。

小芯片(Chiplet)架构:3.5D技术通过将传统的单片系统芯片(SoC)分解为多个小芯片(Chiplet),并利用先进封装技术将它们重新连接在一起。这种架构不仅提高了性能,还降低了制造成本。小芯片可以在不同的工艺节点上制造,从而优化性能和成本。例如,某些高性能计算模块可以采用先进的工艺节点,而其他模块可以采用更成熟的工艺节点,从而在性能和成本之间实现更好的平衡。

大规模集成:通过3D堆叠和2.5D硅中介层的结合,3.5D技术在相同的封装尺寸内集成了更多的计算资源。这种大规模集成不仅提高了性能,还降低了单位计算能力的成本。例如,MI300X加速器通过3D堆叠技术集成了多个GPU芯片,显著提升了并行计算能力,同时降低了单位计算能力的制造成本。

2.功耗与运营成本

低功耗互连:3.5D技术通过铜-铜混合键合技术实现了高密度、低功耗的互连。相比传统的微凸点(μbump)技术,铜-铜混合键合技术可以显著降低互连功耗。这对于长时间运行的AI训练任务尤为重要,因为低功耗意味着更低的运营成本和更高的系统稳定性。

高能效:3.5D技术通过紧密集成和低延迟互连,提高了系统的整体能效。例如,MI300X加速器在AI训练任务中的能效比显著高于上一代产品。高能效不仅降低了功耗,还减少了散热需求,进一步降低了运营成本。

统一内存架构:在MI300A加速器中,CPU和GPU共享统一的HBM内存空间,消除了传统APU中CPU和GPU使用不同内存类型导致的数据传输延迟和冗余内存拷贝问题。这种统一内存架构不仅提高了数据传输效率,还减少了内存需求,从而降低了硬件成本。

3.系统级优化

紧密集成:3.5D技术通过将多个功能模块(如CPU、GPU、HBM等)紧密集成在一个封装内,减少了芯片之间的通信延迟,提高了系统的整体性能。这种紧密集成不仅提高了性能,还减少了系统复杂性和维护成本。

高性能与高密度:通过3D堆叠和2.5D硅中介层的结合,3.5D技术在相同的封装尺寸内集成了更多的计算资源,从而提高了计算密度和性能。这种高性能和高密度的集成不仅提高了系统的整体性能,还减少了数据中心的物理空间需求,降低了数据中心的建设和运营成本。

快速上市时间:3.5D技术的模块化设计和小芯片架构允许快速开发和部署新的产品,从而缩短了产品上市时间。快速上市时间不仅提高了市场竞争力,还降低了开发和运营成本。

3.5D技术通过模块化设计、小芯片架构、低功耗互连、高能效设计和系统级优化,显著降低了AI训练的成本。具体来说,3.5D技术在硬件设计、制造成本、功耗和运营成本方面都取得了显著的提升,使得AI加速器能够更高效地处理复杂的AI训练任务。这种技术不仅提高了系统的整体性能,还为未来的高性能计算和人工智能应用提供了强大的支持。

采用3.5D封装架构创新不仅延续了摩尔定律的经济效益,更开创了"超越摩尔"的新技术路径,为下一代计算平台提供核心支撑。

-

soc

+关注

关注

40文章

4626浏览量

230212 -

先进封装

+关注

关注

2文章

563浏览量

1062

原文标题:先进封装技术(Semiconductor Advanced Packaging) - 20 3.5D封装、AMD、AI训练降本

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

绕开先进制程卡脖子:2026先进封装成中国AI芯片自主突围关键一战

半导体先进封装之“2.5D/3D封装技术”的详解;

先进封装成破局,博通率先落地3.5D,6000mm²超大集成

先进封装时代,芯片测试面临哪些新挑战?

3D-Micromac CEO展望2026半导体:AI 为核,激光微加工赋能先进封装

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

从 2D 到 3.5D 封装演进中焊材的应用与发展

先进封装技术:3.5D封装、AMD、AI训练降本

先进封装技术:3.5D封装、AMD、AI训练降本

评论