引言

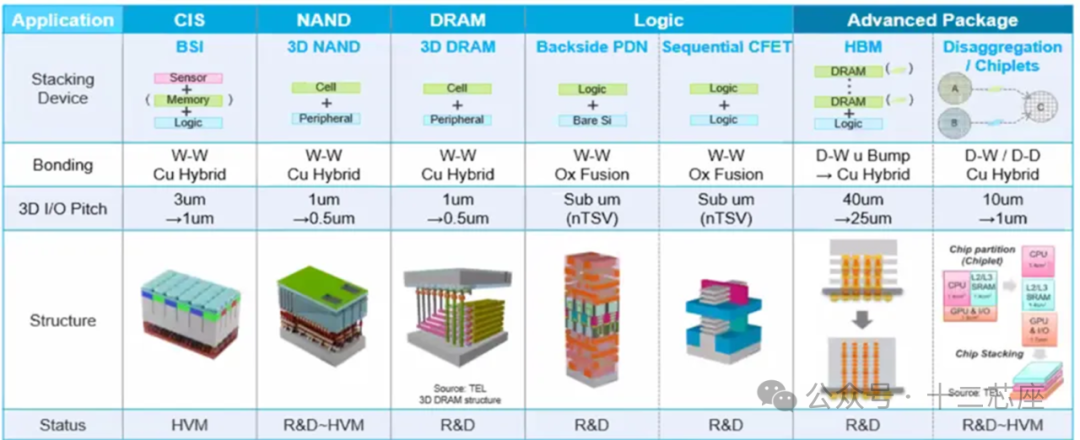

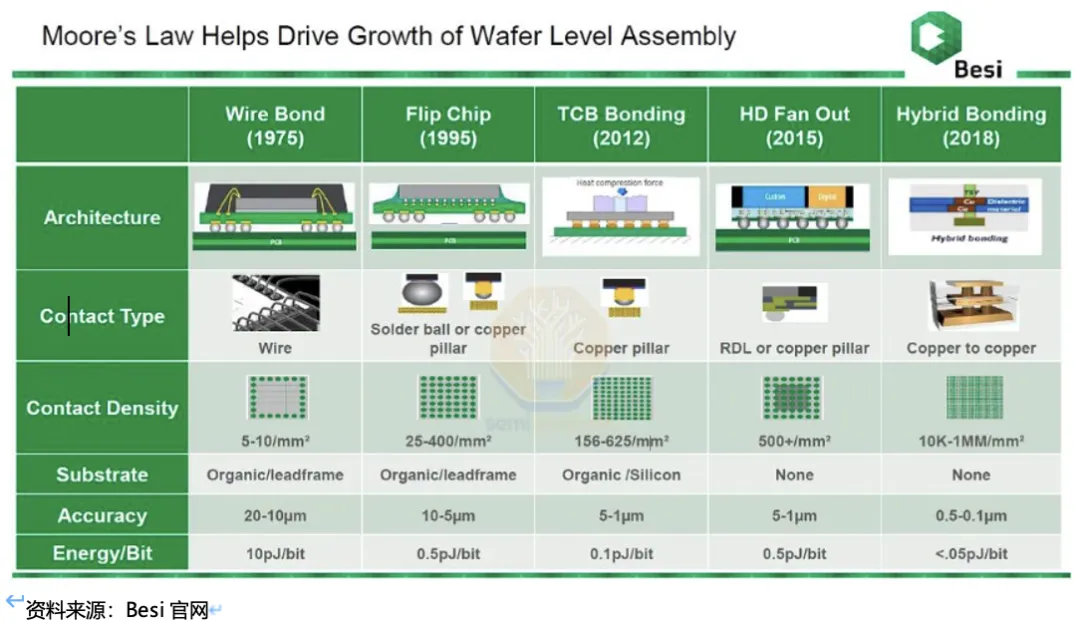

Cu-Cu混合键合(Cu-Cu Hybrid Bonding) 技术正在成为先进3D集成的重要技术,可实现细间距互连和高密度芯片堆叠。本文概述了Cu-Cu混合键合的原理、工艺、主要挑战和主要行业参与者的最新进展[1]。

Cu-Cu混合键合技术简介

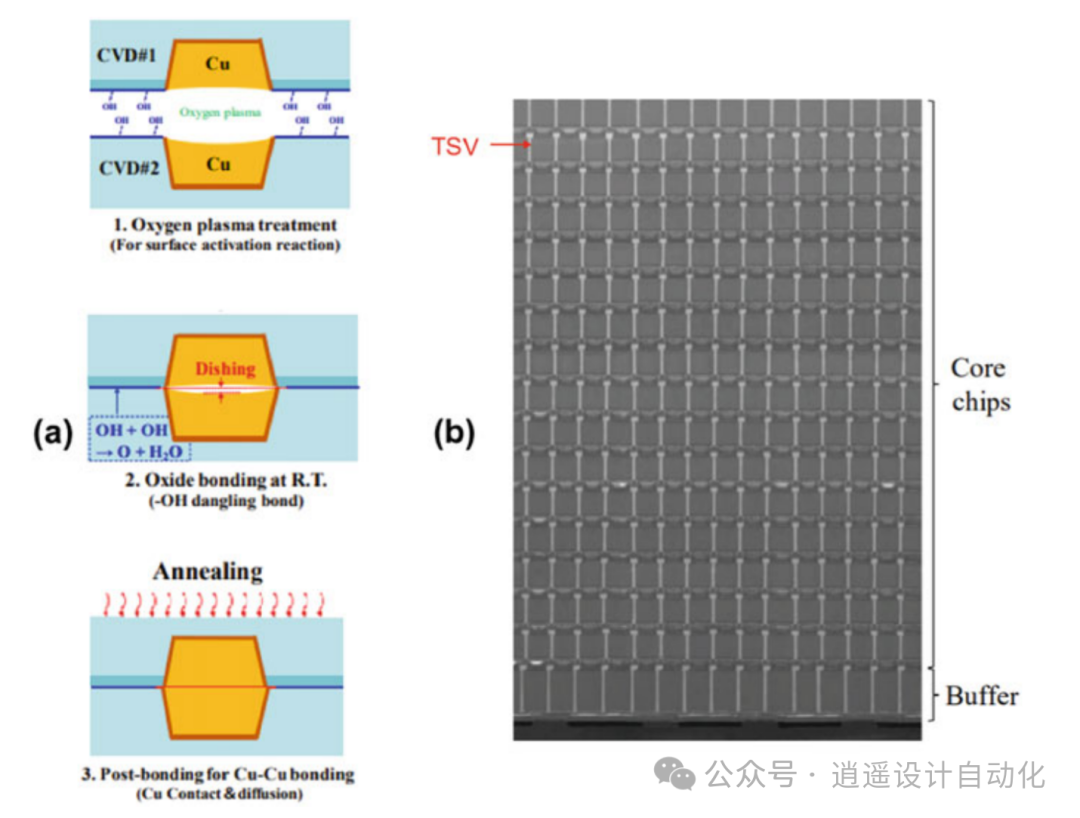

Cu-Cu混合键合是芯片堆叠技术,结合了Cu-Cu金属键合和介电-介电键合,通常是氧化物-氧化物键合。工艺通常包括以下关键步骤:

对Cu焊盘和介电表面进行化学机械抛光(CMP)

表面活化,通常使用等离子体处理

介电表面在室温下键合

退火以促进Cu-Cu互扩散并形成强金属键

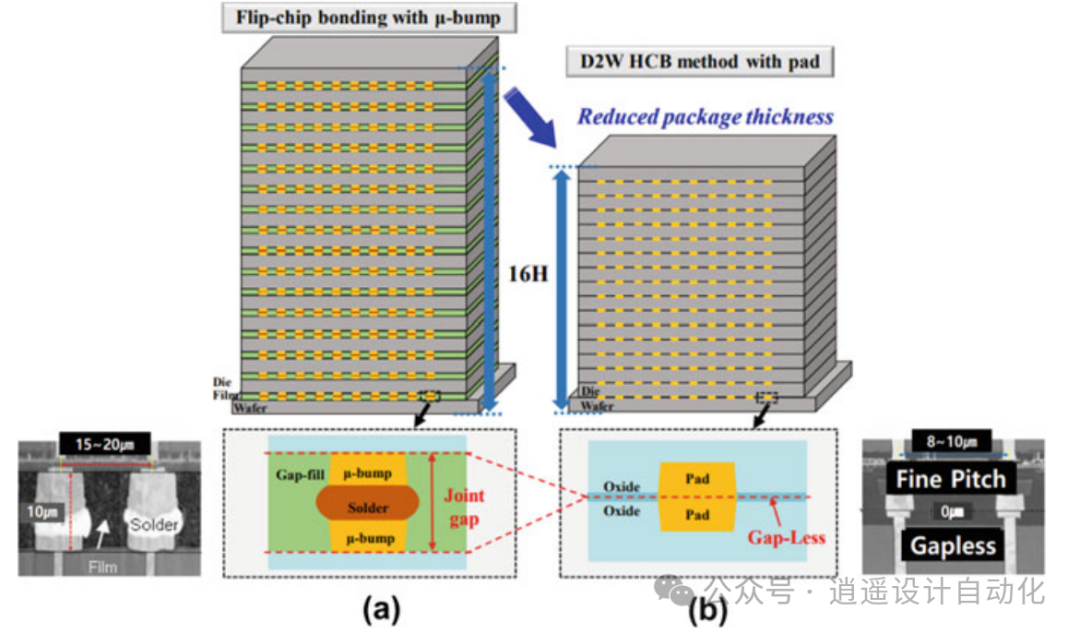

与使用焊料凸点的传统倒装芯片键合相比,Cu-Cu混合键合具有以下优势:

更细的间距(亚微米)互连

更好的散热性能

更薄的封装厚度

图1:(a)倒装芯片焊料回流和(b)Cu-Cu混合键合的16H HBM结构对比。混合键合方法实现了更薄的封装,芯片之间无间隙连接。

关键工艺步骤和挑战

表面准备

获得超平滑和清洁的键合表面对成功实现混合键合很重要。化学机械抛光(CMP)用于使Cu焊盘和介电表面平坦化。精确控制Cu凹陷(凹陷)很重要 - 通常只允许几纳米的凹陷。

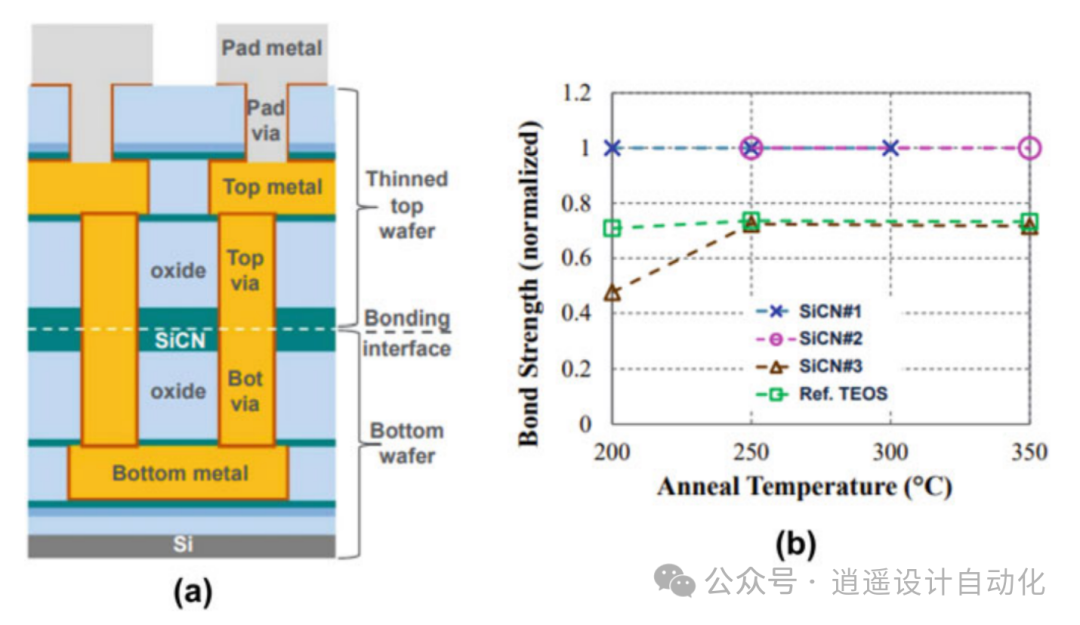

图2:使用SiCN作为键合层的晶圆对晶圆混合键合集成流程。CMP用于在键合前使表面平坦化。

表面活化

等离子体处理通常用于在键合前活化介电表面。这在表面上创建反应性羟基(OH)基团,以实现室温键合。需要优化等离子体条件以获得高键合强度。

图3:关键的混合键合工艺步骤,包括通过等离子体处理进行表面活化,以创建羟基基团实现室温键合。

室温键合

将活化的晶圆或芯片在室温下接触,使介电表面形成初始键合。精确对准对细间距互连尤为关键。

退火

键合后退火,通常在200-400°C下进行,使Cu原子能够跨键合界面扩散,形成强金属-金属键。需要优化退火条件,以实现良好的Cu键合,同时避免空洞形成等问题。

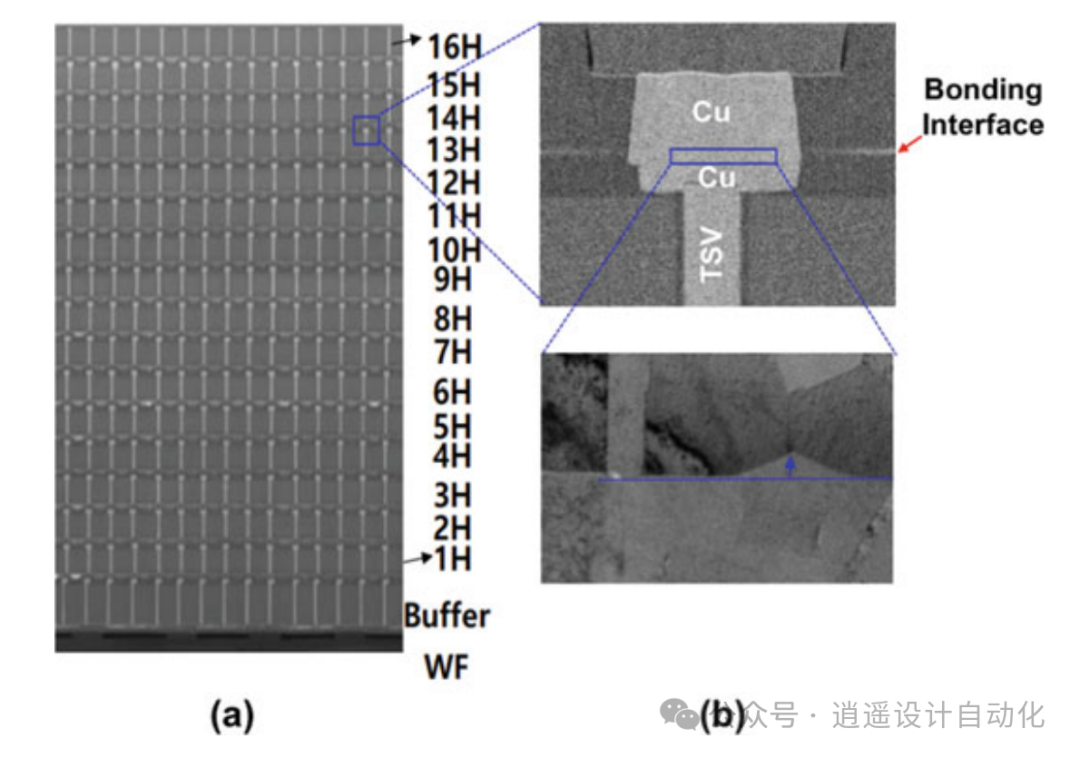

图4:(a)16H HBM整体结构和(b)退火后Cu-Cu界面的横截面SEM图像,显示跨键合界面的重结晶Cu晶粒。

主要挑战

Cu-Cu混合键合的主要挑战包括:

实现并维持超清洁的键合表面

精确控制Cu凹陷/凹陷

优化等离子体活化以获得高键合强度

精确对准,特别是对于细间距

键合界面处的空洞/缺陷控制

某些应用的热预算限制

主要参与者的最新进展

三星一直在积极开发用于高带宽内存(HBM)应用的混合键合技术。已经展示了使用混合键合的16H HBM堆叠。

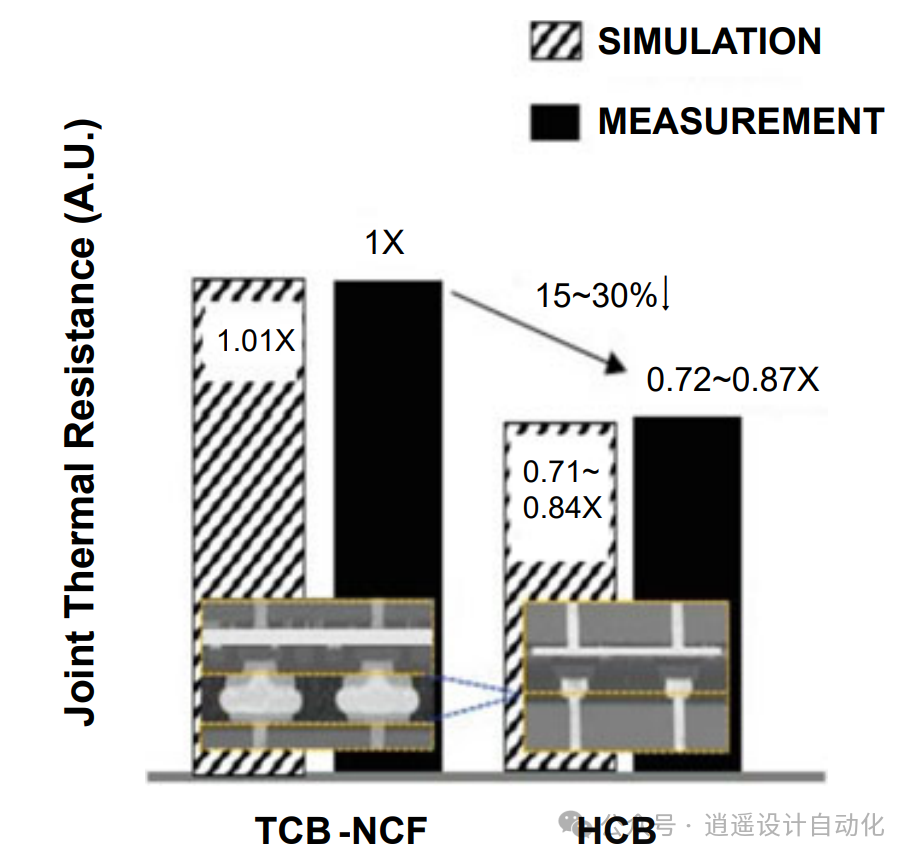

图5:使用TCB-NCF和混合键合方法的16H HBM堆叠热阻对比。混合键合方法显示出15-30%较低的热阻。

三星还提出了新型结构,如键合界面处的Cu-Cu布线,以进一步改善电气和热性能。

SK海力士

SK海力士也在追求用于HBM的混合键合。已经展示了使用芯片对晶圆(C2W)混合键合的8Hi HBM堆叠。

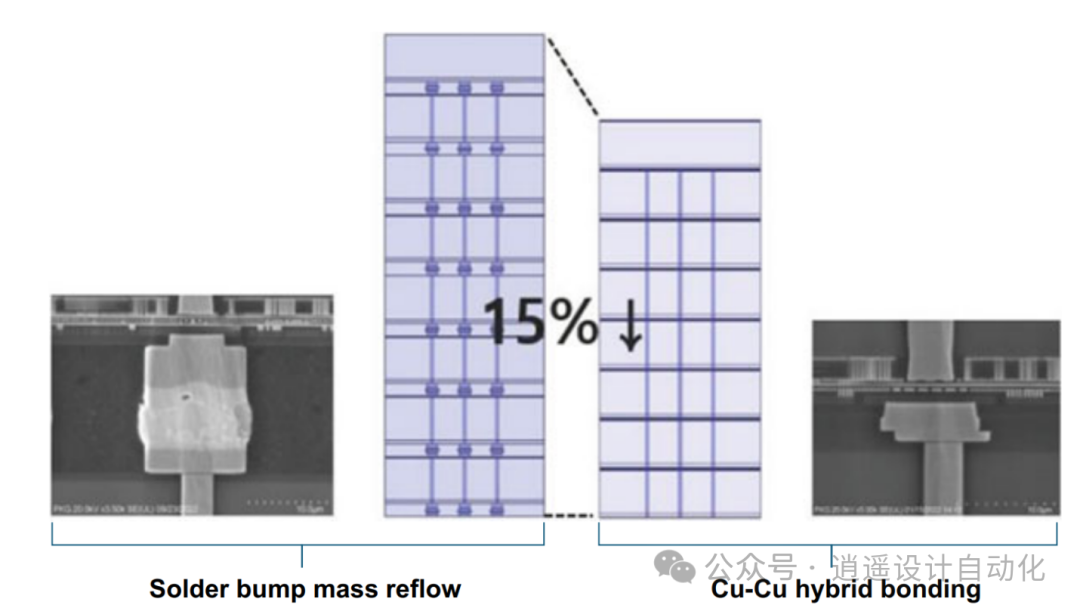

图6:8Hi HBM的焊料凸点倒装芯片和混合键合互连结构对比,显示使用混合键合可减少15%的厚度。

SK海力士的工作集中在优化等离子体处理和键合条件,以实现高键合强度和低空洞密度。

美光

美光正在开发用于HBM和潜在3D DRAM应用的混合键合。他们强调了几个关键挑战,包括:

晶圆切割后的颗粒控制

传统晶圆支撑系统的限制

需要更高温度的退火

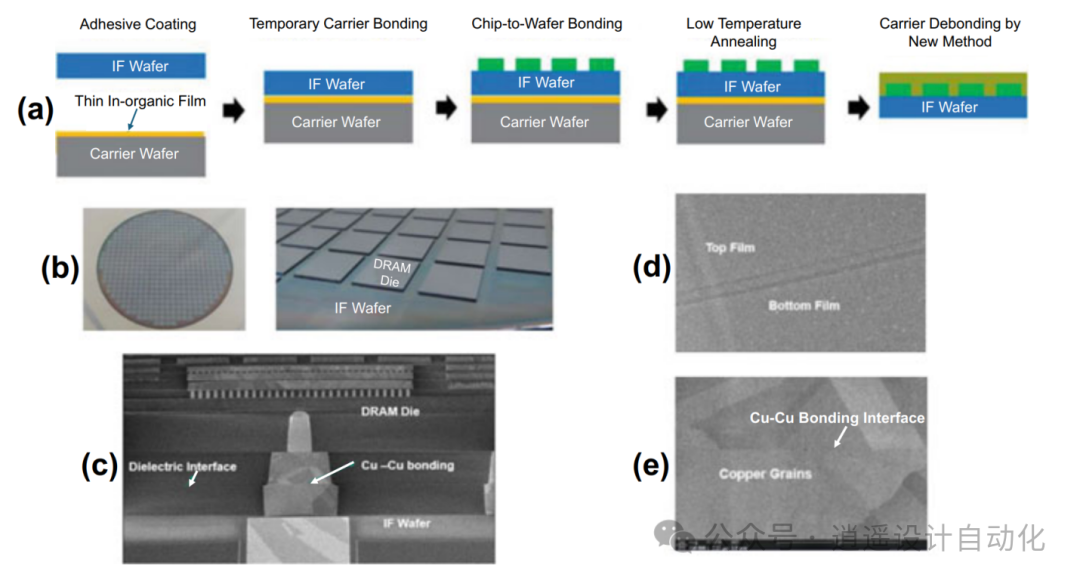

图7:美光的新晶圆支撑系统(WSS)工艺,可实现更高温度退火,提高混合键合质量。

索尼

作为CMOS图像传感器混合键合的早期采用者,索尼继续推进该技术。最近的工作集中在:

大尺寸(>400 mm2)芯片对晶圆键合

细间距(6 μm)互连

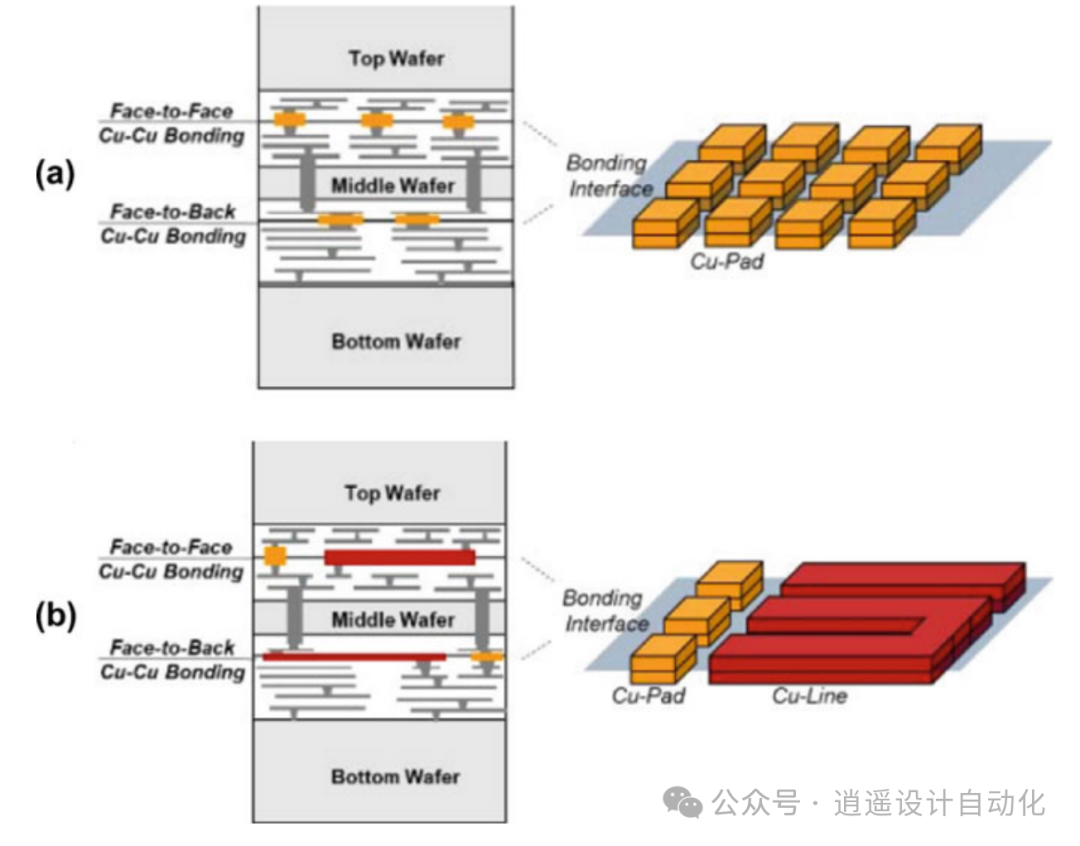

新型结构,如界面处的Cu-Cu布线

图8:索尼在键合界面处的新型Cu-Cu布线结构,除了电气接触外,还可将Cu图案用作互连。

应用材料

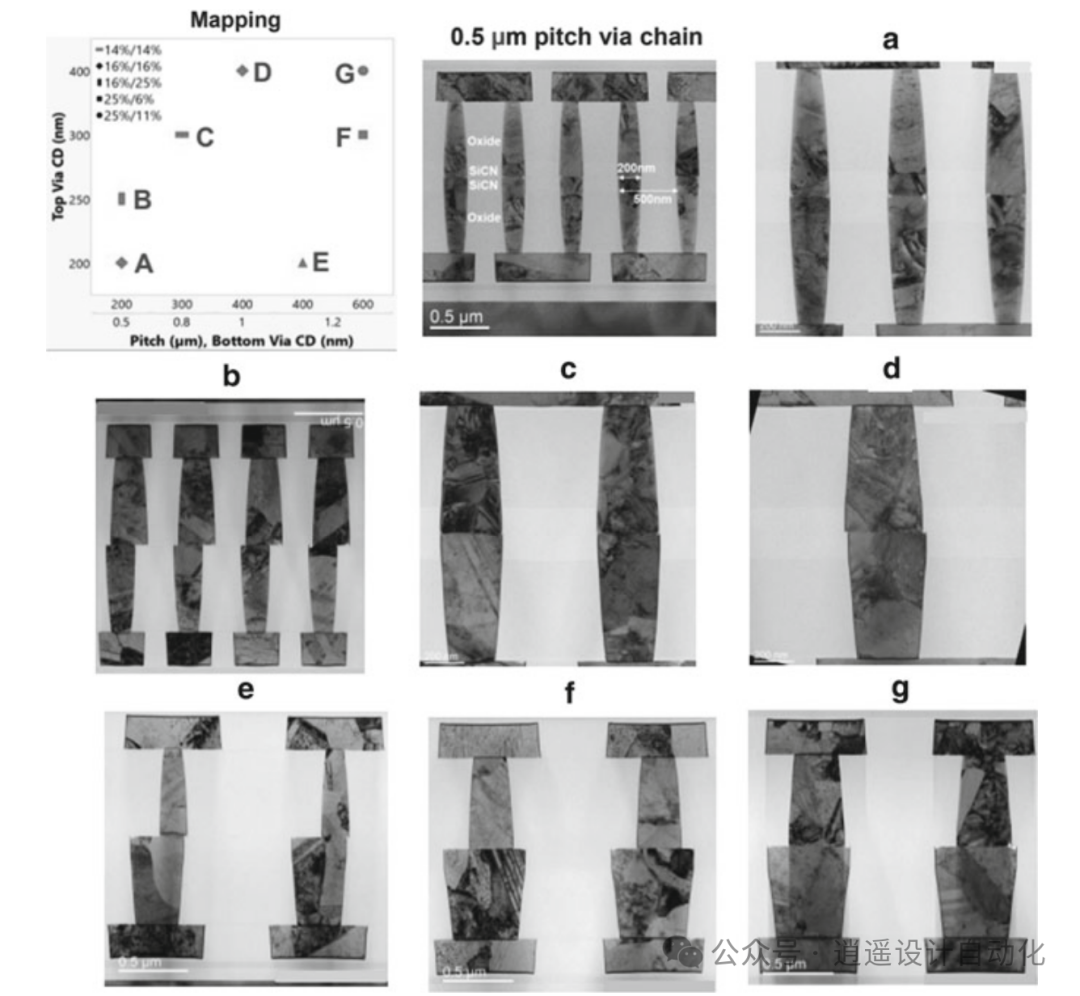

作为主要设备供应商,应用材料正在开发先进节点的混合键合工艺和工具。最近的工作展示了:

0.5 μm间距的晶圆对晶圆键合

使用SiCN作为键合介电材料

Cu凹陷控制在<2-3 nm

图9:应用材料公司展示的各种特征尺寸和间距(小至0.5 μm)的混合键合结果TEM图像。

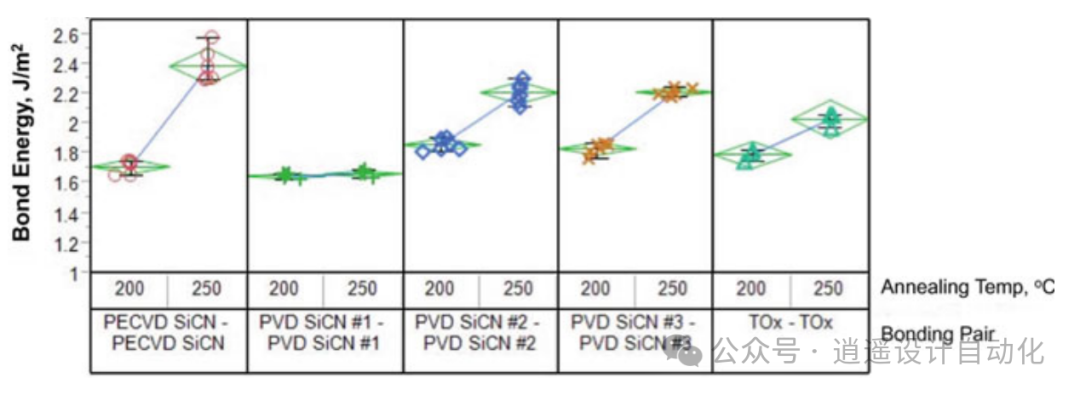

英特尔正在研究混合键合作为其先进封装路线图的一部分。最近的工作集中在:

用于键合介电的低温SiCN薄膜

表面活化效果的表征

键合强度优化

图10:英特尔研究中各种SiCN-SiCN键合界面和退火温度的键合能量(强度)结果。

台积电

台积电正在其SoIC(集成芯片系统)平台下开发混合键合。正在推进芯片对晶圆(SoIC-X)和晶圆对晶圆(SoIC-CoWoS)方法。

最近的工作集中在:

热管理优化

TSV与键合焊盘直接连接

超薄键合膜

图11:台积电SoIC平台中背面键合界面电气-热协同优化方法。

新兴研究方向

正在追求几个有趣的研究方向,以进一步推进混合键合技术:

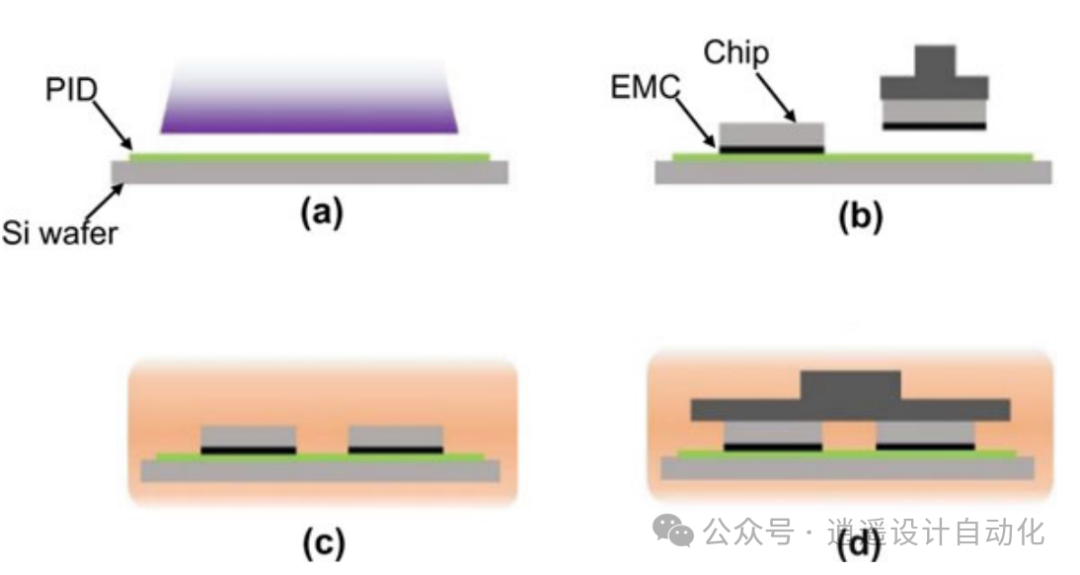

1. 新型键合材料

虽然SiO2和SiCN是常见的键合介电材料,但也在研究其他材料。例如,Resonac提出使用环氧模塑料(EMC)和光敏性介电材料(PID)等有机材料进行混合键合。

图12:Resonac使用EMC芯片和PID晶圆进行混合键合的热键合工艺。

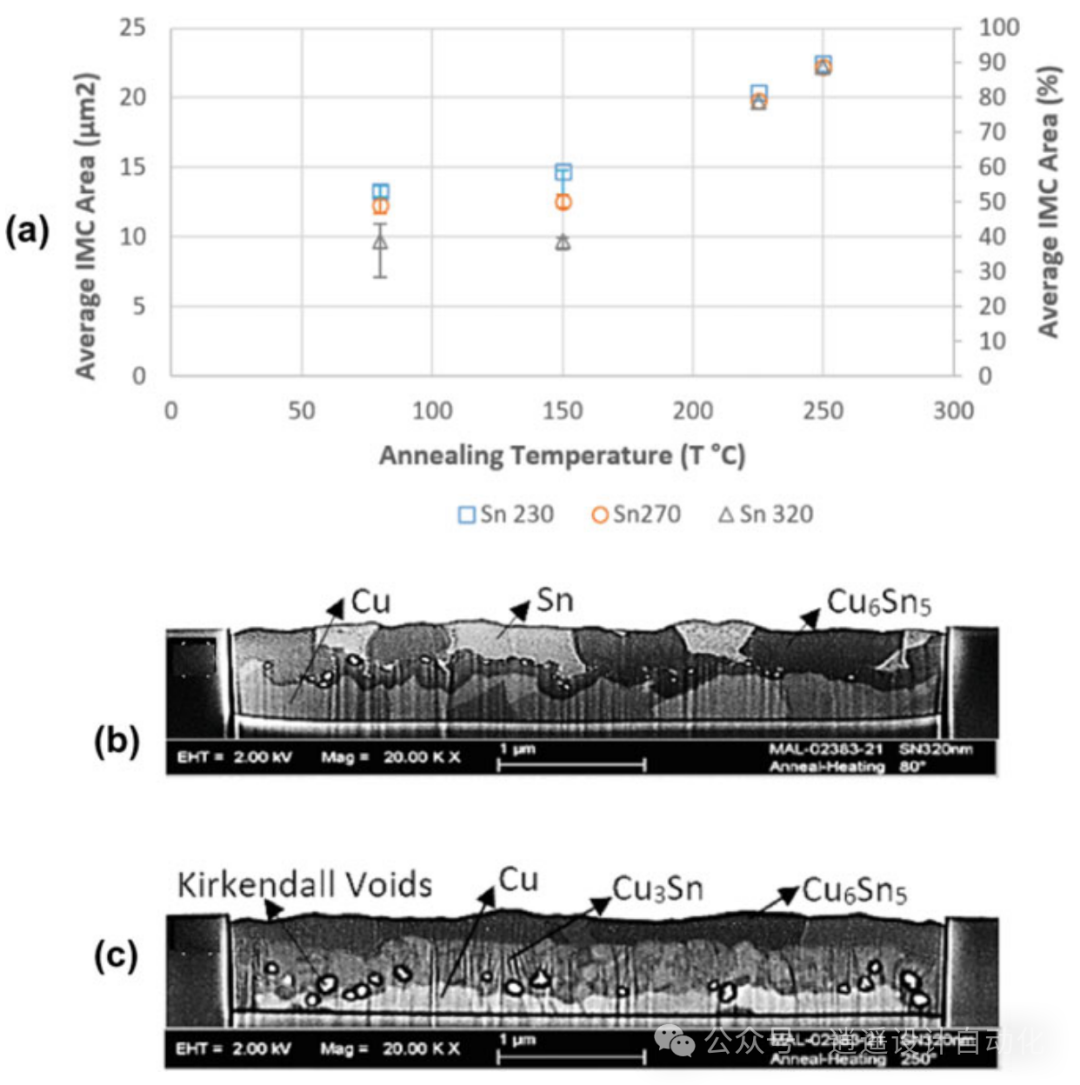

2. 金属间化合物形成

一些研究人员正在探索在键合界面处控制形成金属间化合物。例如,德累斯顿工业大学的工作研究了用于混合键合的超薄Cu-Sn双层。

图13:不同退火温度下超薄Cu-Sn双层的金属间化合物生长研究。

3. 新键合机制

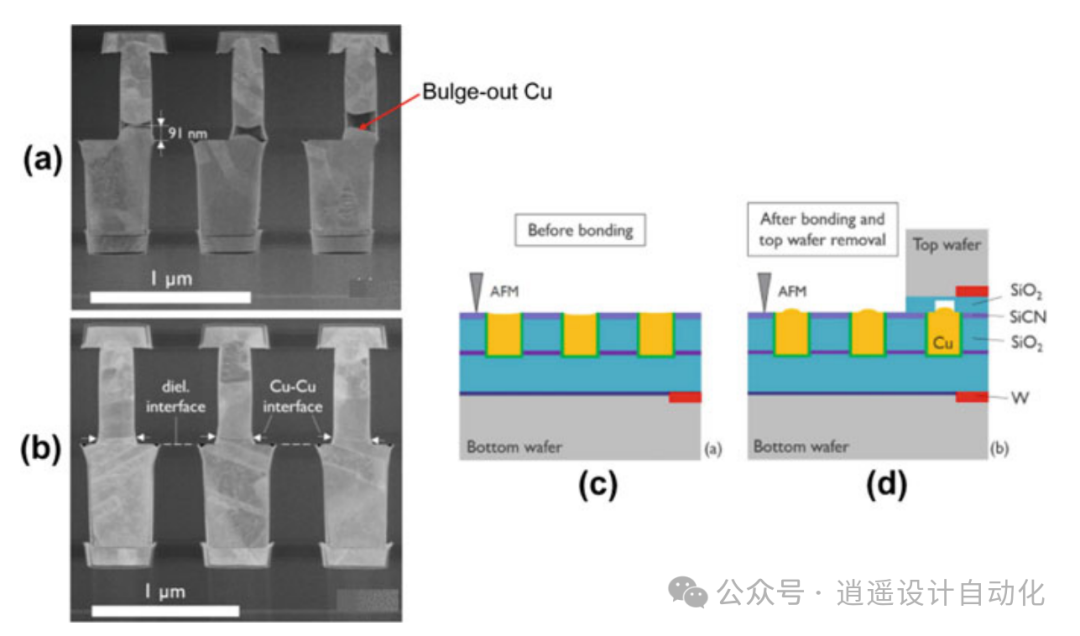

IMEC报告了一种"Cu鼓包"机制,可实现亚微米间距的混合键合。这涉及在退火过程中控制Cu扩散以填充界面处的小间隙。

图14:IMEC的Cu"鼓包"机制支持亚微米混合键合的TEM横截面图。

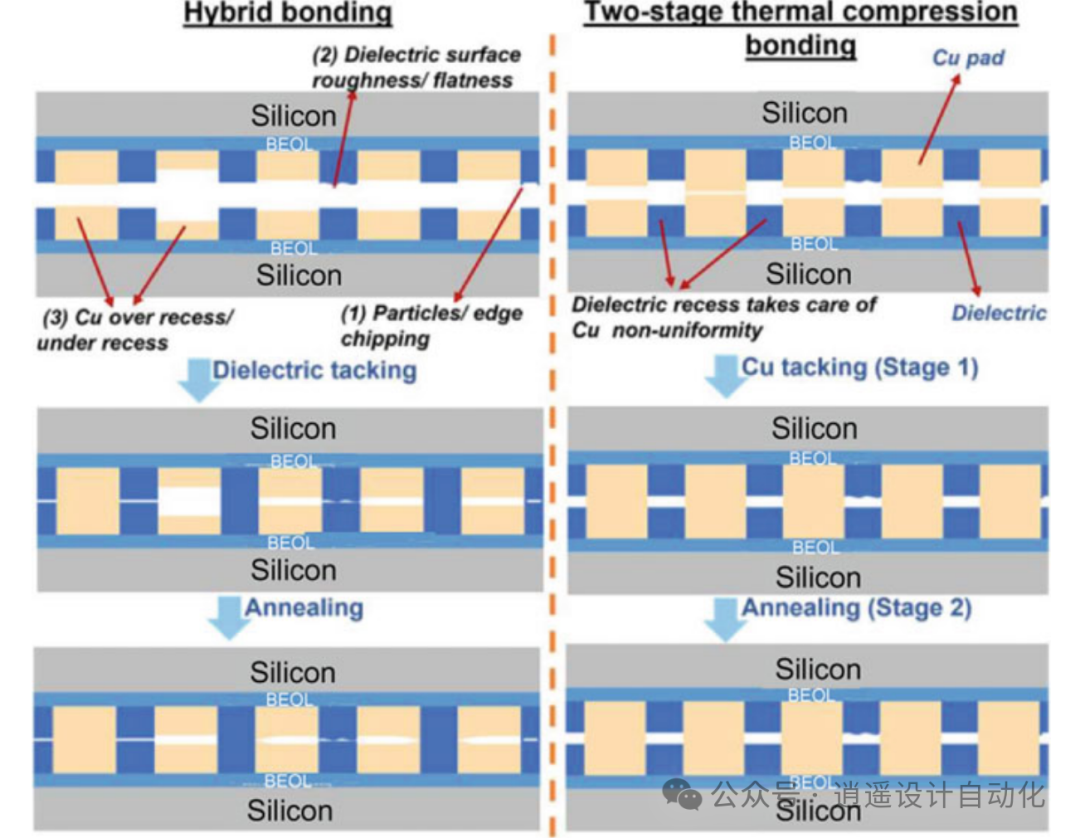

4. 替代键合方法

虽然大多数混合键合工作集中在室温下的氧化物对氧化物键合,然后退火,但也在探索一些替代方法。例如,加州大学洛杉矶分校提出了一种两阶段热压缩键合(TCB)方法,简化了工艺。

图15:传统混合键合与加州大学洛杉矶分校提出的两阶段Cu-Cu TCB方法的比较。

结论

Cu-Cu混合键合正在迅速发展成为下一代3D集成的关键技术。主要的存储器和逻辑制造商,以及设备和材料供应商,正在积极开发和优化混合键合工艺。主要关注领域包括更细间距扩展、更大尺寸晶圆/芯片键合、新型材料系统以及与先进节点器件的集成。

取得了重大进展,但仍然存在几个挑战,特别是在表面准备、对准精度和缺陷控制方面。需要在材料、工艺和设备方面继续创新,以实现混合键合在广泛应用中的大规模制造。

随着半导体行业不断推动更高水平的集成和性能,Cu-Cu混合键合将在实现先进3D和异构集成方案中发挥关键作用。未来几年可能会看到混合键合在需要超高密度互连的存储器、处理器、传感器和其他应用中得到更广泛的应用。

参考文献

[1] J. H. Lau, "Cu-Cu Hybrid Bonding," in Flip Chip, Hybrid Bonding, Fan-In, and Fan-Out Technology. Singapore: Springer Nature Singapore Pte Ltd., 2024, ch. 2, pp. 103-157.

-

3D

+关注

关注

9文章

3022浏览量

115561 -

工艺

+关注

关注

4文章

720浏览量

30391 -

先进封装

+关注

关注

2文章

562浏览量

1062

原文标题:Cu-Cu Hybrid Bonding技术在先进3D集成中的应用

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

用于3D集成的精细节距Cu/Sn微凸点倒装芯片互连工艺研究

短波红外(SWIR)成像技术:重塑先进封装检测的精度与效率

2D、2.5D与3D封装技术的区别与应用解析

FT32F030F6CU7辉芒微单片机32位M0系列MCU

技术资讯 I 图文详解 Allegro X PCB Designer 中的 3D 模型映射

【海翔科技】玻璃晶圆 TTV 厚度对 3D 集成封装可靠性的影响评估

iTOF技术,多样化的3D视觉应用

聊聊倒装芯片凸点(Bump)制作的发展史

Cu-Cu Hybrid Bonding技术在先进3D集成中的应用

Cu-Cu Hybrid Bonding技术在先进3D集成中的应用

评论