黄宏娟 赵德胜 龚亚飞 张晓东 时文华 张宝顺

(中国科学院苏州纳米技术与纳米仿生研究所)

摘要:

芯片异构集成的节距不断缩小至10μm及以下,焊料外扩、桥联成为焊料微凸点互连工艺的主要技术问题。通过对微凸点节距为8μm的Cu/Sn固液扩散键合的工艺研究,探索精细节距焊料微凸点互连工艺存在的问题,分析Cu/Sn微凸点键合界面金属间的化合物,实现了精细节距和高质量的Cu/Sn微凸点互连,获得了节距为8μm、微凸点数为1 900个、总面积为3 mm×3 mm的不均匀微凸点阵列,该阵列互连对准误差小于0.5μm,含有200个微凸点菊花链结构的电学导通。

引言

为了实现片上系统(System⁃on⁃chip,SoC)的性能,硅转接板内互连节距需要缩小至2~10μm[1⁃2],SivaChandra等人研制了节距≤10μm的硅互连结构(Siliconinterconnectfabric,Si⁃IF)[3⁃8],实现微凸点节距为10μm、微凸点直径为5μm的芯片到晶圆(Chiptowafer,C2W)的Cu—Cu直接键合工艺,在Cu微凸点氧化层预处理方面做了系列研究,包括在Cu微凸点表面覆盖一层Ti/Au薄膜用于阻止Cu的氧化以及甲酸气氛还原Cu氧化层等。Cu—Cu直接键合可以避开常用焊料键合焊料外溢、桥联的问题,但低温金属直接键合对微凸点高度一致性、表面平整度以及粗糙度的要求也相应提高,同时为了保证键合时微凸点接触紧密,键合压力也会比焊料键合要大。为此本文采用Cu—Sn热压键合来实现节距≤10μm的精细节距互连,通过在Cu微凸点表面沉积一层Sn来降低微凸点表面平整度和粗糙度的要求,并降低键合压力和键合温度。同时Cu/Sn键合后所生成的金属间化合物Cu3Sn和Cu6Sn5的熔点分别为640℃和415℃,适合多芯片堆叠[9⁃13],但在长期稳定性和耐腐蚀性方面Cu3Sn要明显优于Cu6Sn5[11,14]。

Cu/Sn固液扩散键合的典型温度比Sn熔点(232℃)高约20~50℃。Ching⁃KuanLee等人制备了节距为20μm、微凸点直径为10μm的Cu/Sn微凸点,通过芯片倒装键合工艺互连,260℃保温10s后,在150℃下退火30min,观察界面的金属间化合物(IMC)主要为Cu6Sn5和Cu3Sn,其中Cu6Sn5比Cu3Sn更厚[9]。JohnM.Lannon等人报道的Cu—Sn—Cu固液扩散键合,采用温度275℃加热180s,微凸点界面金属间化合物仅为Cu3Sn,未见Cu6Sn5,并在微凸点之间的间隙中填充BCB胶水增加可靠性[10]。JörgMeyer等人研究了孔隙Cu3Sn形成过程,分析了工艺温度、气氛以及助焊剂对金属间化合物演变的影响[15⁃17],说明如何控制金属间化合物的相是Cu/Sn微凸点键合工艺的技术难点。随着微凸点节距的进一步缩小,微凸点尺寸效应成为主要的工艺难点。目前文献报道的Cu/Sn键合的最小节距为10μm[18],且微凸点采用电镀工艺进行制备,电镀后通常需要金属研磨抛光以及电镀种子层去除工艺,工艺复杂,微凸点高度一致性、表面平整度以及粗糙度不仅受电镀工艺影响,而且受金属研磨抛光和种子层去除工艺影响,增加了微凸点制备的难度。本文采用电子束蒸发工艺进行金属薄膜沉积,用剥离的方式获得微凸点,提高了微凸点高度一致性、表面平整度和粗糙度,将节距减小至8μm。本文还研究了Cu/Sn微凸点互连工艺,展示了微凸点直径为4μm的Cu/Sn微凸点制备工艺流程,通过芯片倒装键合设备进行固液扩散键合,根据电学导通测试判断微凸点互连导通情况,对微凸点键合界面进行能谱测试,分析金属间化合物成分,对键合芯片进行剪切力测试验证微凸点键合剪切强度。

1实验

采用菊花链结构进行微凸点电连接测试,设计版图如图1所示,微凸点为非均匀分布,最大分布面积为3mm×3mm,微凸点分布于样品四周及中间,微凸点间距为4μm,四周分布电导通测试点,可测试50个微凸点、100个微凸点以及200个微凸点的导通电阻,其中四周角上的微凸点可测试相邻微凸点间的电阻,可检测开路微凸点具体分布。

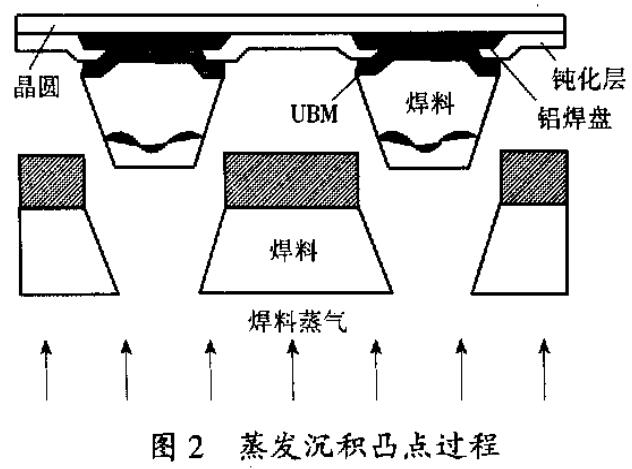

微凸点制备及互连工艺主要流程如图2所示。芯片和基板均为测试片,未进行器件结构制备。图2(a)所示为微凸点下金属层(UBM)以及菊花链结构导电层制备,采用剥离工艺实现,具体为光刻掩模形成UBM和导电层的开孔,并进行金属薄膜沉积和剥离,实现图形化金属薄膜层,金属层选用Ti/Au/Ti,第一层Ti作为芯片和基板表层材料与Au的粘附层,第二层Au作为导电层,第三层Ti作为Au和钝化层SiO2的粘附层。图2(b)所示为钝化层制备,用于菊花链结构相邻微凸点的隔离以及微凸点外围的绝缘钝化,限制微凸点材料的外溢,具体工艺采用PECVD沉积SiO2薄膜,进行光刻掩模后RIE刻蚀去除焊盘孔处的SiO2,去除光刻胶掩模,形成焊盘周围具有钝化膜的结构。图2(c)所示为微凸点制备,采用剥离工艺,具体工艺为在已完成UBM和钝化膜的芯片和基板上进行厚胶光刻,胶的厚度超过所需微凸点的厚度,此步开孔位置与UBM位置对准,开孔尺寸小于UBM开孔,并进行金属焊料的蒸发和剥离,其中微凸点材料为Cu/Sn,厚度分别为3μm和2μm。图2(d)所示为芯片和基板的微凸点互连,采用倒装键合技术实现Cu/Sn固液扩散键合,达到芯片和基板微凸点互连导通的目的。

微凸点制备完成后用扫描电镜(SEM)观察,整体形貌俯视见图3。图3(a)所示为线阵区域的微凸点形貌,可进行X、Y轴单方向大偏移导通测试以及相邻最少4个微凸点导通测试。图3(b)所示为面阵区域的微凸点形貌,微凸点形态均匀,未见相邻微凸点短路等异常现象。图3(c)所示为面阵区域微凸点放大至4000倍形貌,测试微凸点节距为8μm,微凸点直径约4.4μm,微凸点间距小于4μm。图4为微凸点倾斜形貌,由图可见,Cu呈现圆柱体形貌,Sn表面不规则、类尖顶状,如图4(a)所示;另外,Cu厚度约2.7μm,Sn厚度约2.2~2.8μm,如图4(b)所示。

3结果与讨论

采用SETfc150键合机进行倒装互连,250℃/5min,由于微凸点尺寸过小,倒装后的对准误差无法用X⁃ray、超声检测等非破坏性手段测试,采用玻璃透明样品进行对准测试,键合对准误差小于0.5μm,如图5所示。图5(a)所示为菊花链结构微凸点键合后情况,可看出分立微凸点X轴和Y轴均未有与相邻微凸点短路的现象。图5(b)所示为对准精度为0.1μm的标记键合后对准情况,X轴偏移量为0.2μm,Y轴偏移量为-0.4μm。图5(c)所示为对准精度为0.5μm的标记键合后对准情况,X和Y轴偏移量均小于0.5μm。

进行电学导通测试,测试结果如图6所示,微凸点数量为100个,微凸点分布最远距离约为3mm,电阻约80Ω,电阻包含微凸点、链接布线层和探针焊盘,平均单个微凸点电阻约0.8Ω;微凸点数量为200个,微凸点分布最远距离约为1.7mm,电阻约50Ω,平均单个微凸点电阻约0.5Ω;微凸点数量为100个,微凸点分布最远距离约为0.4mm,电阻约50Ω,平均单个微凸点电阻约0.5Ω。对比数据可知导电层电阻占据电阻比例较大。对样品进行260℃/30min氮气退火处理后进行电学测试,微凸点电阻变化不明显。

对倒装互连样品进行剪切力测试,微凸点数量为1900个,测试结果见图7,未退火处理的样品剪切强度约140gf,平均单个微凸点剪切强度约0.074gf,约为文献[18]直径为5μm的单微凸点剪切强度0.026gf的三倍,退火处理的样品剪切强度约600gf。从测试结果看,退火工艺对微凸点互连的剪切强度有明显的改善作用。

对Cu/Sn微凸点键合界面进行观察,由图8可知微凸点对准偏移量小于1μm,相邻微凸点间未短路,可观察到Sn在键合温度下沿着Cu侧面迁移。对260℃退火30min后的样品截面观察,局部微凸点在键合界面存在明显的孔隙,孔隙位置在上下微凸点的接触面处,结合图9的能谱可知,键合界面生成Cu3Sn,Sn在相中的含量为24.5%(at),不排除在键合过程中Cu/Sn合金过快,导致上下微凸点接触面成为金属间化合物之间的键合,从而形成孔隙。

4结论

通过倒装芯片技术实现了芯片级的Cu/Sn微凸点精细节距互连。微凸点节距为8μm,微凸点直径为4μm,每个芯片的微凸点阵列数为1900个。由于微凸点距离小,传统的X射线检测难以检测判断倒装后的微凸点对准精度。透明样品用于显微镜观察以测量倒装芯片对准精度,X轴和Y轴偏差小于0.5μm。单芯片200个微凸点阵列导通,单微凸点电阻约几百mΩ。单芯片剪切强度约600gf。测试结果表明,节距为8μm的Cu/Sn微凸点互连技术可应用于多芯片异质/异构3D集成封装,具有很好的应用前景。

来源:半导体材料与工艺

-

芯片

+关注

关注

463文章

54379浏览量

469007 -

晶圆

+关注

关注

53文章

5445浏览量

132713 -

工艺

+关注

关注

4文章

719浏览量

30388

原文标题:3D集成的精细节距Cu/Sn微凸点倒装芯片互连工艺研究

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电力电子集成模块封装构成与研究重点

倒装芯片与表面贴装工艺

倒装芯片的特点和工艺流程

分享一下小芯片集成的2.5D/3D IC封装技术

基于HFSS的3D多芯片互连封装MMIC仿真设计

3D Cu-Cu混合键合技术的优点和未来发展

先进封装中互连工艺凸块、RDL、TSV、混合键合的新进展

用于3D集成的精细节距Cu/Sn微凸点倒装芯片互连工艺研究

用于3D集成的精细节距Cu/Sn微凸点倒装芯片互连工艺研究

评论