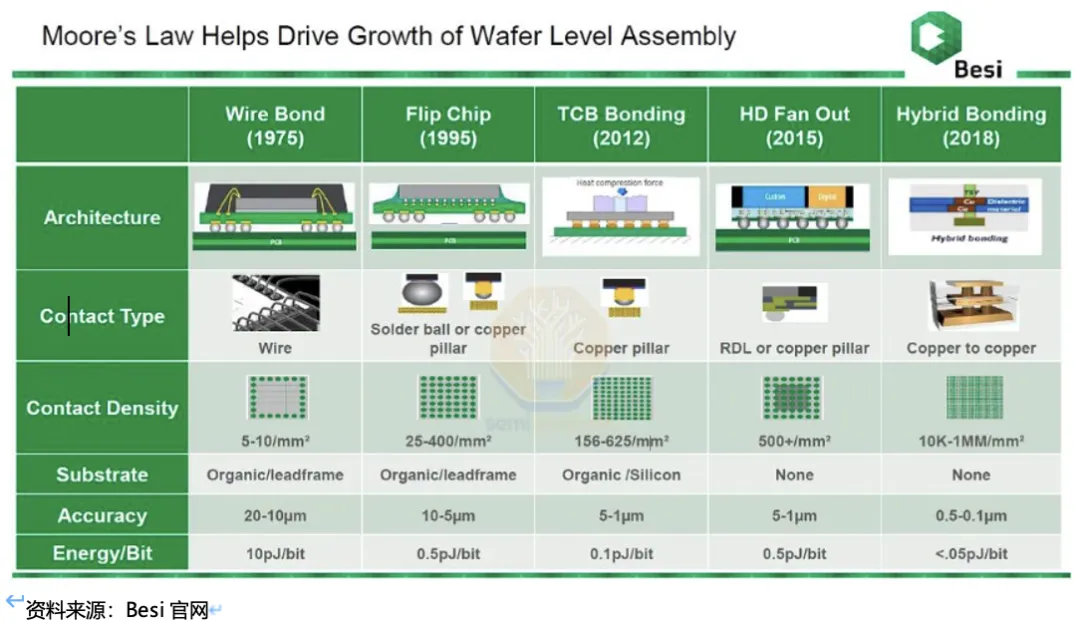

谈一谈先进封装中的互连工艺,包括凸块、RDL、TSV、混合键合,有哪些新进展?可以说,互连工艺是先进封装的关键技术之一。在市场需求的推动下,传统封装不断创新、演变,出现了各种新型的封装结构。

下游市场对于产品小型化需求增长,让SiP(系统级封装)和 PoP(叠成封装)奠定了先进封装的初始阶段。此后,倒装芯片(Flip-Chip)、晶圆级封装(WLP)和3D IC封装技术出现, 不断缩短芯片之间的互连距离。近年来,先进封装的发展非常快,台积电的InFO(集成扇出)和 CoWoS(Chip On Wafer On Substrate)、日月光的FOCoS(基板上扇出芯片)等,都引起了市场的广泛关注。而支持这些封装平台的,首要就是互连工艺。

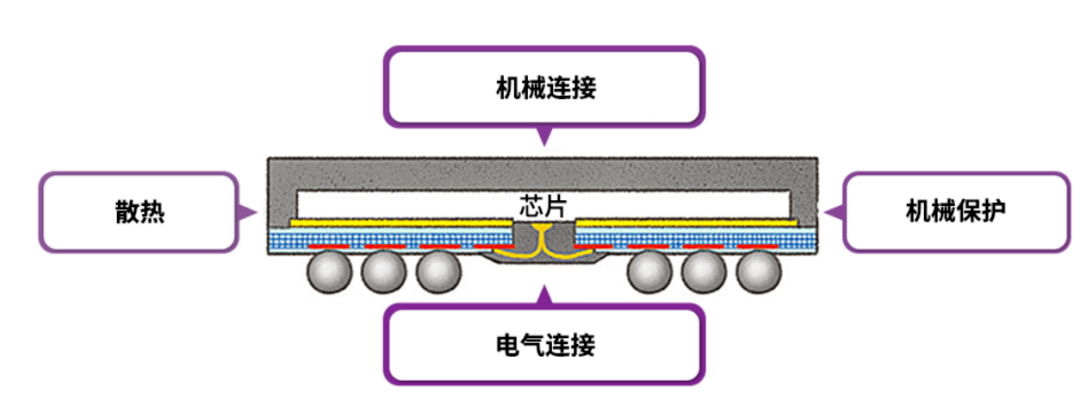

半导体封装的四大作用

凸块(Bumping)

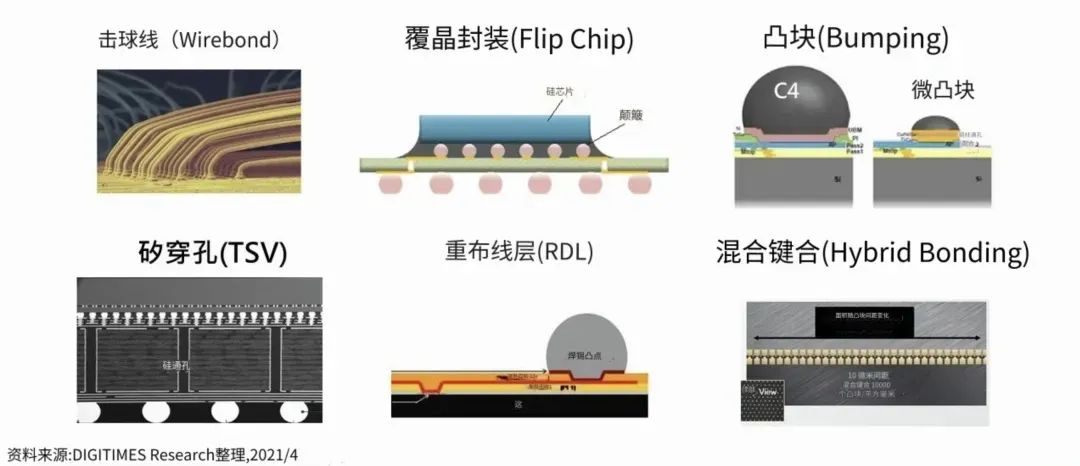

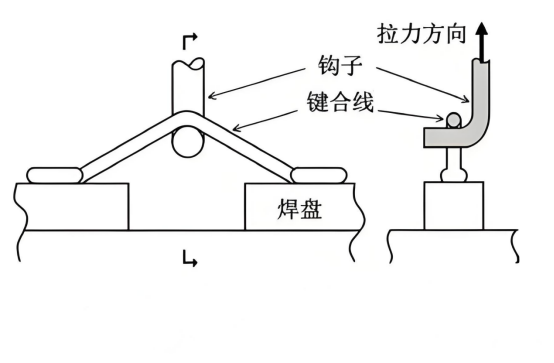

凸块(bumping)是多种先进封装形式的基础工艺,倒装(FC)、扇出型(Fan-out)封装、扇入型(Fan-in)封装、芯片级封装(CSP)、三维立体封装(3D)、系统级封装(SiP)等先进封装结构与工艺实现的关键技术均涉及凸块制造技术。

凸块是在将晶圆切割成单个芯片之前,在基板上形成由各种金属制成的“凸块”。这些凸块可在管芯和衬底之间提供比引线键合更短的传输路径,可使得芯片能够以更小、更快、更可靠的方式与其他电子元件进行通信,改善芯片封装的电气、机械和热性能。

凸块间距的微型化是凸块技术的主要发展趋势。随着电子器件向更轻薄、更微型和更高性能进步,凸块间距越小,意味着凸点密度增大,封装集成度越高,难 度越来越大。行业内凸点间距正在朝着20μm推进。而实际上部分巨头已经实现了小于10μm的凸点间距。三星的X-Cube(TCB)采用了25µm的微凸块间距和40µm的硅片厚度,而X-Cube(HCB)的微凸块间距更是达到了4µm,硅片厚度仅为10µm。这种极小的凸块间距使得三星能够生产出高性能、高密度的3D IC。台积电在3D SoIC技术方面也取得了突破,其凸点间距最小可达6um,可实现更佳效能、功耗、尺寸外观及功能,达成系统级整合。Amkor已经实现了200mm的单列铜柱小间距低至30um,交错低至30/60um。

更小的凸点间距意味着凸点密度增大,封装集成度提高,但技术难度也随之增大。面向未来,混合键合(HB)铜对铜连接技术可以实现更小的凸点间距(10μm以下)和更高的凸点密度(10000 个/mm2),并带动带宽和功耗双提升。

凸块材料也是技术创新重点之一。凸块制作的材质从传统的金凸块、铜镍金凸块发展到铜柱凸块、焊球凸块等。不同金属材质适用于不同芯片的封装,以满足不同应用场景的需求。近年来,无铅材料得到了广泛的研究及应用,,以满足环保要求。同时,一些新型金属材料如铜镍金等也被用于凸块制造中,以提高凸块的导电性和可靠性。

从制造工艺来看,凸块的制造工艺从最初的蒸发沉积法逐步发展到丝网印刷、植球、电镀、喷射、化镀等多种方法。这些方法各有优缺点,适用于不同的封装需求。电镀法因其易于批量生产、一致性好以及可以制备绝大部分凸点等优点,被广泛应用于集成电路的封装领域。同时,电镀工艺也在不断优化和改进,以提高凸块的质量和良率。

随着3D封装、Chiplet等先进封装技术的兴起,凸块技术就与之紧密结合。例如,在3D封装中,凸块技术被用于实现多个芯片或器件在垂直方向上的堆叠和互连;在Chiplet技术中,凸块则被用于将多个具有不同功能的芯片集成。

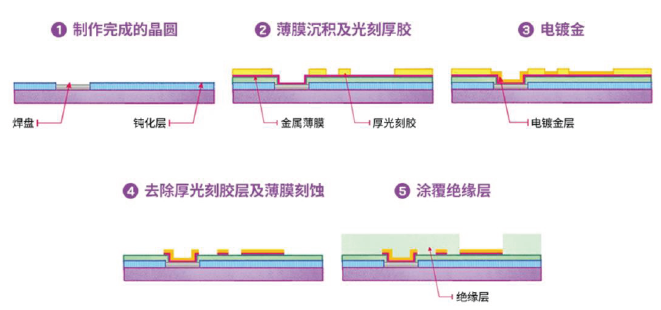

RDL重布线层技术

RDL重布线层技术,是先进封装中的一个关键部分。它的主要作用是XY平面电气延伸和互联,它有助于提高I/O密度、改善电气性能、减少芯片面积,并降低封装成本。它通过在晶圆表面沉积金属层和介质层并形成相应的金属布线图形,来对芯片的I/O端口进行重新布局,将其布置到新的、节距占位可更为宽松的区域。

在扇入晶圆级封 装(FIWLP)和扇出晶圆级封装(FOWLP)等先进封装中,RDL为核心关键工艺。使得封装厂能够在扇出封装技术方面与晶圆代工厂展开竞争。通过 RDL,IO Pad 可 以制成 FIWLP 或 FOWLP 中不同类型的晶圆级封装。

在 FIWLP 中,凸块全部生长在芯片上,芯片和焊盘之间的连接主要依靠RDL的金属线。封装后,IC的尺寸几乎与芯片面积相同。在 FOWLP 中,凸块可以生长在芯片外,封装后的 IC 比芯片面积大1.2 倍。以台积电的 InFO为例,InFO 在载体上使用一个或多个裸 芯片,然后将其嵌入到模塑料的重构晶圆中,并在晶圆上制造RDL互连和介电层。单芯片 InFO 提供高凸点数量,RDL 线从芯片区域向外延伸,形成“扇出”拓扑。

RDL工艺技术趋势来看,首先是线宽线距的不断缩小随着工艺技术的发展,RDL形成的金属布线的线宽线距(L/S)正在不断缩小。未来三年,RDL的L/S将进入亚微米级别,赋能扇出封装更高效能集成。台积电的RDL技术解决方案已经能够实现高密度布线,其InFO_oS技术利用InFO技术具有更高密度的2/2μm RDL线宽/间距,并提供多达14个重新分布层。三星在其I-CubeE技术中采用了集成硅桥的RDL中介层,相比现有硅中介层降低了封装成本,同时利用小L/S优势的硅桥实现了高性能和高密度互连。

其次,材料工艺也在不断创新。重布线层的金属线路以电镀铜材料为主,根据需要也可以在铜线路上镀镍金或者镍钯金材料,相关核心材料包括光刻胶、电镀液、靶材、刻蚀液等。随着RDL技术精度的提高,对材料的要求也越来越高。新型的低损耗介电材料、高导电性金属材料等被广泛应用于RDL制造中,以提高封装性能和可靠性。而在先进工艺方面,一些领先企业采用了新型垂直电镀铜技术,无需使用夹具,且能实时监测电镀液成分,确保工艺安全稳定。

此外,RDL-first工艺的发展也值得关注。与传统的Chip-first工艺相比,RDL-first工艺先在载片上完成布线后进行芯片倒装,可以实现更小的线宽线距和更高的封装良率。它特别适用于多芯片、大尺寸的高密度扇出封装。台积电推出了多种RDL-first封装方案,如CoWoS-R和InFO等,这些方案利用RDL中介层实现了高性能和高密度互连。三星在其I-CubeE和R-Cube技术中也采用了RDL-first工艺,以降低封装成本并提高性能。

面板级封装是当前行业主要热点之一。RDL技术在面板级封装中扮演着关键角色。在面板级封装中,RDL技术可以实现芯片之间的高效互连,提高封装密度和性能。FOPLP技术利用RDL层将芯片上的I/O端口重新布局到占位更为宽松的区域,并形成面阵列排布。这样,封装过程中可以直接连接到RDL层上的触点,而不仅仅是连接到芯片的边缘。这种技术提高了封装密度和连接灵活性。

在面板级封装中,RDL-first工艺成为了一种趋势。这种工艺先在载片上完成RDL布线,然后再进行芯片倒装和封装。与传统的Chip-first工艺相比,RDL-first工艺可以实现更小的线宽线距和更高的封装良率。

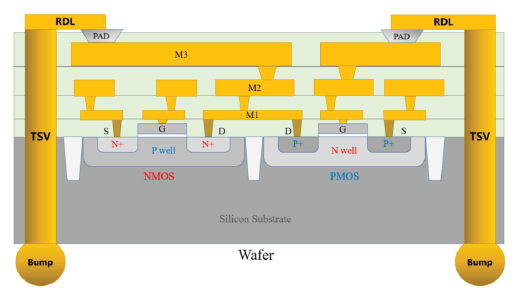

TSV技术

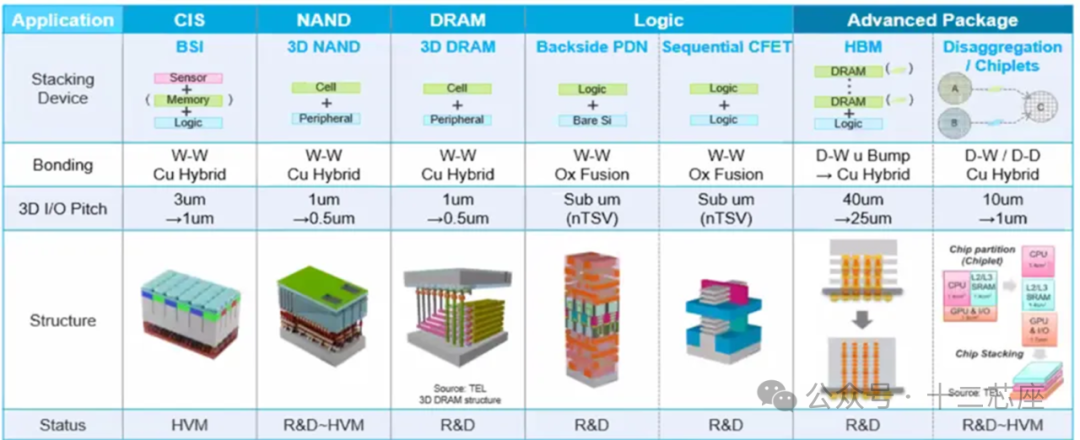

TSV技术是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的技术。它极大地缩短了芯片间的互连长度,减小了信号延迟和功耗,提高了带宽和封装密度。因此,TSV技术被认为是实现3D封装和2.5D封装的关键工艺之一。

与传统 Wire Bonding 的芯片堆叠技术不 同,TSV技术能够使芯片在3D堆叠的密度最大化,外形尺寸最小,并且大幅改善芯片运行速度,降低功耗。通过 TSV 技术将多层平面型芯片进行堆叠互连,减小芯片面积,大大缩短整体 互连线的长度,互连线长度的缩短能有效降低驱动信号所需的功耗。

从工艺技术趋势上看,一是TSV孔径与深宽比的不断优化。随着工艺技术的不断进步,TSV的孔径和深宽比正在不断优化。更小的孔径和更大的深宽比意味着更高的封装密度和更短的互连路径。

二是高密度TSV的设计与制造。在高密度应用场景下,TSV存在严重的热应力问题,会影响器件性能甚至导致损坏。中国科学院微电子研究所研究团队提出了两端窄中间宽、两端封闭中间空心的“类橄榄球”状TSV结构,有效解决了高密度TSV互连中的热应力问题,实现了国际已有报道中深度最大(>100μm)、深宽比最大(>20.3:1)、残余应力最小(31.02MPa)的TSV结构。

三是TSV填充材料的创新与改进。铜因其良好的导电性、低电迁移性和低成本,成为TSV填充材料的首选。然而,随着TSV深宽比的不断提高,对填充材料的要求也越来越高。在电镀铜填充TSV工艺中,应用最多的硫酸铜体系与甲基磺酸铜体系。甲基磺酸铜体系能溶解更多Cu2+,更利于填孔。此外,氯离子在镀液中有着不可或缺的作用,可以提高阳极活性并防止阳极产生铜粉,减少电镀过程中产生的铜颗粒。

TSV 主要有三大应用领域,分别是2.5D中介转接层(Interposer)封装、3D IC封装和3D圆片级芯片(3D WLCSP)封装。对应 TSV 生产流 程,会涉及到深孔刻蚀、PVD、CVD、铜填充、微凸点及电镀、清洗、减薄、键合等二十余种工艺。

1、2.5D 中介转接层封装,其特征是正面有多层细节距再布线层和细节距微凸点,主流 TSV 深宽比达到 10:1,厚度约为 100m。台积电的 CoWoS采用的就是2.5D TSV 技术。在CoWoS技术中,TSV是实现多层堆叠芯片之间高效互连的关键。通过TSV技术,可以显著缩短芯片间的互连长度,从而减小信号延迟和功耗,提高数据传输带宽和系统性能。

在CoWoS封装中,硅中介层(Silicon Interposer)扮演着重要角色。TSV技术被用于在硅中介层上制作垂直导通孔,以实现中介层与芯片、中介层与基板之间的互连。在高性能计算(HPC)和存储应用中,CoWoS技术通过TSV技术将多个高性能计算芯片和高带宽存储器(如HBM)堆叠在一起,实现高效的数据处理和传输。

随着工艺技术的进步,未来CoWoS封装中TSV的密度将进一步提高,以实现更高的封装密度和性能。为了应对TSV制造过程中的挑战(如深宽比增加、热应力问题等),台积电等领先企业正在探索新材料和新工艺的应用,以优化TSV的性能和可靠性。

2、3D IC封装:应用方向主要是存储类产品,其原因是存储类产品引脚密度 小,版图布局规律,芯片功率密度小等。通过 TSV 通孔实现三维集成,可以增加存 储容量,降低功耗,增加带宽,减小延迟,实现小型化。

3、3D WLCSP:主要应用于图像、指纹、滤波器、加速度计等传感器封装领 域。其特点是采用 Via Last 工艺,TSV 深宽比较小(1:1~3:1),孔径较大出于对成本 的考虑,目前图像传感器封装大多采取低深宽比的 TSV 结构。

混合键合(Hybrid Bonding)

混合键合(Hybrid Bonding)是通过铜—铜金属键合和二氧化硅—二氧化硅介质层键合实现无凸点永久键合的一种芯片三维堆叠高密度互连技术。相关数据显示,混合键合技术可实现极小间距的芯片焊盘互连,每平方毫米可互连的芯片焊盘数达104~106 个,可以提供更高的互连密度、更小更简单的电路、更大的带宽、更小的电容和更低的功耗。

主要优点包括实现芯片之间无凸点互连;实现芯片之间超细间距的互连,比微凸点提高10 倍以上,超细间距的互连将增加布线有效使用面积, 大幅增加通道数量;实现超薄芯片制备,通过芯片减薄可使芯片厚度和重量大幅降低,并且可进一步提升系统中芯片的互连带宽;实现键合可靠性的提高,铜—铜触点间以分子尺度融合,取消了焊料连接,二氧化硅—二氧化硅以分子共价键键合取消了底填材料,极大提高了界面键合强度,增强了芯片的环境适应性。

混合键合工艺主要包含D2W(Die-to-Wafer)和 W2W(Wafer-to-Wafer)两类。根据 EVG 报告《Bonding Technologies for the Next Generation Integration Schemes》(发布于 2021 年6月 10 日)数据,Wafer-to-Wafer 的工艺更加成熟,但需要每个芯片尺寸相同,且整体良率较低。下游应用端,在背光 CIS 及存储领域3D NAND等领域均已实现量产。而 D2W下游应用前景更广,但产品仍处于研发及量产爬坡阶段。

连接密度与精度的提升是混合键合工艺技术关键。目前,行业内主要企业通过采用先进的机器视觉和精密机械控制系统,实现了亚微米级乃至纳米级的对准精度,确保了芯片之间的高密度、高精度连接。

表面处理技术:在混合键合过程中,芯片表面的平整度对连接质量至关重要。为了获得更好的连接效果,企业正在不断优化表面处理技术,如化学机械平坦化(CMP)等,以确保芯片表面的平整度达到纳米级。

退火温度与时间的降低:退火是混合键合过程中的关键步骤之一,用于形成牢固的键合。近年来,研究人员通过改进退火工艺,降低了所需的退火温度和时间,从而减少了工艺过程中的热应力和损伤风险。

新型介电材料:为了进一步提高混合键合的键合强度和可靠性,研究人员正在探索新型介电材料的应用,如碳化硅氮化物(SiCN)等。这些新型材料具有更好的化学稳定性和机械性能,有助于提高混合键合的键合质量。

行业内主要企业的做法也值得关注。台积电推出名为3D Fabric的混合键合服务,该服务已广泛应用于AMD的V-Cache等产品中。通过采用超高密度垂直堆叠技术,台积电实现了高性能、低功耗和最小电阻-电感-电容(RLC)的封装解决方案。台积电的SoIC(System on Integrated Chip)采用混合键合技术实现芯片之间的高密度互连,支持从10微米以下开始的键合间距。SK海力士计划于2026年在其HBM生产中采用混合键合技术。通过混合键合,SK海力士旨在提高HBM产品的性能和能效,同时降低生产成本。

-

SiP

+关注

关注

5文章

537浏览量

107468 -

半导体封装

+关注

关注

4文章

312浏览量

15131 -

TSV

+关注

关注

4文章

136浏览量

82381 -

先进封装

+关注

关注

2文章

520浏览量

972

原文标题:先进封装的互连工艺升级新进展:凸块、RDL、TSV、混合键合

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

先进封装中互连工艺凸块、RDL、TSV、混合键合的新进展

先进封装中互连工艺凸块、RDL、TSV、混合键合的新进展

评论