半导体IP领域的先锋企业Alphawave Semi近日宣布了一项重大技术突破,成功推出了业界首款基于最新UCIe(Universal Chiplet Interconnect Express)标准的3nm Die-to-Die(D2D)多协议子系统IP。这一里程碑式的成果不仅标志着半导体互连技术的又一次飞跃,还通过深度融合台积电的Chip-on-Wafer-on-Substrate(CoWoS)先进封装技术,为超大规模数据处理、高性能计算(HPC)及人工智能(AI)等前沿领域带来了前所未有的性能提升。

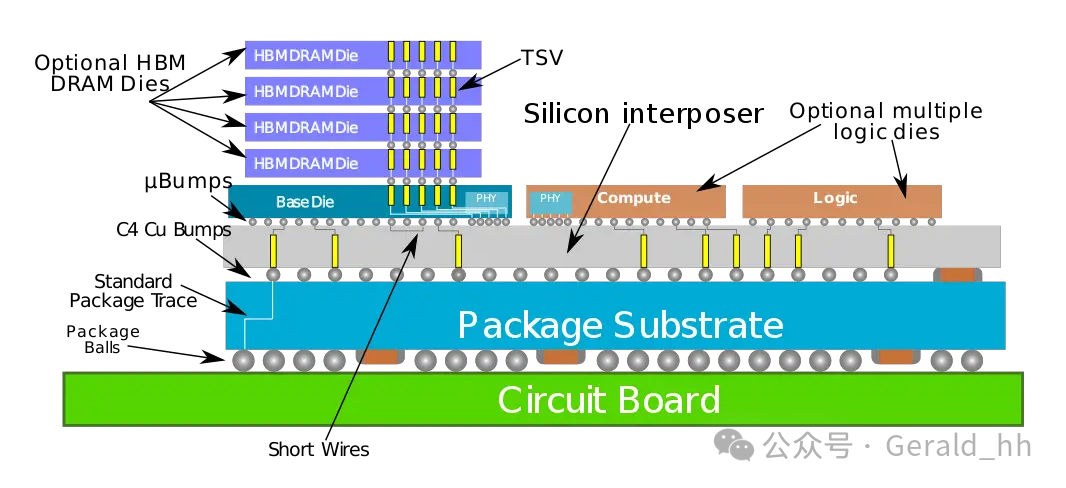

这款专为高性能需求设计的子系统IP,是Alphawave与台积电紧密合作的结晶。它充分利用了台积电CoWoS 2.5D硅中介层封装技术的优势,实现了前所未有的8 Tbps/mm带宽密度,以及高达24 Gbps的D2D数据传输速率,为数据密集型应用提供了前所未有的高效通道。

该子系统IP集成了完整的PHY(物理层)和控制器,构成了一个高度集成且可灵活配置的解决方案。这一设计不仅极大简化了系统设计的I/O复杂度,还通过优化功耗和降低延迟,为用户带来了更加高效、可靠的性能体验。对于追求极致性能和效率的数据中心、超级计算机以及AI加速平台而言,这无疑是一项革命性的技术突破。

Alphawave Semi的这一创新成果,不仅展示了其在半导体IP领域的深厚积累和技术实力,也为整个半导体行业树立了新的标杆。随着云计算、大数据、人工智能等技术的蓬勃发展,对高性能计算能力的需求日益增长。Alphawave Semi与台积电携手推出的这款3nm UCIe IP,无疑将为这些领域的快速发展提供强有力的技术支撑。

-

半导体

+关注

关注

339文章

31241浏览量

266589 -

台积电

+关注

关注

44文章

5811浏览量

177055 -

CoWoS

+关注

关注

0文章

170浏览量

11536

发布评论请先 登录

台积电拟投资170亿,在日本建设3nm芯片工厂

1.4nm制程工艺!台积电公布量产时间表

先进封装市场迎来EMIB与CoWoS的格局之争

台积电2纳米制程试产成功,AI、5G、汽车芯片

台积电预计对3nm涨价!软银豪掷54亿美元收购ABB机器人部门/科技新闻点评

化圆为方,台积电整合推出最先进CoPoS半导体封装

业界首款支持星闪车钥匙的智能手机亮相

台积电先进制程涨价,最高或达30%!

西门子与台积电合作推动半导体设计与集成创新 包括台积电N3P N3C A14技术

AMD实现首个基于台积电N2制程的硅片里程碑

Alphawave推出业界首款支持台积电CoWoS封装的3nm UCIe IP

Alphawave推出业界首款支持台积电CoWoS封装的3nm UCIe IP

评论