本文介绍了TSV工艺流程是什么。

用于2.5D与3D封装的TSV工艺流程是什么?有哪些需要注意的问题?

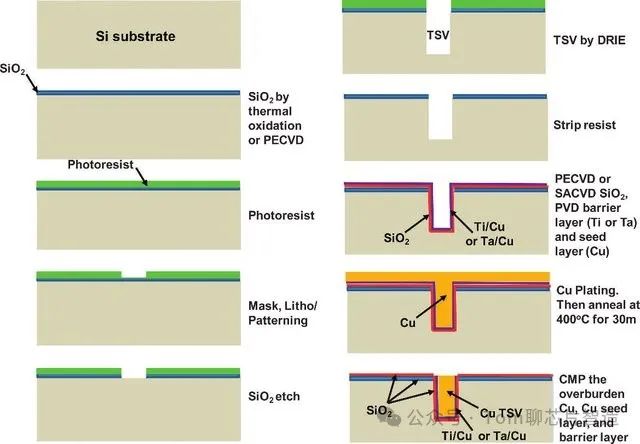

上图是TSV工艺的一般流程。TSV,全名Through-Silicon Via,又叫硅通孔工艺。

硅基底准备:流程以一块覆盖有二氧化硅(SiO₂)层的硅基底开始。这层SiO₂可以通过热氧化或等离子体增强化学气相沉积(PECVD)方法形成。

光刻:光刻胶(Photoresist)被涂布在SiO₂层上,然后通过曝光和显影步骤进行图案化,以得到后面工序要进行硅蚀刻的区域。 硅蚀刻:使用光刻图案作为掩模,采用DRIE在硅基底中蚀刻出通孔。

去除光刻胶:在蚀刻完成后,去除光刻胶以准备接下来的层沉积步骤。

沉积绝缘层和阻挡层:通过PVD,PECVD或原子层沉积(ALD)技术在孔壁上沉积一层二氧化硅来作为绝缘层,防止电子窜扰;然后沉积一层导电的阻挡层,如钛/铜(Ti/Cu)或钽/铜(Ta/Cu),以便后续的铜镀层能更好地附着,且能防止电子迁移。

铜电镀:在绝缘层和阻挡层上进行铜镀层,以填充TSV孔洞。一般通过电镀方式完成。电镀完成后,进行退火工序,释放应力。

化学机械抛光(CMP):最后,进行CMP步骤来平整表面,去除多余的铜和阻挡层,留下一个与硅基底表面平齐的铜TSV。

审核编辑:刘清

-

CMP

+关注

关注

7文章

162浏览量

27900 -

TSV

+关注

关注

4文章

139浏览量

82774 -

光刻胶

+关注

关注

10文章

357浏览量

31861 -

3D封装

+关注

关注

9文章

149浏览量

28369

原文标题:TSV工艺流程介绍

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

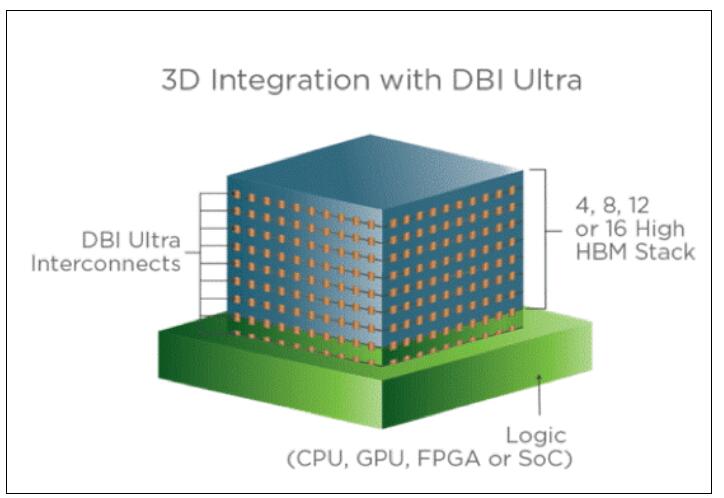

研发的铜混合键合工艺正推动下一代2.5D和3D封装技术

2.5D/3D芯片-封装-系统协同仿真技术研究

3D封装结构与2.5D封装有何不同?3D IC封装主流产品介绍

用于2.5D与3D封装的TSV工艺流程是什么?有哪些需要注意的问题?

用于2.5D与3D封装的TSV工艺流程是什么?有哪些需要注意的问题?

评论