日月光集团研发中心李长祺处长日前在世界半导体大会的先进封装创新技术论坛上分享小芯片集成的2.5D/3D IC封装技术,李处长表示, 全球数据总量在2025年将达到175ZB,大数据处理过程与传输及时化日趋重要。系统整合把传输的距离缩短,有效提升传输速率及能量效率。随着硅光子学(Silicon Photonics)发展,光的传输频宽级效率也变得越来越高,把光整合至封装形态是未来重要的发展趋势。

李处长也强调,系统整合与SoC分拆是驱动先进封装与小芯片Chiplet集成的关键因素,在系统整合中,内存、电源与光学整合是主要的发展机会,SoC分拆中I/O分拆与SRAM分拆最为重要。小芯片Chiplet集成技术中细间距互连、大规模整合、电力传输以及散热等都是未来主要发展方向。

2.5D/3D IC封装特性与异质整合

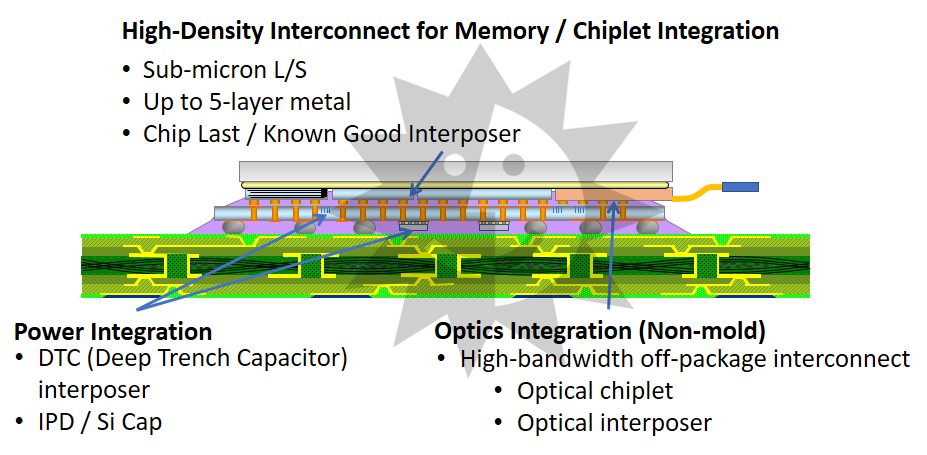

异质整合需要通过先进封装提升系统性能,以2.5D/3D IC封装为例,可提供用于存储器与小芯片集成的高密度互连,例如提供Sub-micron的线宽与线距,或五层的互连,是良好的Interposer(中介层)。此外可通过DTC Interposer与IPD/Si Cap技术完成电源集成,通过高带宽非封装互连提供高性能的长距离资料传输。日月光目前与合作伙伴正在合作开发Optical Chiplet与Optical Interposer的技术,为进一步小型化提供可靠的解决方案。

内存集成发展趋势

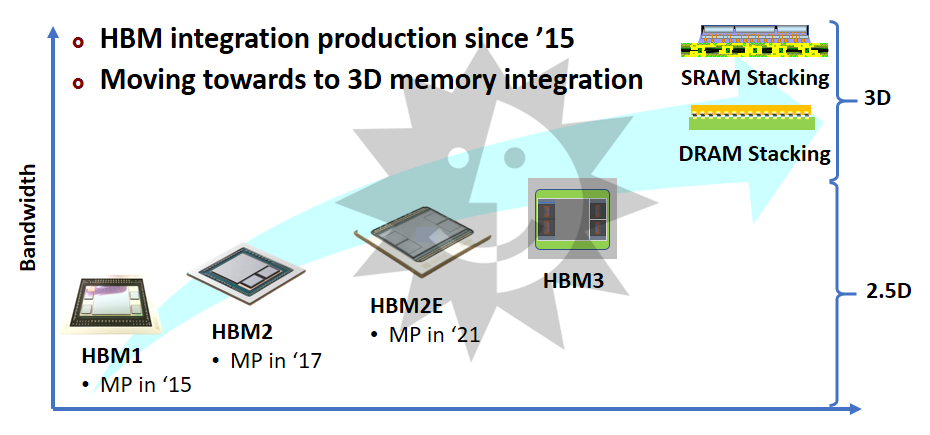

内存频宽的需求越来越高,高频宽内存的集成发展成为关键竞争力。内存集成未来主要发展趋势有两种,一种是整合HBM3提高频宽,另一种是做3D整合及堆叠,如SRAM堆叠及DRAM堆叠。日月光率先在2015年量产HBM1整合的封装,2017年HBM2也顺利量产,在2021年量产HBM2E,目前正朝着3D整合方向发展。

电源集成Si Cap发展趋势

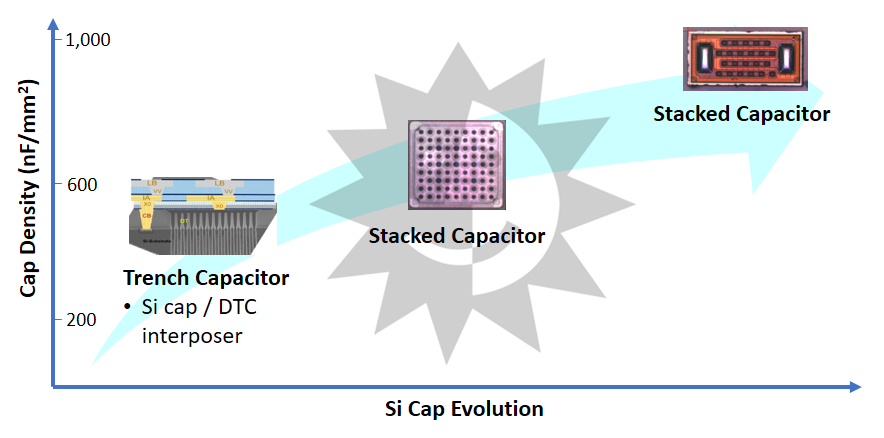

随着电源功率越来越高,电容密度的要求也同步提高,因此电容整合的重要性尤为突出。日月光正在与合作伙伴共同开发不同的电容技术,例如应用在Si Cap及DTC Interposer上沟槽电容器(Trench Capacitor)以及电容密度更高的堆叠电容器(Stacked Capacitor),以满足越来越高的电容密度需求。

光学集成发展趋势

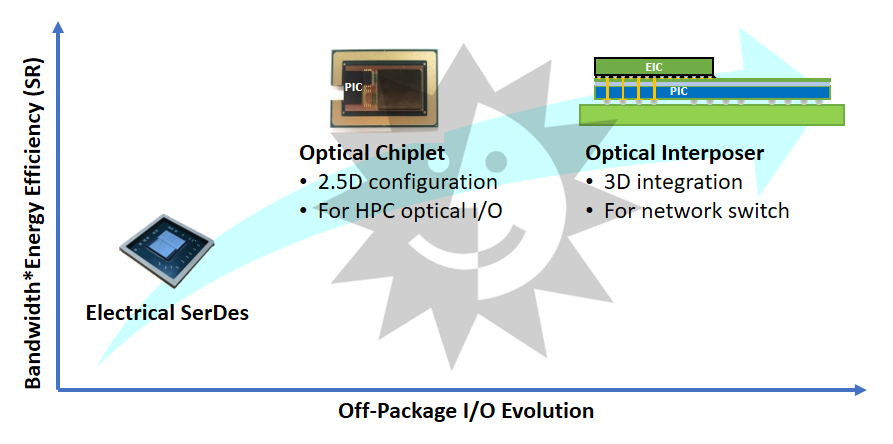

频宽与能量效率问题是未来电的长距离传输主要瓶颈,因此光学整合成为重点发展趋势之一。目前日月光与合作伙伴开发两种不同的光整合技术,第一个是光学小芯片Chiplet技术,应用2.5D 硅中介层(Silicon Interposer)整合光学小芯片Chiplet以及SoC技术,以满足最高的能量效率与最高的频宽,如应用于高速运算光学I/O的要求。另一个发展趋势是基于3D整合的光学中介层(Optical Interposer)技术,即电子IC在上面,光子IC在下面,这种整合方式可提供更高的频宽级能量效率的需求,可应用于网络交换机。

日月光持续开发不同的先进封装如扇出型封装Fan Out形态的 FOCoS、2.5D/3D IC封装、混合键合Hybrid Bonding技术等,与产业链合作伙伴们共同研发合作,以满足系统整合及小芯片Chiplet集成发展要求。

审核编辑:刘清

-

电容器

+关注

关注

64文章

6971浏览量

108651 -

soc

+关注

关注

40文章

4638浏览量

230355 -

DRAM芯片

+关注

关注

1文章

89浏览量

18947 -

IC封装

+关注

关注

4文章

196浏览量

27741

原文标题:聚焦小芯片Chiplet集成的2.5D/3D IC 封装技术

文章出处:【微信号:ASE_GROUP,微信公众号:ASE日月光】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于 HT 的 2.5D 组态可视化技术方案与场景实现

台积电如何为 HPC 与 AI 时代的 2.5D/3D 先进封装重塑热管理

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

分享一下小芯片集成的2.5D/3D IC封装技术

分享一下小芯片集成的2.5D/3D IC封装技术

评论