复位信号存在亚稳态,有危险吗?

复位信号在电子设备中起着重要的作用,它用于使设备回到初始状态,以确保设备的正常运行。然而,我们有时会发现复位信号存在亚稳态,这意味着信号在一定时间内未能完全复位,并停留在一个临界状态。这种亚稳态可能会引发一系列问题,包括设备故障和数据丢失等。因此,我们需要深入探讨这个问题,并了解它的危险性。

第一部分:复位信号的作用和原理

复位信号是一种用于让电子设备回到初始状态的信号。当设备处于异常状态时,通过发送复位信号,可以迫使设备重新启动和初始化,以确保设备能够正常运行。复位信号通常由电路中的复位线产生,并在特定条件下触发。

第二部分:亚稳态的定义和原因

亚稳态是指在一定时间内,设备未能完全从复位状态恢复正常,而是停留在一个临界状态。产生亚稳态的原因有很多,如信号传输延迟、电路不稳定、系统资源不足等。这些因素可能导致复位信号在设备中不断传播,直到达到稳定态,从而影响设备的正常运行。

第三部分:亚稳态可能造成的问题

亚稳态可能引发一系列问题,包括设备故障和数据丢失等。设备故障可能由于复位信号未能正常传递到设备的关键组件,导致组件未能重新初始化或重启。这将导致设备不能正常工作或执行错误的操作。数据丢失则可能由于复位信号在传输过程中丢失或延迟,导致设备未能正确保存数据或中断数据写入操作。

第四部分:预防和解决亚稳态问题的方法

为了防止亚稳态问题,我们可以采取一系列措施。首先,我们可以使用高品质的信号传输线和设备,以减少信号传输延迟和不稳定性。其次,我们可以增加冗余的复位机制,以确保即使一个复位信号无法到达,其他复位信号仍然可以起作用。此外,我们还可以进行定期的设备维护和监控,以及对亚稳态问题进行实时检测和修复。

结论:

复位信号的亚稳态问题可能对电子设备的正常运行造成严重影响,包括设备故障和数据丢失等。因此,我们需要引起足够的重视,并采取相应的措施来预防和解决这个问题。通过使用高品质的信号传输线和设备,增加冗余的复位机制,以及进行定期的设备维护和监控,我们可以最大程度地减少亚稳态问题的发生。只有这样,我们才能确保设备的持续稳定运行,并保护关键数据的安全。

-

亚稳态

+关注

关注

0文章

47浏览量

13752 -

复位信号

+关注

关注

0文章

71浏览量

6833

发布评论请先 登录

深入解析MC14538B:双精度可重触发/可复位单稳态多谐振荡器

为何跨复位域问题是危险的“芯片杀手”

MAX6467/MAX6468:微处理器监控复位电路新选择

MC14528B双单稳态多谐振荡器:电子设计中的实用选择

高速CMOS逻辑双可重触发精密单稳态多谐振荡器:CD54HC4538与CD74HCT4538深度解析

深入解析MC14538B:双精度可重触发/可复位单稳态多谐振荡器

深入解析CD4047B:CMOS低功耗单稳态/无稳态多谐振荡器

高速CMOS逻辑双可重触发单稳态多谐振荡器:CD54/74HC123等系列解析

CD4047B:CMOS低功耗单稳态/无稳态多谐振荡器的设计与应用

深入解析MC14538B:双精度可重触发/可复位单稳态多谐振荡器

CD4098B:CMOS 双单稳态多谐振荡器的技术解析与应用指南

深入解析 MC14538B 双精度可重触发/可复位单稳态多谐振荡器

高速CMOS双单稳态多谐振荡器CD54HC221、CD74HC221和CD74HCT221的深度解析

CD4047B:低功耗单稳态/无稳态多谐振荡器的设计与应用

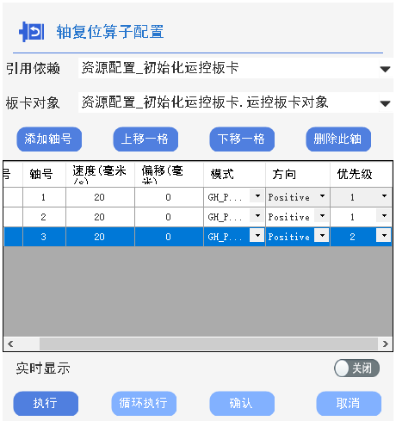

GraniStudio零代码平台轴复位算子支持多少个轴同时复位,有哪些回零模式?

复位信号存在亚稳态,有危险吗?

复位信号存在亚稳态,有危险吗?

评论