欢迎了解

1 引言

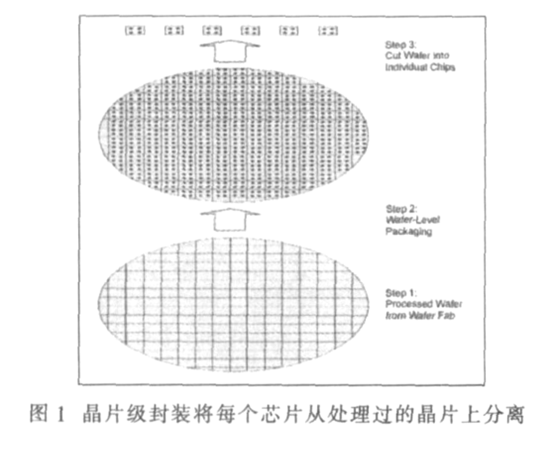

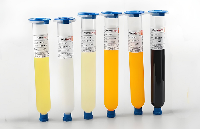

半导体技术的进步大大提高了芯片晶体管数量和功能, 这一集成规模在几年前是无法想象的。因此, 如果没有 IC 封装技术快速的发展, 不可能实现便携式电子产品的设计。在消费类产品小型化和更轻、更薄发展趋势的推动下, 制造商开发出更小的封装类型。最小的封装当然是芯片本身, 图 1 描述了 IC 从晶片到单个芯片的实现过程, 图 2 为一个实际的晶片级封装 (CSP) 。

晶片级封装的概念起源于 1990 年, 在 1998 年定义的 CSP 分类中, 晶片级 CSP 是多种应用的一种低成本选择, 这些应用包括 EEPROM 等引脚数量较少的器件, 以及 ASIC 和微处理器。 CSP 采用晶片级封装 (WLP) 工艺加工, WLP 的主要优点是所有装配和测试都在晶片上进行。随着晶片尺寸的增大、管芯的缩小, WLP 的成本不断降低。作为最早采用该技术的公司, Dallas Semiconductor 在 1999 年便开始销售晶片级封装产品。

2 命名规则

业界在 WLP 的命名上还存在分歧。 CSP 晶片级技术非常独特, 封装内部并没有采用键合方式。封装芯片的命名也存在分歧。常用名称有: 倒装芯片 (STMicroelectronics 和 Dallas Semiconductor TM ) 、CSP 、晶片级封装、 WLCSP 、 WL- CSP 、 MicroSMD(Na-tional Semiconductor) 、 UCSP (Maxim Integrated Prod-ucts) 、凸起管芯以及 MicroCSP(Analog Devices) 等。

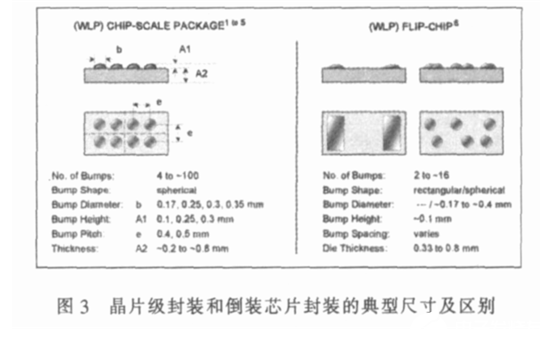

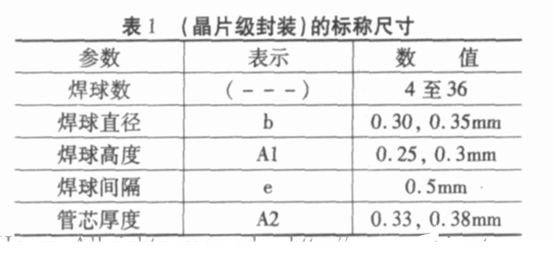

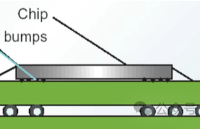

对于 Maxim/Dallas Semiconductor , “倒装芯片”和“晶片级封装”, 最初是所有晶片级封装的同义词。过去几年中, 封装也有了进一步地细分。在本文以及所有 Maxim 资料中, 包括公司网站, “倒装芯片”是指焊球具有任意形状、可以放在任何位置的晶片级封装管芯 ( 边沿有空隙 ) 。 “晶片级封装”是指在间隔规定好的栅格上有焊球的晶片级封装管芯。图 3 解释了这些区别, 值得注意的是, 并不是所有栅格位置都要有焊球。图 3 中的倒装芯片尺寸反映了第一代 Dallas Semiconductor 的 WLP 产品; 晶片级封装尺寸来自各个供应商, 包括 Maxim 。目前, Maxim 和 Dallas Semiconductor推出的新型晶片级封装产品的标称尺寸如表 1 所列。

3 晶片级封装 (WLP) 技术

提供 WLP 器件的供应商要么拥有自己的 WLP生产线, 要么外包封装工艺。各种各样的生产工艺必须能够满足用户的要求, 确保最终产品的可靠性。美国亚利桑那州凤凰城的 FCI 、美国北卡罗莱纳州的 Unitive 建立了 WLP 技术标准, 产品名为 UltraCSP (FCI) 和 Xtreme (Unitive) 。 Amkor 在并购 Unitive后, 为全世界半导体行业提供 WLP 服务。

在电路 / 配线板上, 将芯片和走线连接在一起的焊球最初采用锡铅共晶合金 (Sn63Pb37) 。为了减少电子产品中的有害物质 (RoHS) , 半导体行业不得不采用替代材料, 例如无铅焊球 (Sn96.5Ag3Cu0.5) 或者高铅焊球 (Pb95Sn5) 。每种合金都有其熔点, 因此, 在元器件组装回流焊工艺中, 温度曲线比较特殊, 在特定温度上需保持一段时间。

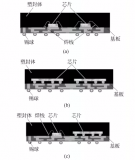

集成电路的目的在于提供系统所需的全部电子功能, 并能够装配到特定封装中。芯片上的键合焊盘通过线键合连接至普通封装的引脚上。普通封装的设计原则要求键合焊盘位于芯片周界上。为避免同一芯片出现两种设计 ( 一种是普通封装,另一种是 CSP) , 需要重新分配层连接焊球和键合焊盘。

4 晶片级封装器件的可靠性

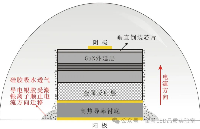

晶片级封装 ( 倒装芯片和 UCSP) 代表一种独特的封装外形, 不同于利用传统的机械可靠性测试的封装产品。封装的可靠性主要与用户的装配方法、电路板材料以及其使用环境有关。用户在考虑使用 WLP 型号之前, 应认真考虑这些问题。首先必须进行工作寿命测试和抗潮湿性能测试, 这些性能主要由晶片制造工艺决定。机械压力性能对WLP 而言是比较大的问题, 倒装芯片和 UCSP 直接焊接后, 与用户的 PCB 连接, 可以缓解封装产品铅结构的内部压力。因此, 必须保证焊接触点的完整性。

5 结束语

目前的倒装芯片和 CSP 还属于新技术, 处于发展阶段。正在研究改进的措施是将采用背面叠片覆层技术 (BSL) , 保护管芯的无源侧, 使其不受光和机械冲击的影响, 同时提高激光标识在光照下的可读性。除了 BSL , 还具有更小的管芯厚度, 保持装配总高度不变。 Maxim UCSP 尺寸 ( 参见表 1) 说明了 2007年 2 月产品的封装状况。依照业界一般的发展趋势, 这些尺寸有可能进一步减小。因此, 在完成电路布局之前, 应该从各自的封装外形上确定设计的封装尺寸。

此外, 了解焊球管芯 WLP 合金的组成也很重要, 特别是器件没有声明或标记为无铅产品时。带有高铅焊球 (Pb95Sn5) 的某些器件通过了无铅电路板装配回流焊工艺测试, 不会显著影响其可靠性。采用共晶 SnPb 焊球的器件需要同类共晶 SnPb 焊接面, 因此, 不能用于无铅装配环境。

审核编辑 黄宇

-

封装

+关注

关注

128文章

9332浏览量

149047 -

倒装芯片

+关注

关注

1文章

124浏览量

16872 -

晶片级

+关注

关注

0文章

2浏览量

5675 -

wlp

+关注

关注

0文章

18浏览量

11021

发布评论请先 登录

超细间距倒装芯片灌封胶渗透与空洞控制 |铬锐特实业

决战纳米级缺陷!东亚合成IXEPLAS纳米离子捕捉剂如何助力先进封装?

聊聊倒装芯片凸点(Bump)制作的发展史

汉思新材料取得一种系统级封装用封装胶及其制备方法的专利

什么是晶圆级扇入封装技术

理解倒装芯片和晶片级封装技术及其应用

理解倒装芯片和晶片级封装技术及其应用

评论