chiplet和cowos的关系

Chiplet和CoWoS是现代半导体工业中的两种关键概念。两者都具有很高的技术含量和经济意义。本文将详细介绍Chiplet和CoWoS的概念、优点、应用以及两者之间的关系。

一、Chiplet的概念和优点

Chiplet是指将一个完整的芯片分解为多个功能小芯片的技术。简单来说,就是将一个复杂的芯片分解为多个简单的功能芯片,再通过互联技术将它们组合在一起,形成一个整体的解决方案。

Chiplet技术的优点主要有以下几点:

1. 提高芯片的灵活性。芯片中的各个模块可以独立升级,从而提高芯片的灵活性和可维护性。

2. 降低芯片设计的难度。芯片优化和设计变得更加容易,设计团队可以将自己的核心专业领域内的复杂问题分解成简单的部分进行解决。

3. 降低制造成本。芯片的制造分解成多个芯片,每个小芯片的生产成本会比整个芯片的生产成本低。

4. 提高生产效率。芯片生产分解成多个小芯片后,每个模块的制造可以并行进行,从而缩短生产周期。

二、CoWoS的概念和优点

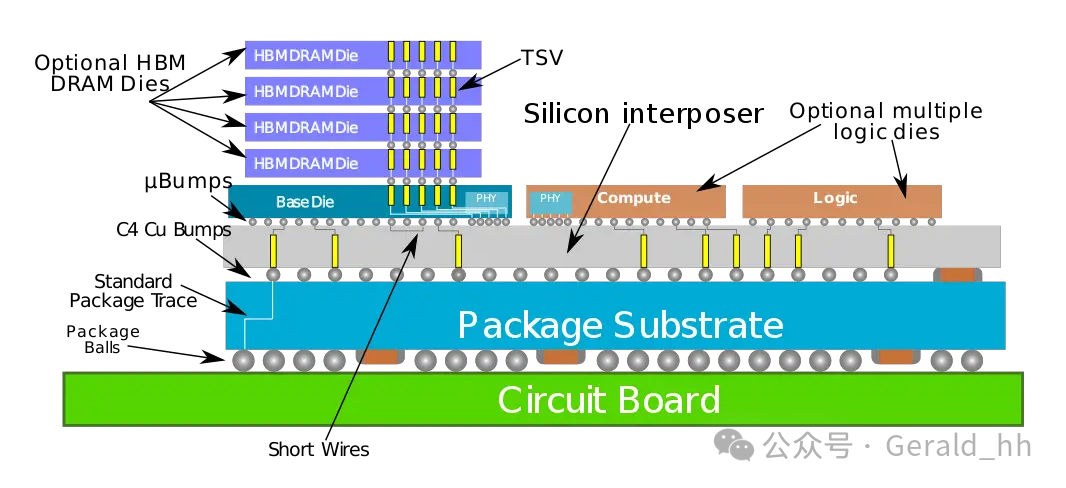

CoWoS(Chip On Wafer On Substrate)是一种三维堆叠技术。顾名思义,便是通过将多个芯片堆叠在晶圆上形成一个整体的芯片。具体而言,通过将低功耗芯片、高性能芯片和其他功能芯片组合在一起,实现芯片级封装。

CoWoS技术的优点主要有以下几点:

1. 提高芯片的集成度。通过堆叠多个芯片,可以实现芯片级封装,使整个芯片结构更加紧凑。

2. 降低芯片功耗。芯片的多层堆叠可以实现更好的功耗控制,从而提高芯片的能效比。

3. 提高芯片工作速度。通过使用高速通信总线,可以实现堆叠芯片之间的高速数据传输,从而提高芯片的工作速度。

4. 提高芯片的稳定性。采用三维堆叠的技术可以提高芯片的稳定性,降低故障率。

三、Chiplet和CoWoS的应用

Chiplet和CoWoS技术在现代半导体工业中有着广泛的应用。其中,Chiplet技术主要应用于AI芯片、网络芯片、计算芯片、存储芯片等领域,主要的目的是提高芯片的灵活性和可维护性,同时降低芯片设计和制造的难度和成本。CoWoS技术主要应用于高性能计算、图像处理、高速通讯、高密度存储和人工智能等领域,主要目的是降低芯片功耗,提高芯片的集成度和工作速度,提高芯片的稳定性。

四、Chiplet和CoWoS的关系

Chiplet和CoWoS是两种不同的技术,在不同的领域有不同的应用。但是,两者都是为了提高芯片的灵活性、可维护性和性能而产生的技术。Chiplet技术通过分解芯片的复杂性,使芯片的设计和制造更加简单易行;而CoWoS技术则是通过将多个芯片堆叠在一起实现芯片级封装,从而提高芯片的集成度和工作速度。

综合来看,Chiplet和CoWoS两种技术都具有很高的技术含量和经济意义,都是现代半导体工业中的重要组成部分。两者之间并不存在绝对的等价关系,而是各自的应用范围和优点有所不同。在今后的半导体工业中,Chiplet和CoWoS的发展将继续不断地推动着芯片技术的飞速发展。

-

存储器

+关注

关注

39文章

7757浏览量

172207 -

芯片设计

+关注

关注

15文章

1172浏览量

56780 -

CoWoS

+关注

关注

0文章

170浏览量

11536 -

AI芯片

+关注

关注

17文章

2164浏览量

36869 -

chiplet

+关注

关注

6文章

499浏览量

13650

发布评论请先 登录

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展

多Chiplet异构集成的先进互连技术

【深度报告】CoWoS封装的中阶层是关键——SiC材料

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

AI芯片发展关键痛点就是:CoWoS封装散热

先进封装市场迎来EMIB与CoWoS的格局之争

CoWoS产能狂飙的背后:异质集成芯片的“最终测试”新范式

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

解构Chiplet,区分炒作与现实

HBM技术在CowoS封装中的应用

CoWoP能否挑战CoWoS的霸主地位

chiplet和cowos的关系

chiplet和cowos的关系

评论