- 亚稳态

跨时钟域(CDC)的应从对亚稳定性和同步性的基本了解开始。用普通的话来说,亚稳定性是指不稳定的中间状态,但是在此状态下,任何微小的扰动将导致最终状态变为稳定状态,但是并不能保证最终的状态就是设计所期待的状态,换句话就是可能发生传输错误。当应用于数字电路中的触发器时,它表示触发器的输出可能尚未稳定,不确定是否能到最终期望值的状态。

触发器进入亚稳态的一种方法是违反了其建立或保持时间。在异步时钟域跨越(CDC)中,其中源时钟和目标时钟没有频率关系,来自源域的信号在驱动目的域的触发器时,无法保证目的域的触发器能够满足建立时间和保持时间。当目的域的触发器的输出变为亚稳态并且在必须再次对其输出进行采样(由目标域中的第二个触发器完成)时尚未收敛,则将发生同步失败。更糟糕的是,下一个触发器也可能变为亚稳态,从而导致亚稳定性在设计中传播!

- 跨时钟域同步器

同步器是跨时钟域中设计的一种常用电路,其目的是把同步失败的可能性降到最低。我们希望亚稳态在一个同步周期(目标时钟域的时钟周期)内解决,以便我们可以在目标时钟域中使得触发器的输出是安全采样值。在此我们把同步器的两次采样出现问题之间的时间间隔,称为平均故障间隔时间(MTBF)。

在跨时钟域(CDC)中出现亚稳态的概率与以下因素成正比:

- 目标时钟域的时钟频率

- 跨时钟边界的数据传输速率

根据上述因素,我们常用的同步器电路如下:

-

两个触发器同步器

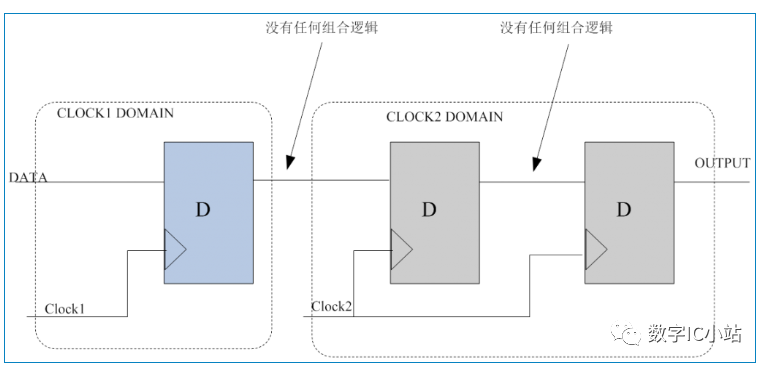

最基本的同步器是两个串联的触发器,均由目的时钟域提供时钟。这个电路称为两个触发器同步器。如果输入数据的变化非常接近接收时钟边沿(在建立/保持时间内),则同步器中的第一个触发器可能会变为亚稳态,但是在信号被采样之前,仍然有一个完整的时钟使信号变得稳定--第二触发器。然后,目标时钟域的逻辑使用的是第二个触发器的输出。

两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立/保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 <= 时钟周期。如果不满足上述表达式,那么到第二个触发器开始,信号仍然可能是亚稳态的。在这种情况下,将发生同步错误,并且设计可能会发生故障,但是这种情况是很罕见的。

两个触发器同步器足以满足很大部分应用的需求了。为了进一步提高MTBF,有时会使用具有更好的建立/保持时间特性的库单元(其具有低阈值电压)构建两个触发器同步器。

在跨时钟域(CDC)发送信号到同步器之前,通常先在源时钟域中使用寄存器保存信号。这也是为什么上图中介绍为什么在两个时域的触发器之间需要没有组合逻辑的原因,只有这样才可以首先消除了组合电路产生的毛刺。如下图所示:

因为在组合逻辑电路中常常因为各个输入信号的不一致性以及各路径延迟的不一样,可能导致输出结果存在毛刺。

而在跨时钟域时,又不确定目的时钟域时钟上升沿什么时候到来,因此目的时钟域时钟的采样就更加无法保证。

因此必须保证两个时域的触发器之间没有组合逻辑。

- 慢时钟域到快时钟域

最简单的情况是将信号从慢速时钟域传递到快速时钟域。只要快时钟的频率大于慢时钟频率的1.5-2倍,通常就不会有问题。快速目标时钟将简单地对慢速信号进行多次采样。在这些情况下,一个简单的两级串联触发器同步就足够了。

目的时钟域如果不采取任何操作,那么就会多次采样同一个值,这会导致一个问题--电路误以为这是多个操作。因此为了避免这种错误的发生,通常添加一些简单的逻辑使得同步后的采样值出现周期和原时钟域的一样。具体操作,在soc设计方法与实现书上有讲。

如果快时钟的频率小于慢时钟频率的1.5倍,也就是稍微快点,这个欢迎各位讨论,我觉得使用。

- 快时钟域到慢时钟域

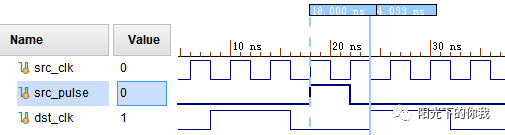

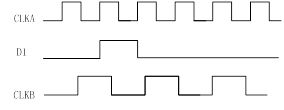

困难的情况是将快速信号传递到慢速时钟域。明显的问题是,如果快速信号上的脉冲短于慢速时钟的周期,则该脉冲可能会在被慢速时钟采样之前消失。下面的波形显示了这种情况。

还有一个考虑较少的问题是,即使脉冲只是比慢时钟的周期稍宽,信号也会在目标触发器的建立/保持时间内(在慢时钟上)变化,这会违反时序并导致亚稳性。

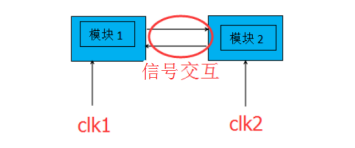

在处理上述问题时,首先应该确认是否需要源信号中的每个值,如果可以不需要,那么采样在上文异步fifo中设计的格雷码就可以异步FIFO设计。当然如果需要在目的域中使用每个值,那么就得想办法设计新方法。

- 还是使用两级触发器

一个简单的两个触发器同步器是跨时钟域交叉传输信号的最快方法。只要在快速时钟域中生成的信号比慢速时钟的周期时间宽,在许多应用中就足够了。例如,如果只需要同步缓慢变化的状态信号,则可能会起作用。一个安全的经验法则是信号必须大于目标时钟周期宽度的1.5倍。这保证了信号将被目标时钟的至少一个(但可能更多)时钟沿采样。可以使用SystemVerilog断言(SVA)轻松检查需求。

当源和目标的相对时钟频率固定时,很容易实现1.5x的周期宽度。但是在现实世界中,情况并非如此。目标时钟可以采用多种不同的频率,它们可以与源时钟更快/更低/相同。在那种情况下,设计时钟域交叉信号来满足最慢目标时钟的1.5倍周期宽度并不容易。

- 采用具有反馈信号的同步器

上图中,源域通过两个触发器同步器将信号发送到目的时钟域,然后通过另一个两个触发器同步器将同步信号传递回源时钟域,作为反馈确认。下图显示了同步器的波形。

该解决方案非常安全,但是由于在允许再次更改信号之前需要在两个方向上进行同步,因此确实存在增加延迟的代价。

-

SoC设计

+关注

关注

1文章

151浏览量

19473 -

MTBF

+关注

关注

1文章

30浏览量

14025 -

CDC

+关注

关注

0文章

58浏览量

18512 -

触发器

+关注

关注

14文章

2050浏览量

63042 -

同步器

+关注

关注

1文章

117浏览量

15527

发布评论请先 登录

从电路的角度出发,提出了一种新的SOC跨时钟域同步电路设计的方法

跨时钟域电路设计:多位宽数据通过FIFO跨时钟域

跨时钟域电路设计—单比特信号传输

跨时钟域电路设计—单比特信号传输

评论