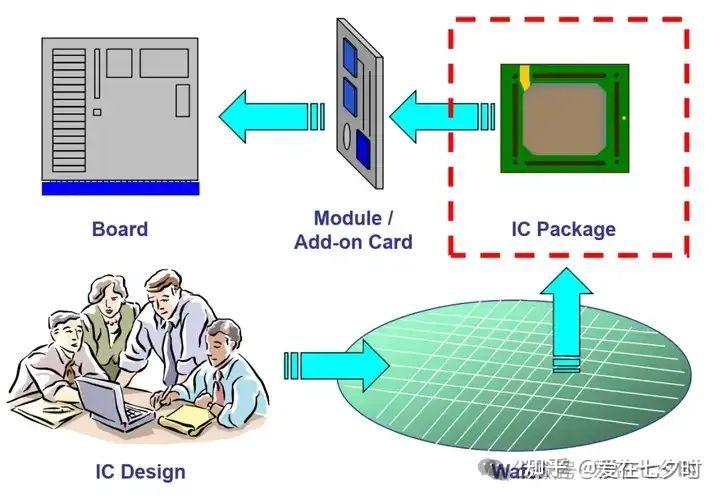

半导体集成电路封装起着安装、固定、密封、保护芯片和增强电热性能的作用。另一方面,它通过芯片上的触点连接到封装外壳的引脚,这些引脚通过印刷电路板上的导线与其他器件连接,从而实现内部芯片与外部电路的连接。同时,芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀导致电气性能下降。本篇【科准测控】小编主要介绍一下半导体集成电路封装工艺的流程有哪些,一起往下看吧!![]

封装工序一般可以分成两个部分:包封前的工艺称为装配(Assembly)或称前道工序(Front End Operation),在成型之后的工艺步骤称为后道工序(Back End Operation)。在前道工序中,净化级别控制在100~1000级。在有些生产企业中,成型工序也在净化控制的环境下进行。典型的封装工艺流程如图2-1所示。

磨片 : 磨片之前,在硅片表面贴一层保护膜以防止磨片过程中硅片表面电路受损。磨片就是对硅片背面进行减薄,使其变薄变轻,以满足封装工艺要求。磨片后进行卸膜,把硅片表面的保护膜去除。

划片(Dicing) : 在划片之前进行贴膜,就是要用保护膜和金属引线架将硅片固定。再将硅片切成单个的芯片,并对其检测,只有切割完经过检测合格的芯片可用。

装片(Die Attaching) : 将切割好的芯片从划片膜上取下,将其放到引线架或封装衬底(或基座)条带上。

键合(Wire Bonding) : 用金线将芯片上的引线孔和引线架衬垫上的引脚连接,使芯片能与外部电路连接。

塑封(Molding) : 保护器件免受外力损坏,同时加强器件的物理特性,便于使用。然后对塑封材料进行固化(Curing),使其有足够的硬度与强度经过整个封装过程。

电镀(Plating) : 使用Pb和Sn作为电镀材料进行电镀,目的是防止引线架生锈或受到其他污染。然后根据客户需要,使用不同的材料在封装器件表面进行打印(Marking),用于识别。

切筋/打弯(Trimming/Forming) : 去除引脚根部多余的塑膜和引脚连接边,再将引脚打弯成所需要的形状。

测试∶ 全面检测芯片各项指标,并决定等级。

包装 : 根据测试结果,将等级相同的放进同一包装盒。

仓检 : 人库和出库检验。

出货 : 芯片出仓。

以上就是关于半导体集成电路封装工艺流程的简单介绍了。小编后续会对磨片、划片、装片、键合、塑封、电镀、切筋/打弯、测试以及包装这几个封装工艺流程进行详细的描述,有需要了解的朋友可以继续关注哦~如果您对半导体、集成电路或者芯片、推拉力测试机有什么不明白的问题,欢迎给我们私信或留言,科准测控的技术团队也会为您解答疑惑!

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54429浏览量

469367 -

半导体

+关注

关注

339文章

31238浏览量

266576 -

封装

+关注

关注

128文章

9330浏览量

149047

发布评论请先 登录

85页PPT,看懂芯片半导体的封装工艺!

华进半导体荣登2025中国集成电路新锐企业50强榜单

半导体“封装过程”工艺技术的详解;

集成电路制造中薄膜刻蚀的概念和工艺流程

PDK在集成电路领域的定义、组成和作用

集成电路传统封装技术的材料与工艺

42.5亿,重庆半导体大动作,8个集成电路领域头部企业集中签约,包含2个传感器项目

现代集成电路半导体器件

【展会预告】2025 中国西部半导体展重磅来袭,华秋邀您 7 月 25-27 日西安共探集成电路新未来!

半导体封装工艺流程的主要步骤

半导体集成电路封装工艺的11个流程介绍!

半导体集成电路封装工艺的11个流程介绍!

评论