开发者在提升芯片性能和加速数据传输的道路上永远不会停歇,能够充分利用光的优势的光子学就是一个很好的切入方向。

曦智科技(Lightelligence)是全球领先的光子芯片和人工智能公司,成立于2017年。最近,曦智科技在开发一种复杂的Multi-Die系统级封装解决方案,致力于实现计算能力指数级提升的同时大幅降低能耗。

在真实的机器学习(ML)工作负载下预测系统性能和功耗非常困难,因此开发团队需要一个现代化的解决方案来帮助定义执行ML工作负载的整个系统架构。理想情况下,该解决方案可以有效地对定制SoC(由数字组件、模拟组件和光学组件构成)的性能进行建模。

现在先进的SoC中都包含许多互联组件,这些都必须经过整体验证从而确保系统能够按预期运行。传统的方法是手动完成相关工作,包括使用静态电子表格计算。另一种方法则是使用新思科技的Platform Architect,一种动态仿真解决方案。Platform Architect不仅能够提供SoC架构分析还可以对性能和功耗进行优化。

曦智科技已经在其SoC设计中使用了Platform Architect。借助该解决方案,曦智科技的开发团队生成了AI工作负载模型来执行其应用要求规范,以创建硬件架构(包括总线网络拓扑)的性能模型。内置的分析工具让团队效率大幅提升。

曦智科技表示,与基于电子表格的分析方法相比,Platform Architect解决方案的结果保真度更高,并且可以比传统方法更快地获得架构分析结果。

观看视频,了解曦智科技是如何利用Platform Architect加速其复杂SoC的架构设计的。

-

新思科技

+关注

关注

5文章

981浏览量

52998

原文标题:光子芯片公司如何轻松搞定复杂Multi-Die设计?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

JCMsuite应用:空心光子晶体光纤

新思科技携手Socionext实现3DIC芯片成功流片

新思科技发布全新软件定义硬件辅助验证解决方案

软件定义的硬件辅助验证如何助力AI芯片开发

新思科技Multi-Die方案助力车企迈向汽车电子新时代

新思科技助力UCIe 3.0快速落地

新思科技以AI驱动EDA加速Multi-Die创新

新思科技斩获2025年台积公司开放创新平台年度合作伙伴大奖

面向芯粒设计的最佳实践

增加语音控制功能关注这几颗芯片轻松搞定

宏集HMI-4G套装,轻松搞定“数据上云+异地远程运维”

新思科技UCIe IP解决方案实现片上网络互连

新思科技网页端虚拟原型工具的工作流程

新思科技与三星深化合作加速AI和Multi-Die设计

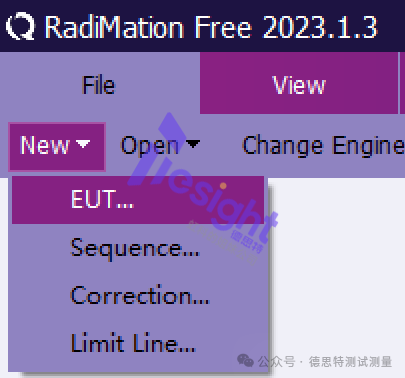

手把手教你用RadiMation进行MIMO功率测量,轻松搞定射频测试!

光子芯片公司如何轻松搞定复杂Multi-Die设计?

光子芯片公司如何轻松搞定复杂Multi-Die设计?

评论