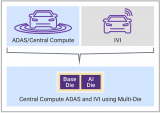

芯片已从单一整体式芯片发展为集成多个芯粒的 Multi-Die 设计,其中每个芯粒都针对处理、内存和数据传输等特定功能进行了优化。

随着芯粒供应商生态持续扩展,客户希望根据架构设计、供应链策略、成本控制等因素灵活组合芯粒方案。在此背景下,芯片间实现快速、可靠、安全通信的需求空前迫切。

UCIe 标准正是为满足这一需求而制定。它定义了裸片间互连的通用接口,实现了不同供应商解决方案和工艺节点之间的互操作性。

最近发布的 UCIe 3.0 实现了跨越式发展,其性能较 UCIe 2.0 提升至两倍,系统级控制也得到了改进,并支持新的应用场景。

新思科技作为通用芯粒互联产业联盟的成员和标准制定的主要贡献者,始终处于 UCIe 创新和应用的前沿。我们的经过硅验证的完整 IP 已适配 UCIe 标准的最新版本。

借助我们的 UCIe PHY、控制器和验证 IP ,客户可轻松将 UCIe 3.0 引入设计中,缩短产品上市时间。

为何需要 UCIe 3.0

UCIe 的问世是 Multi-Die 设计领域的一个重要里程碑。它通过确立通用的 Die-to-Die 接口,使得在同一封装内集成来自不同供应商和工艺节点的芯粒成为可能。这一基础推动了芯粒在设计中的首次广泛应用。

随着 Multi-Die 架构日益盛行,业界对 UCIe 标准的期望也水涨船高。如今,为了支持更广泛的性能范围、功耗包络和应用需求,设计团队开发的系统日趋复杂。每个封装中集成了更多裸片以应对高级工作任务,因而要求更快的连接速度和更紧密的系统级协同。

因此,UCIe 变得愈发重要。除了互操作性之外,UCIe 还需要支持可预测性、高能效和规模化。随着 Multi-Die 设计在人工智能(AI)、高性能计算(HPC)和汽车等领域从试用阶段迈入量产,UCIe 标准也需要同步演进,以便更全面地支持这些应用场景。

UCIe 3.0 正是演进过程中的最新进展,它为顺应 Multi-Die 设计的发展趋势而制定。我们已将支持新标准作为首要任务,并为此提供芯片就绪型 IP 和 EDA 流程。

UCIe 3.0的新特性

UCIe 3.0 引入了多项重大升级,满足了现代 Multi-Die 设计的带宽、延迟和系统集成要求。

其中最引人注目的变化是速度:UCIe 3.0 将最大数据速率从 32 GT/s 提高一倍,达到 64 GT/s。在 AI 推理、内存与 I/O 解耦及高速加速器结构等数据密集型应用中,可显著提升系统性能。但是,单凭速度并不能解决系统级挑战。

为了改善更高数据速率下的功耗和可靠性,UCIe 3.0 引入了运行时重新校准,使得链路能够适应运行期间的漂移和环境变化。此特性有助于保证信号质量,无需设置过宽的保护裕度。

另一项重大改进是边带信号传输距离扩展至 100 毫米。从而能够支持更复杂的拓扑结构,芯粒之间的物理距离可以更大。

其他新特性包括固件预先下载和通过边带信道传递确定性优先级消息。这两个特性都有助于缩短系统初始化时间,提高启动和运行期间的系统响应速度。

助力UCIe 3.0快速落地

为了支持 UCIe 3.0,需要一套能够全速协同工作的 IP、验证和设计解决方案。

我们的 UCIe PHY IP 已在台积公司和三星先进节点上完成流片(tape-out),可同时支持标准和先进封装流程。PHY 用于高速、低功耗操作,内置了对运行时重新校准和边带信号传输的支持。当与支持 PCIe、CXL 和定制串流协议的灵活控制器 IP 配合使用时,PHY 解决方案可帮助工程团队调整 UCIe 设计,以精准适配特定的工作负载和系统架构。

我们还为 UCIe 提供了验证 IP,用于模拟链路行为、协议正确性和系统级交互,包括固件预先加载和确定性边带控制等新特性。这些验证 IP 与我们的硬件加速仿真和原型平台(ZeBu 和 HAPS)集成,可在流片之前验证Die-to-Die 连接。

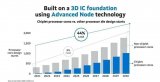

我们针对芯片/封装协同设计,提供了统一的“探索到签核”平台 3DIC Compiler,能够整合所有环节。它使团队能够以 UCIe 链路为第一等元素来设计布局图、布线和封装几何形状,从而有效管理因性能扩展而带来的复杂性。

早期势头与未来展望

早在 UCIe 3.0 正式发布之前,我们就与早期采用者合作,开发出具备更高带宽和先进系统协同能力的设计。如今,随着新标准正式公布,合作进展持续加速。

芯粒生态仍在持续演进,能否成功普及和应用将有赖于全面的支持和赋能,即在芯片与系统层面实现 IP、工具和验证的无缝整合。

依托 UCIe 3.0 和新思科技,未来蓝图正在逐步实现。新思科技将持续推动 UCIe 标准的演进,助力客户实现更高效的多芯粒系统设计。

-

新思科技

+关注

关注

5文章

979浏览量

52989 -

AI芯片

+关注

关注

17文章

2164浏览量

36869 -

chiplet

+关注

关注

6文章

499浏览量

13650

原文标题:性能翻倍!新思科技发布UCIe 3.0,为AI芯片与Chiplet架构注入新动能

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新思科技2026 HAV硬件加速验证技术开放日深圳站圆满落幕

新思科技助力Arm Zena CSS快速落地的完整VDK平台

新思科技首届Converge大会隆重举行

格罗方德收购新思科技处理器IP产品组合

H5412B降压恒流智能调光IC 建筑照明落地灯48V转9V芯片方案

UCIe协议代际跃迁驱动开放芯粒生态构建

XMOS与飞腾云联袂以模块化方案大幅加速音频产品落地

新思科技助力UCIe 3.0快速落地

新思科技助力UCIe 3.0快速落地

评论