半导体领域正经历快速变革,尤其是在人工智能(AI)爆发式增长、对更高处理性能及能效需求持续攀升的背景下。传统的片上系统(SoC)设计方案在尺寸与成本方面逐渐触及瓶颈。此时,Multi-Die设计应运而生,将SoC拆分为多个称为芯粒的芯片,并集成到单一封装内,成功突破了上述限制。

基于芯粒的设计方案具备多项优势:在AI与高性能计算(HPC)应用中,通过将计算、存储与输入输出(I/O)功能解耦,助力提升计算能力;在汽车与边缘AI应用场景下,将大型芯片拆分为尺寸更小、更适配量产的元器件,从而提高生产良率与产品可靠性;借助对封装内部芯粒组合的灵活重构,能够快速推出新产品,缩短产品迭代周期。

芯粒设计最佳实践

对于考虑采用芯粒设计方案的开发者,以下是八项最佳实践:

从合理的系统分区入手

首先将系统设计拆解为计算、存储、I/O等功能模块,并明确哪些功能应作为独立芯粒存在。针对高性能元器件,选择先进的工艺节点;而对于性能要求较低的模块,则选用技术成熟、性价比高的工艺节点。在此过程中,需精心平衡速度、功耗与系统整体效率之间的权衡关系。此外,还应考虑系统的可扩展性,选择能够支持未来升级或功能变更的标准与接口。

为每个芯粒选择合适的工艺节点

并非所有功能皆可从最新技术中获得同等程度的提升。例如,存储器的微缩效率通常不及逻辑电路,因此在较成熟的工艺节点上制造存储器芯粒,既能降低成本,又不会影响性能。在集成芯粒时,需考虑芯粒应采用3D堆叠结构(以实现更低延迟与功耗),还是2.5D并排布局(以简化实现流程)。

精心规划Die-to-Die连接

选择合适的接口对芯粒间实现无缝通信至关重要。UCIe等行业标准在Die-to-Die连接领域的应用正日益广泛。设计时需确保连接带宽与系统所需的数据吞吐量相匹配,同时兼顾主数据与边带控制数据的传输需求。此外,还需精心规划封装内芯粒的布局与互连方式来优化物理结构,确保设计符合目标尺寸与形状要求。根据物理布局的不同,Die-to-Die接口可用的“边缘区域”(beachfront)面积会有所差异,可能需要采用不同的接口配置。切勿忽视热管理的重要性,单一封装内的多个芯粒可能产生热点,因此必须在设计中融入充足的冷却与散热方案。

了解先进的封装方案

选择合适的封装技术是实现设计目标的关键。封装方案涵盖从传统有机基板到支持更高密度与性能的先进中介层等多种类型。设计时需综合考虑外形尺寸与整体成本:先进封装方案通常具备更强的性能,但实施成本更高、复杂度也更大。要确保开发时间表预留足够时间用于全面测试与良率管理。每个芯粒都应单独测试,确保仅选择“已知合格芯粒”(KGD)进行最终组装。在Die-to-Die接口中加入冗余与修复功能,有助于提升组装、测试及量产阶段的封装良率。此外,需密切监控供应链,确保所有芯粒组件与封装材料的采购稳定可靠。

设计时融入安全考量

安全应作为所有基于芯粒的系统的基础要素。需确保每个芯粒都通过信任根(RoT)进行认证与锚定,以防止未授权访问,并安全管理密钥(尤其在多租户环境中)。通过加密技术与安全通信协议保护芯粒间传输的数据。同时,需规划安全启动流程,从硬件与软件两个层面防范篡改行为。

投入开展系统级设计与验证

尽早且高频率地开展系统级仿真与硬件辅助验证,有助于在硬件制造前发现集成问题,节省宝贵的时间与资源。采用软硬件协同设计模式,可加速开发进程,缩短产品上市时间。为单个芯粒与最终封装系统制定完善的测试计划也至关重要,这是确保可靠性与性能的关键。分级测试等新方法可用于评估单个芯粒,并验证其在Multi-Die设计中组装后的性能。此外,还需投入资源开展系统级热建模与串扰分析,以准确评估最终产品中的Multi-Die相互作用。

聚焦控制与管理系统

许多芯粒(尤其在数据中心环境中)可受益于专用的控制与管理系统。这类系统配备CPU,负责管理初始化、低速外设以及RoT等安全功能。通过收集、汇总与分发遥测数据,这类系统还能提升芯片的可靠性、可用性与可服务性(RAS)。

借力生态系统合作伙伴与专业技术

由于芯粒技术与方案仍相对较新且在持续演进,与经验丰富的伙伴合作至关重要。新思科技等行业领导者不仅提供经过硅验证的IP解决方案,还提供设计服务与封装指导。这些IP解决方案正与Arm计算子系统(CSS)集成,以进一步加快芯粒开发速度、降低风险。及时了解最新的芯粒标准也同样关键:通用UCIe联盟、JEDEC等行业组织会提供关于芯粒技术新进展的重要更新与资源;而imec、ASRA等机构则在为汽车行业制定专门的芯粒提案与指导规范。

释放基于芯粒设计的优势

基于芯粒的设计方案为打造下一代高性能系统提供了灵活且可扩展的路径。设计团队通过遵循上述最佳实践,能够从容应对(芯粒设计的)复杂性,充分发挥基于芯粒方案的优势。若需在整个芯粒开发周期(从概念构思到产品落地)中获取专业指导,建议与精通从芯片到系统集成全领域的专家展开合作。

-

半导体

+关注

关注

336文章

29985浏览量

258297 -

AI

+关注

关注

89文章

38108浏览量

296653 -

新思科技

+关注

关注

5文章

925浏览量

52639 -

芯粒

+关注

关注

0文章

81浏览量

395

原文标题:Multi-Die设计不踩坑指南:经市场认证的八个关键点

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

UCIe协议代际跃迁驱动开放芯粒生态构建

爱芯元智荣获2025金辑奖最佳技术实践应用奖

芯粒技术的专利保护挑战与应对策略

技术资讯 I 基于芯粒(小晶片)的架构掀起汽车设计革命

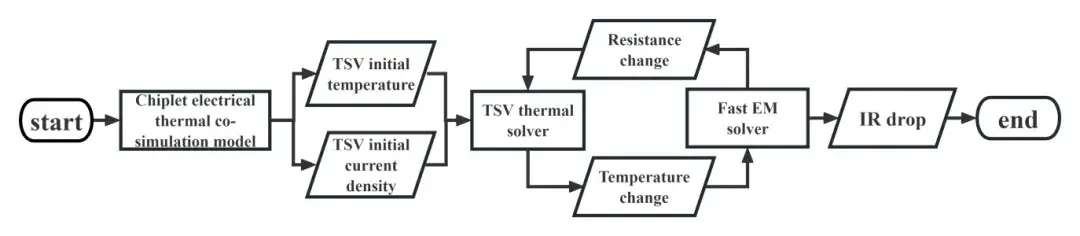

微电子所在芯粒集成电迁移EDA工具研究方向取得重要进展

行芯科技亮相第三届芯粒开发者大会

奎芯科技登场 COMPUTEX 2025,聚焦芯粒互连解决方案

面向芯粒设计的最佳实践

面向芯粒设计的最佳实践

评论