基于SelectIO的高速ADC时序实现

引言

本文通过以高速ADS42LB69芯片为例进行实战,利用SelectIO IP快速快速高效完成驱动的生成。关于SelectIO IP的使用,可以参考。

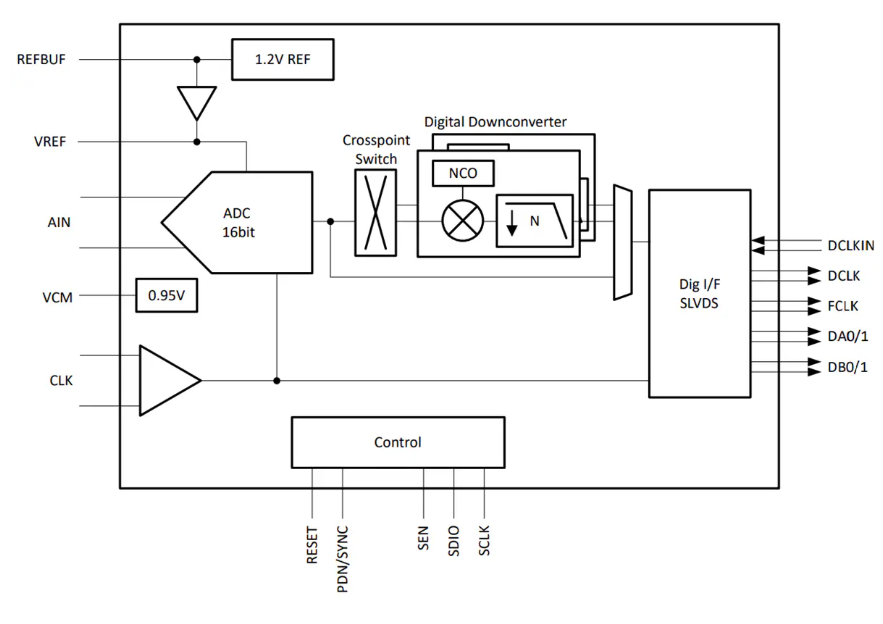

ADS42LB69

芯片简介

ADS42LB49和ADS42LB69是高线性度、双通道、14 和 16 位 250MSPS 模式转换器 (ADC) 系列,支持 DDR 和 QDR LVDS 输出接口。已缓冲模拟输入在大大减少采样保持毛刺脉冲能量的同时,在宽频率范围内提供统一的输入阻抗。采样时钟分频器可实现更灵活的系统时钟 架构设计。ADS42LBx9 以低功耗在宽输入频率范围内 提供出色的无杂散动态范围 (SFDR)。

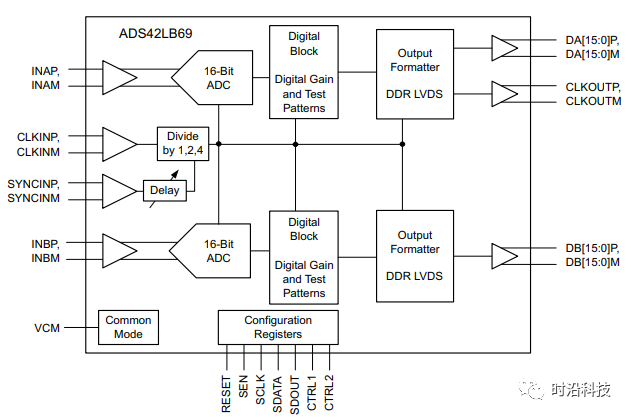

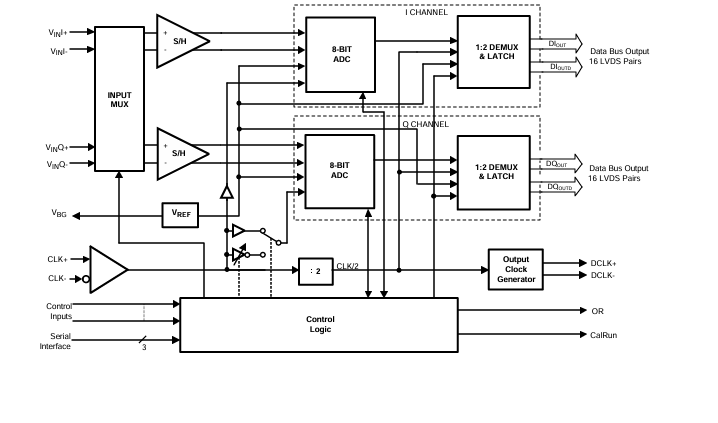

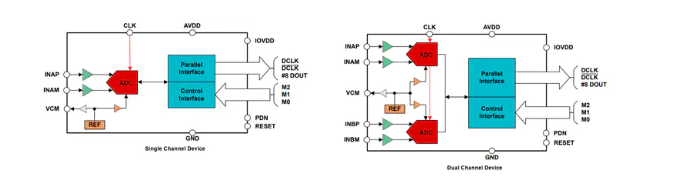

ADS42LB69功能框图

ADS42LB69功能框图

双通道

14和16位分辨率

最大时钟速率:250MSPS

支持高阻抗输入的模拟输入缓冲器

支持1分频,2分频和4分频的灵活输入时钟缓冲器

2VPP和2.5VPP差分满量程输入(SPI可编程)

双倍数据速率(DDR)或四倍数据速率(QDR)低压差分信令(LVDS)接口

功耗:820mW/通道

间隙抖动:85 fs

通道隔离:100dB

参数配置

用户可以根据自己的需求将数据接口通过SPI配置成QDR或DDR接口。在进行数据验证时,也可以使用测试模式,对收发数据进行验证以保证系统的正确性。另外,还可以对输入时钟进行延时调节或者通过SelectIO的delay、delayctrl功能对时钟信号进行微调,以满足时序要求。此方面不是本文重点,不做展开,更多内容参考官方data sheet。

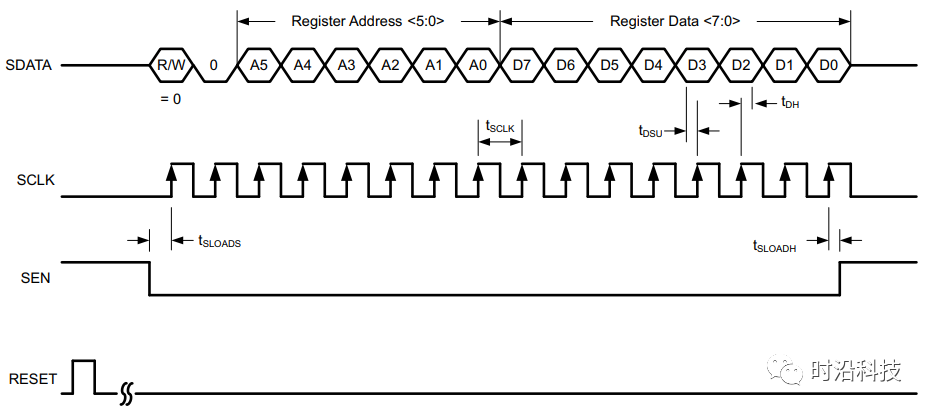

SPI时序

SPI时序引脚

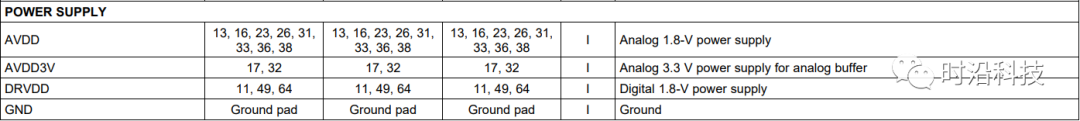

从下图可以看到,数据接口引脚采用1.8V供电,故数据接口为差分1.8V。

数据端口信号

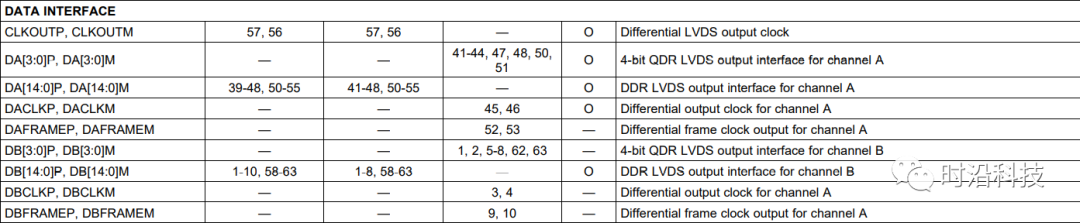

数据端口信号接口时序

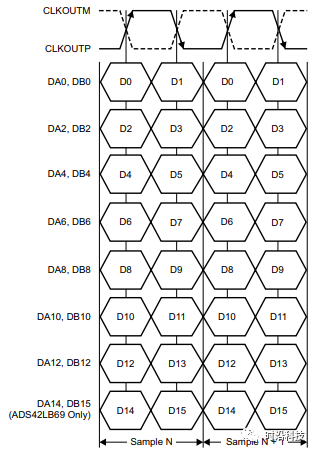

下图为ADS42LB69的DDR模式时序图,从图中可以看出有1对时钟接口,两个8对数据接口(DA与DB),每对数据接口分别在时钟的上升沿与下降沿采样,经过一个时钟周期可以捕获16位数据。

ADS42LB69的DDR模式时序图

ADS42LB69的DDR模式时序图SelectIO GUI配置

根据以上对ads42lb69的了解,就可以轻松的配置SelectIO IP的GUI界面了。

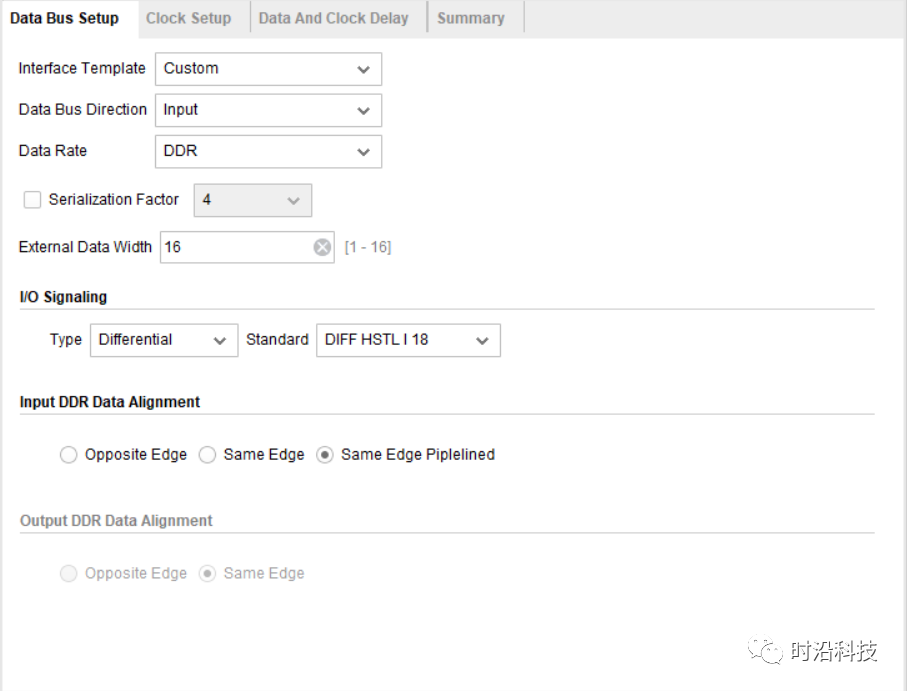

首先时钟接口与数据接口都是input,该时钟信号与RF模块时钟必须保持同源,以保证系统的相参性。由于ads42lb69采用DDR模式,且所有数据引脚都是并行,所以不选择串并转换器SERDES。

Data Bus Setup界面

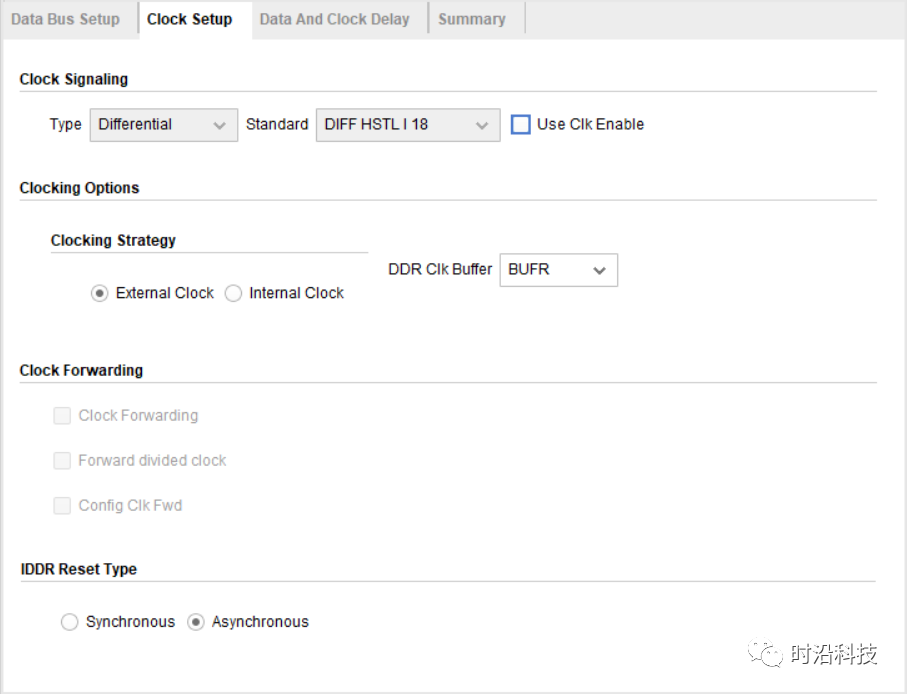

Data Bus Setup界面由于数据时钟来源于ads42lb69引脚,故选择外部时钟,而非FPGA内部时钟。

Clock Setup界面

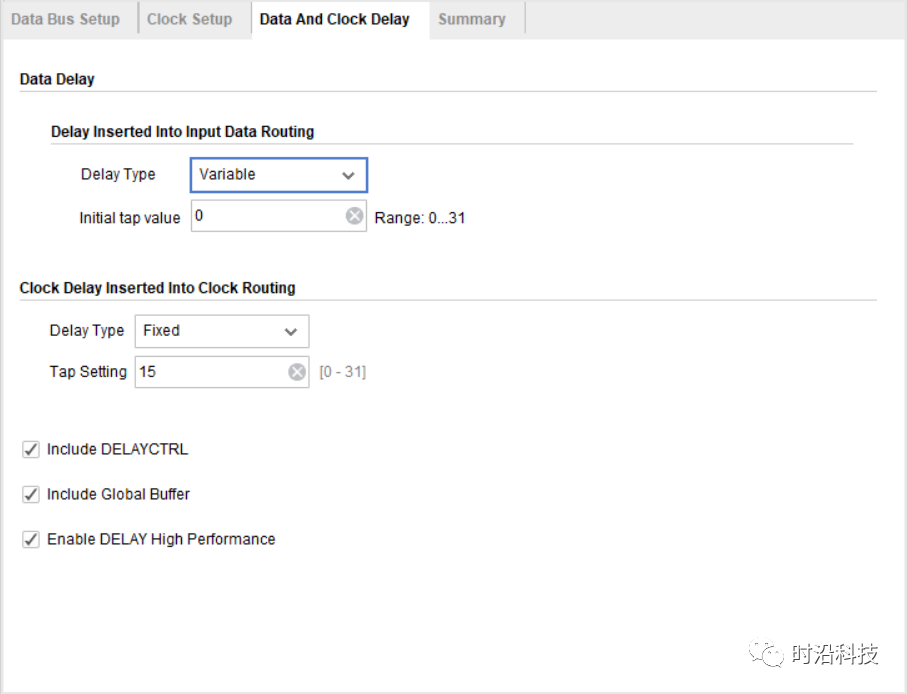

Clock Setup界面在实际处理高速数据时,往往存在由于布局布线导致的数据引脚之间的延时不相同,可以通过在每个数据引脚添加idelay、delayctrl模块对齐进行微调。或者,存在数据引脚与时钟引脚之间不对齐,通常对时钟引脚添加idelay、delayctrl模块对其进行微调。

Data And Clock Delay界面

Data And Clock Delay界面IP生成之后,通过右击选择Open IP Example Design进行仿真以加强理解,在线DEBUG调试延时模块,以达到设计要求。

-

芯片

+关注

关注

463文章

54373浏览量

468982 -

adc

+关注

关注

100文章

7942浏览量

556856 -

时序

+关注

关注

5文章

411浏览量

38997

原文标题:基于SelectIO的高速ADC时序实现

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

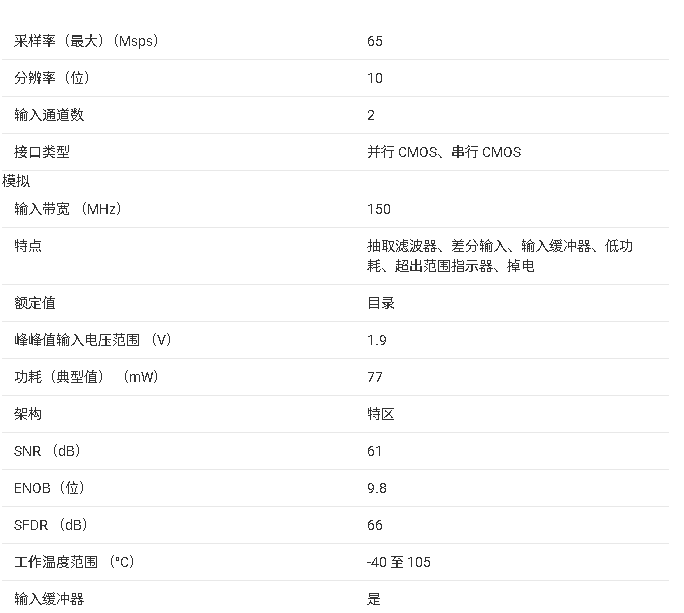

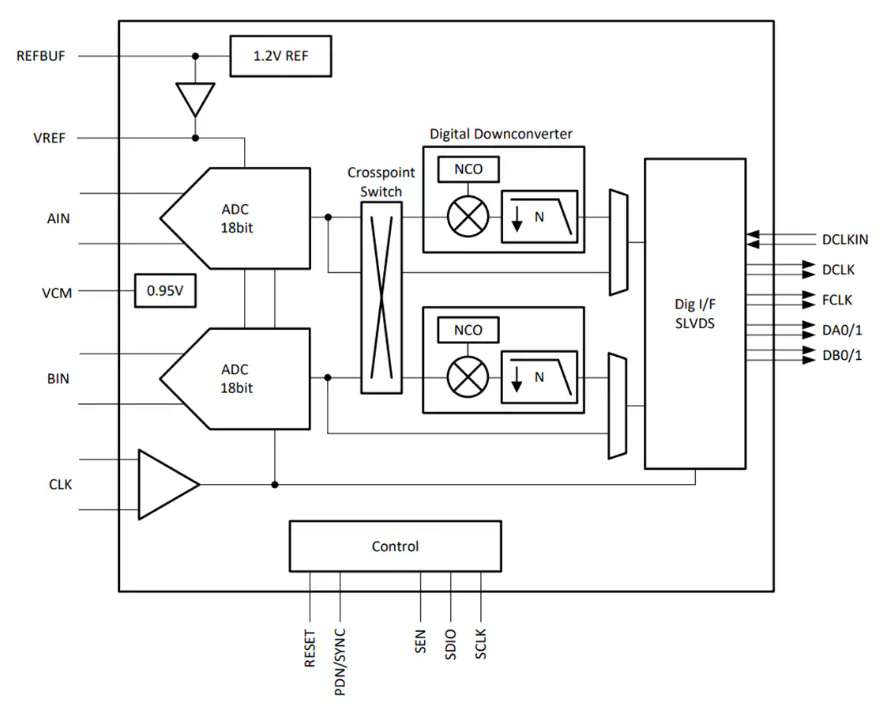

MAX153:高速8位ADC的卓越之选

12 位高速 ADC AD9432:性能剖析与应用指南

技术资讯 I AiPT与AiDT,高速设计的时序双引擎

12 位高速 ADC:AD9634 深度剖析与应用指南

AD4087:高速低噪SAR ADC的卓越之选

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

高速低功耗利器:ADC08D1500 ADC深度解析

ADC3910D065 10 位高速低功耗 ADC 技术文档总结

如何利用XPIO构建并实现带有Strobe的高速接口设计

Texas Instruments ADC368x系列:低噪声、低功耗18位高速ADC的技术解析

ADC356x系列16位高速ADC技术解析与应用指南

Texas Instruments ADC3908Dx/ADC3908Sx 8位高速ADC数据手册

基于SelectIO的高速ADC时序实现

基于SelectIO的高速ADC时序实现

评论