在 AMD Versal 自适应 SoC 器件中,SelectIO 是实现高速接口的重要组成部分。它为器件提供了灵活且高性能的通用 I/O 资源,支持多种工作模式,能够满足源同步接口、异步接口以及各类自定义接口的需求。高速接口设计中,源同步接口(Source-Synchronous Interface) 是一种常见方式,其特点是发送端不仅传输数据信号,还会同时发送一条或多条时钟或选通信号(Strobe),以帮助接收端在高速条件下实现精确的数据采样。

在 Versal 器件中,XPIO 提供了灵活的时钟与数据路径资源。本文将以源同步接口为例,说明如何利用 XPIO 构建并实现带有 Strobe 的高速接口设计。

XPIO 的内部架构

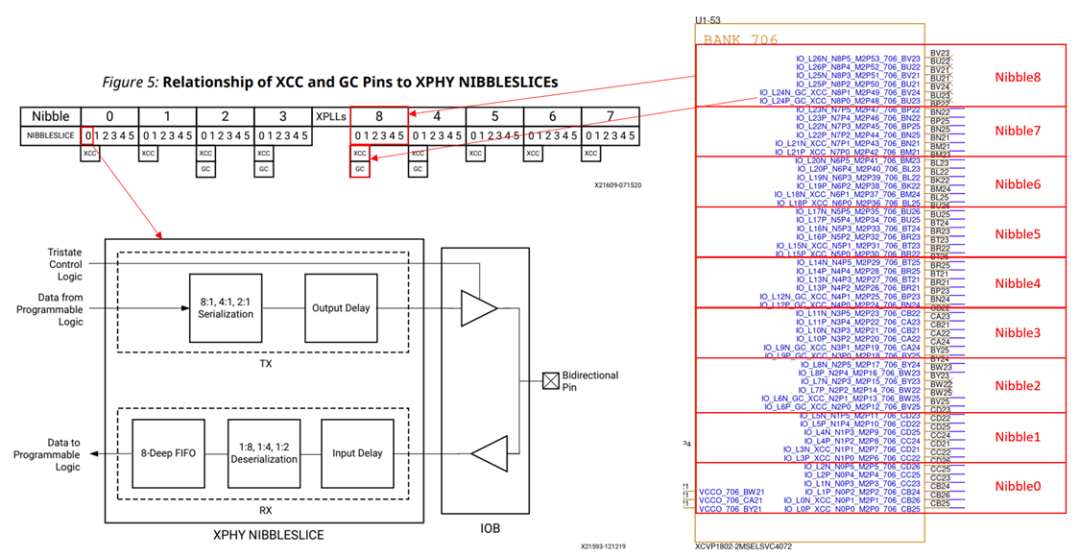

这里以 VP1802 的 Bank706 为例,如下图所示,一个 Bank 有9个 XPHY Nibble 和2个 XPLL 组成,每个 Nibble 有6个 NIBBLESLICE,对应6个引脚或3组差分对,每个 XPHY NIBBLESLICE 由串行器(Serializer)、解串器(Deserializer)、I/O 延迟单元和接收 FIFO 组成。

GC 和 XCC 管脚

GC 是全局时钟输入管脚,通常作为 XPLL 的时钟源,可以驱动同一 XPIO bank 内的所有 XPLL,以及相邻 Bank 内的 XPLL。

XCC 是 Strobe 的输入管脚,Strobe 通常是由对端的 TX 接口发送的。

在一个 Bank 中,只有 NIBBLESLICE [0] 和 NIBBLESLICE [1] 可以用作 GC 或 XCC 的输入。无论是单端还是差分,都必须从与 NIBBLESLICE [0] 关联的 I/O 引脚输入。如果时钟是差分信号,那么时钟的反相信号(输入到与 NIBBLESLICE [1] 关联的 I/O 引脚)应与输入到 NIBBLESLICE [0] 的 I/O 引脚的信号连接到同一个差分缓冲器。

时钟布线资源

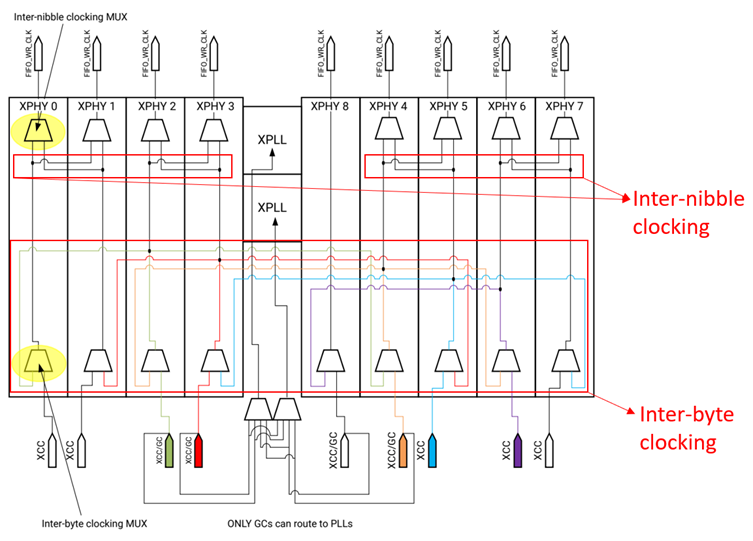

如果源同步接口有一路 Strobe 输入和多路 Data 输入,则可以利用 XPIO 内部的两种时钟资源( Inter-nibble clocking和 Inter-byte clocking)来转发 Strobe。当SERIAL_MODE 属性为 FALSE 时, Inter-nibble clocking 和 Inter-byte clocking 会被使能,适用于同步模式; SERIAL_MODE 属性为 TURE 时,每个 Nibble 的采样时钟都来自于 PLL_CLK 输入,适用于异步模式。

1.Inter-nibble clocking

Inter-nibble clocking 用于两个相邻 XHPY Nibble 对之间传递时钟。比如 Nibble0 和 Nibble1 在同一个 Nibble 对里面,它们可以相互使用对方的时钟。同样的还有 Nibble2 和 Nibble3、Nibble4 和 Nibble5 以及 Nibble6 和 Nibble7。但是 Nibble8 因为没有与之配对的 Nibble,因此也就不能通过 Inter-nibble clocking 资源与其他 Nibble 传递时钟,只能通过 Inter-byte clocking 来传递时钟。

2.Inter-byte clocking

Inter-byte clocking 支持在一个 Bank 中的两个特定非相邻的 Nibble 之间传递时钟,注意这里是特定的 Nibble,而不是所有的 Nibble 之间都可以传递。下面通过三个案例来做详细说明。

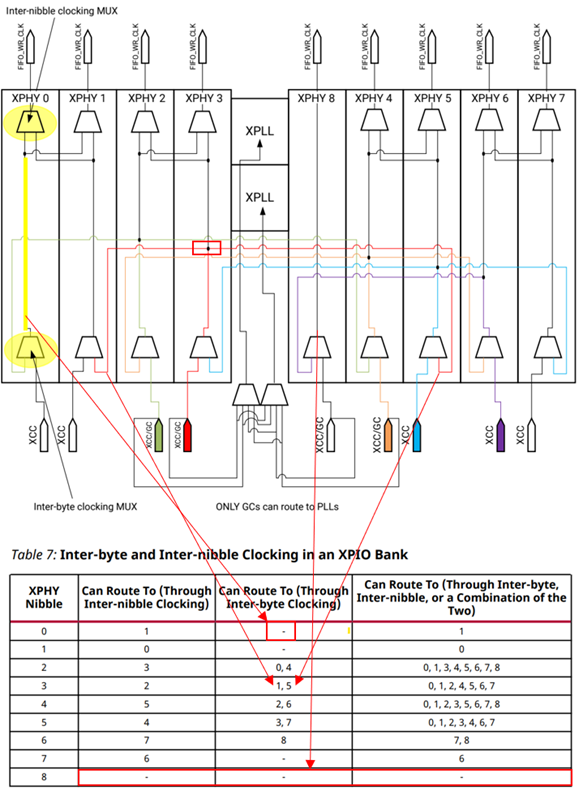

以 Nibble3 为例,它的 Inter-byte clocking MUX 的输出分别连到了 Nibble1 和 Nibble5 的 Inter-byte clocking MUX 输入端(下图红色线路),红框内的实心点表示水平与垂直线存在相交。因此对应到Table-7第五行第三列,Nibble3 的时钟可以通过Inter-byte clocking传递到Nibble1和Nibble5,在到达 Nibble5 之后还可以再通过 Nibble5 的 Inter-byte clocking 把时钟传递到 Nibble7,也就是上文所提到的特定 Nibble,而不是所有的 Nibble。

以 Nibble0 为例,它的 Inter-byte clocking MUX 的输出(下图黄色线路)只连到了 Inter-nibble Clocking MUX 的输入,没有与任何别的端口连接,因此 Nibble0 不能通过 Inter-byte Clocking 将自己的时钟传递到别的 Nibble,也对应了 Table-7第二行第三列的 “-” ,Nibble1 的原因相同。

以 Nibble8 为例,它的内部没有 Inter-nibble clocking MUX,Inter-byte clocking MUX 的输出直接连到了 XPHY 的外部,Nibble8 只能接收来自 Nibble2、Nibble4 和 Nibble6 传递过来的时钟,而无法将自己的时钟传递给别的 Nibble,正如在 Table-7 的最后一行的所示。

3.组合使用

组合使用两种时钟路径可以更加灵活地将时钟传递到其他 Nibble 中,比如要将 Nibble2 的时钟传递给 Nibble7,可以先通过 Nibble2的 Inter-byte clocking 把时钟输出到 Nibble4(上图绿色路径),再通过 Nibble4 的 Inter-byte clocking 把时钟输出到 Nibble6(上图橙色路径),最后通过 Nibble6 的 Inter-nibble clocking把时钟输出到 Nibble7。

注意组合使用存在一定的限制,Inter-byte clocking 的时钟输出可以连到 Inter-nibble clocking 再次传递,但是不能反过来操作,这与 XPHY 的结构有关。从上图 XPHY 的结构图中可以看到,Inter-byte clocking MUX 的输入是 XCC 或 GC,输出与 Inter-Nibble clocking MUX 相连,所以时钟传递的顺序就必须是先到 Inter-byte clocking,再到 Inter-Nibble clocking,反过来没有对应的时钟路径。

以 Nibble7 为例,当1个 XCC 时钟被连到 Nibble7 以后,它可以通过 Inter-Nibble clocking 被传递到 Nibble6,但是在这个时钟到达 Nibble6 以后就不能再被传递到其他 Nibble 中。因为 Nibble7 通过 Inter-Nibble clocking 输出的时钟没有任何路径可以再回到 Inter-byte clocking MUX的输入端。因此,如果希望时钟被灵活的传递到同一个 Bank 的多个 Nibble 中,选择 Nibble2、Nibble4 的 XCC 或 GC 输入是比较好的选择。

应用分析

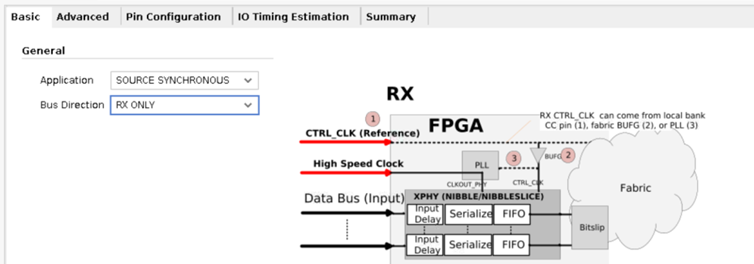

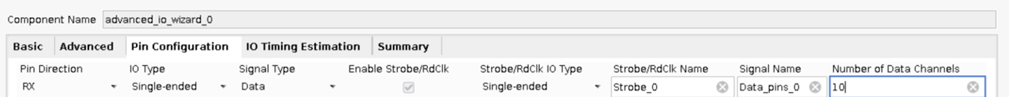

1.使用 Advanced IO wizard 生成 IP,这里需要注意以下几点:

Basic 页面,Application 有两个选项,分别是源同步和异步,这里选择源同步(SOURCE SYNCRONOUS)。Bus Direction 选择 RX ONLY,其余保持默认。

Pin Configuration 页面,这里需要设置 Data 通道的数量。因为 XPIO 的1个 Bank 有9个 Nibble,每个 Nibble 有3组差分对,这样1个 Bank 总共有27组差分对可以使用。其中1对用于 Strobe 输入,那么在使用差分电平输入的情况下,Number of Data Channels 最大只能设置为26。而使用单端输入时,可以最大设置为53。也就是说,1个 XPIO Bank 最多可以接收1路Strobe+26路 data(差分模式)或1路 Strobe+53 路 data(单端模式)。这里把 Number of Data Channels 设置为10。

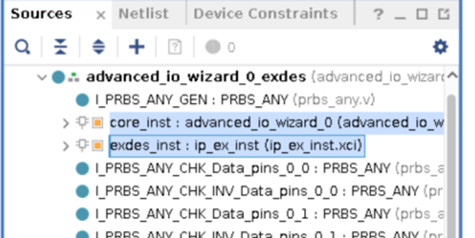

2.点击 OK 产生 IP,右击 IP 选择 Open example design。

3.Example design 生成完毕后,可以看到内部包含了两个 Advanced IO 的 IP,名字分别为 core_inst 和 exdes_inst,分别对应 RX 和 TX 两组接口。

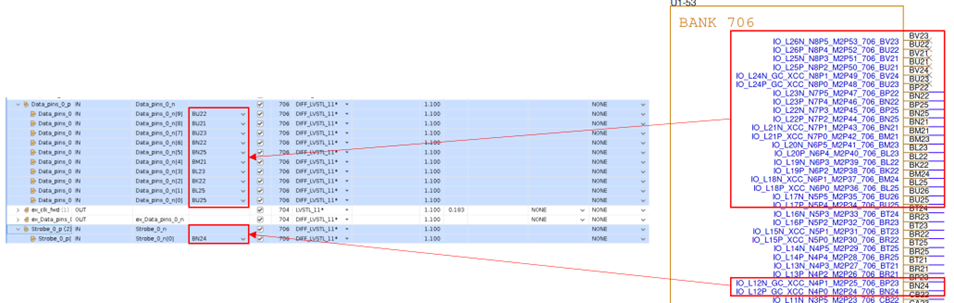

4.管脚约束:

这里还是把1路 Strobe 和10路 Data 都约束在 VP1802 的 Bank706,Strobe 从 Nibble4 的 XCC 管脚输入,10路 Data 被约束到 Nibble5-8,参考下图:

此外,TX 相关的端口也需要作相应的约束,TX 的管脚约束取决于外部信号的连接。所有输入到 MMCM 的时钟需要被约束到 GC 管脚,其余的输入输出管脚没有特别的要求,可根据实际情况连接。

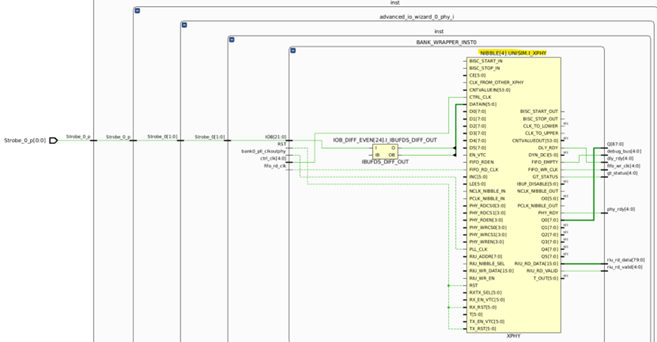

5.约束完成后,点击 Generate Device Image,完成后 Open implemented Design,下面我们验证一下 XPHY 的时钟资源。

Strobe 管脚被约束到了 BN24,这个管脚属于 Bank706 的 Nibble4。

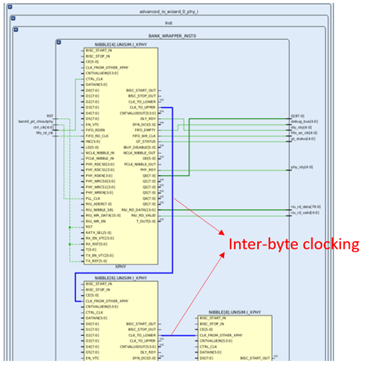

10路 Data 信号分别被约束到了 Nibble5-Nibble8,根据 XPHY 内部的时钟结构,Nibbe4 会通过 CLK_TO_UPPER 管脚经过Inter-byte clocking(下图蓝色线)输出时钟给 Nibble6 的 CLK_FROM_OTHER_XPHY 管脚和 Nibble8 的 CLK_FROM_OTHER_XPHY 管脚,如下图所示:

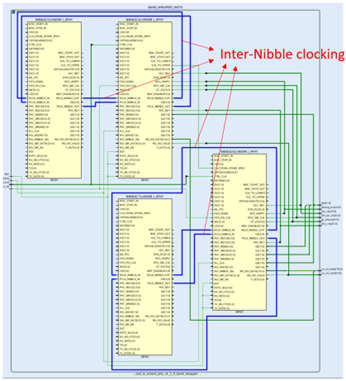

Nibble4 和 Nibble6 再通过 P/NCLK_NIBBLE_OUT 管脚经过 Inter-nibble clocking 分别输出时钟给 Nibble5 的 P/NCLK_NIBBLE_IN 和 Nibble7 的 P/NCLK_NIBBLE_IN,下图蓝色的走线都是 Inter-nibble clocking。

-

amd

+关注

关注

25文章

5647浏览量

139021 -

soc

+关注

关注

38文章

4514浏览量

227615 -

高速接口

+关注

关注

1文章

67浏览量

15214 -

Versal

+关注

关注

1文章

172浏览量

8385

原文标题:开发者分享|AMD Versal™ SelectIO 基于 XPHY 构建源同步接口

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何利用FPGA实现高速连续数据采集系统设计?

基于FPGA的高速数据接口的实现

利用Allegro实现嵌入式系统高速电路设计

利用FPGA 实现与TS201 的LinkPort 高速数据

基于FPGA的高速串行传输接口研究与实现

IR-UWB通信系统高速USB接口的设计与实现

视频采集接口的设计与实现

基于USB协议的DSP高速上位机接口实现

$monitor和$strobe有何差异?

哪些探头与带有 TekVPI 探头接口的示波器兼容?

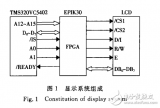

如何利用XPIO构建并实现带有Strobe的高速接口设计

如何利用XPIO构建并实现带有Strobe的高速接口设计

评论