MRAM,即磁阻式随机访问存储器的简称,兼备SRAM的高速读写性能与闪存存储器的非易失性。STT-MRAM是通过自旋电流实现信息写入的一种新型MARM,属于MRAM的二代产品,解决了MRAM写入信息存在的问题。

STT-MRAM存储单元的核心仍然是一个MTJ(磁性隧道结),由两层不同厚度的铁磁层及一层几个纳米厚的非磁性隔离层组成,它是通过自旋电流实现信息写入的。目前,STT-MRAM已经从几家代工厂(GlobalFoundries、英特尔、三星、台积电和联电)中脱颖而出,成为一种非常有吸引力的IP选择。

STT-MRAM具有以下几个出色的特性:

STT-MRAM的开发步骤包括以下几项:

第一步是材料的堆栈工程——例如,晶体结构、原子组成、厚度和每个层边界的界面特性。需要通过详细的“自旋极化”计算确定以下材料特性:

第二步是扩展电子级、“基态、零K”材料模拟。

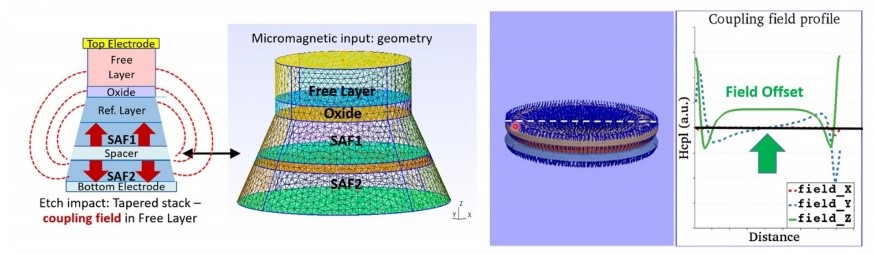

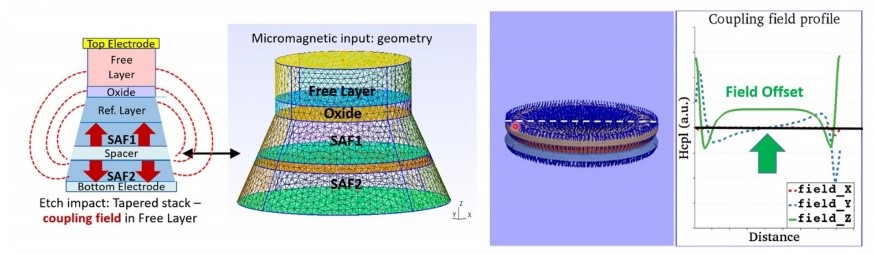

第三步是将 MTJ 物理维度引入到工艺开发中。下图说明了磁性“耦合场”在制造后如何存在于锥形、非完全圆柱形 MTJ 中。

最后一步是将之前对材料、温度相关性和 MTJ 尺寸的分析抽象为合适的“紧凑型器件模型”, MRAM阵列设计人员可以用阵列解码的 SPICE 模型结合位单元存取晶体管、写入驱动器和读取传感设备。

与当前的嵌入式闪存相比,STT-MRAM 在以下几个方面都具有优势:

所有这些特性优势都是在严格的环境条件下应用,例如-40℃~125℃——对应于带有eMRAM IP的工业应用SoC。

制造方式实际上也是STT-MRAM优于闪存的点。以台积电32Mb嵌入式STT-MRAM为例,闪存需要12个或更多额外的掩模,只能在硅基板上实现,并且以页面模式写入。由于MTJ器件能够通过三个左右额外的掩膜嵌入芯片的线路后端(BEOL)互连层,因此STT-MRAM在后段(BEOL)金属层中实现仅需要2-5个额外的掩模,并且可以以字节模式写入。

将STT-MRAM与最新的通用存储候选进行比较,STT-MRAM的读写时间分别为2和20 ns,而相变RAM(PRAM)的读取时间为20~50ns,写入的时间为30ns。此外,STT-MRAM的耐久性也是要优于PRAM的。

当然STT-MRAM也有自身的一些问题。在基于STT-MRAM的许多应用中,磁场干扰是一个潜在的问题。因此 STT-MRAM 阵列的磁抗扰度 (MI) 是一个新的可靠性参数。在最近的 2021 年 VLSI 研讨会上,GLOBALFOUNDRIES 的 MRAM 负责人 Vinayak Bharat Naik 解读了采用 22FDX-SOI 工艺技术制造的 MRAM 阵列的磁抗扰度实验分析结果。值得注意的是,该技术还具有非常吸引人的 RF 特性。因此,可能存在带有电感元件的片上 RF IP,即便这些电感元件会发出显著的场强。下面看看STT-MRAM对于外部场强和片上场强的反应。

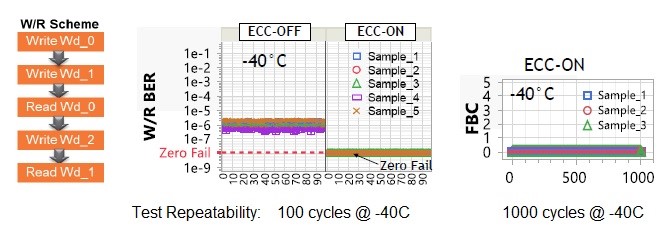

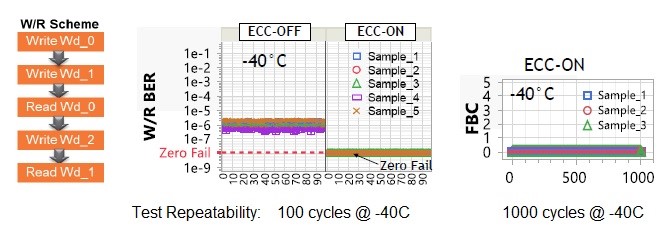

外部场强源自 SoC 封装之外。Vinayak 展示了应用于 STT-MRAM 测试站点的实验设置和 MI 分析结果。下图显示了(ECC 校正的)存储器读写 BER 为零,活动 MI 大于 250 Oe。

另外,Vinayak 还强调,MTJ 层内磁化畴的各向异性表明外部磁场和 STT-MRAM 测试点表面之间的入射角可能会影响抗干扰性。

SoC 芯片内的抗磁性能有两个方面:

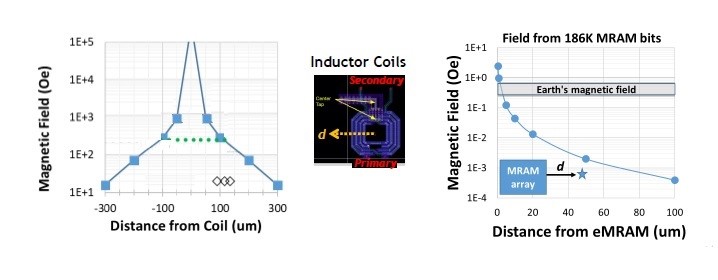

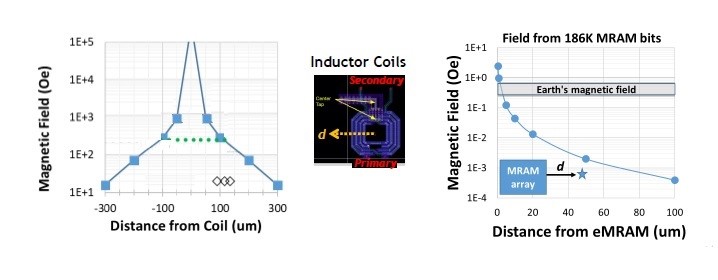

Vinayak 分享了分析数据,显示感应线圈的磁场强度与分离距离的关系,如下所示。右上方的图表显示了源自嵌入式 STT-MRAM 阵列的磁场。在示例中,MRAM阵列场非常小,因此对LC谐振回路振荡频率的影响可以忽略不计。

嵌入式MRAM 确实引入了一个新的可靠性问题——阵列对来自 SoC 封装外部或芯片上电感电路的磁场的“抗扰度”。在制造环节,为了解决磁干扰性问题,制造商选择在封装上沉积0.3mm厚的磁屏蔽层。实验表明在移动设备的商用无线充电器的磁场强度为3500Oe的情况下,暴露100小时的误码率可以从> 1E6 ppm降低到1ppm。另外,在650 Oe的磁场下,在125°C下的数据保存时间超过10年。

目前MRAM软件技术正在世界各地的实验室中开发,但是随着STT-MRAM产品成本的降低,无论是嵌入式产品还是独立产品,MRAM软件技术都可能成为MRAM取代最快的静态随机存取存储器应用的手段,提供更高的非易失性存储器密度。

谈到应用,STT-MRAM可以在许多嵌入式应用中替代NOR闪存和SRAM。非易失性存储使用NOR闪存存储代码,并将数据传输到SRAM充当缓冲区或高速缓存。例如低端手机同时使用NOR和SRAM,可以很容易地用单个STT-MRAM芯片替换它们。

同时,STT-MRAM具有重要的军事应用,在抗恶劣环境高性能计算机、军用卫星、导弹、火箭、航天飞行器控制和数据存储系统中都需要具有超高密度、超大容量、超低能耗、随机存储、非易失性、结构简单、抗辐照能力强等优点的存储器系统,这些特性STT-MRAM都具备。

本文由电子发烧友编辑整理自公开资料和semiwiki技术文章,转载请注明!

STT-MRAM存储单元的核心仍然是一个MTJ(磁性隧道结),由两层不同厚度的铁磁层及一层几个纳米厚的非磁性隔离层组成,它是通过自旋电流实现信息写入的。目前,STT-MRAM已经从几家代工厂(GlobalFoundries、英特尔、三星、台积电和联电)中脱颖而出,成为一种非常有吸引力的IP选择。

STT-MRAM具有以下几个出色的特性:

- 储存时间长

- 高密度

- 随机访问

- 接近零泄漏功率

- 低写误码率

STT-MRAM的开发步骤包括以下几项:

第一步是材料的堆栈工程——例如,晶体结构、原子组成、厚度和每个层边界的界面特性。需要通过详细的“自旋极化”计算确定以下材料特性:

- 磁各向异性 (K)

- 磁饱和 (Ms)

- 隧道磁阻性(TMR)

第二步是扩展电子级、“基态、零K”材料模拟。

第三步是将 MTJ 物理维度引入到工艺开发中。下图说明了磁性“耦合场”在制造后如何存在于锥形、非完全圆柱形 MTJ 中。

图源:semiwiki

最后一步是将之前对材料、温度相关性和 MTJ 尺寸的分析抽象为合适的“紧凑型器件模型”, MRAM阵列设计人员可以用阵列解码的 SPICE 模型结合位单元存取晶体管、写入驱动器和读取传感设备。

与当前的嵌入式闪存相比,STT-MRAM 在以下几个方面都具有优势:

- 耐久性(读/写周期数)

- 数据保留(非易失性阵列存储)

- 读/写循环性能

- 成本

所有这些特性优势都是在严格的环境条件下应用,例如-40℃~125℃——对应于带有eMRAM IP的工业应用SoC。

制造方式实际上也是STT-MRAM优于闪存的点。以台积电32Mb嵌入式STT-MRAM为例,闪存需要12个或更多额外的掩模,只能在硅基板上实现,并且以页面模式写入。由于MTJ器件能够通过三个左右额外的掩膜嵌入芯片的线路后端(BEOL)互连层,因此STT-MRAM在后段(BEOL)金属层中实现仅需要2-5个额外的掩模,并且可以以字节模式写入。

将STT-MRAM与最新的通用存储候选进行比较,STT-MRAM的读写时间分别为2和20 ns,而相变RAM(PRAM)的读取时间为20~50ns,写入的时间为30ns。此外,STT-MRAM的耐久性也是要优于PRAM的。

当然STT-MRAM也有自身的一些问题。在基于STT-MRAM的许多应用中,磁场干扰是一个潜在的问题。因此 STT-MRAM 阵列的磁抗扰度 (MI) 是一个新的可靠性参数。在最近的 2021 年 VLSI 研讨会上,GLOBALFOUNDRIES 的 MRAM 负责人 Vinayak Bharat Naik 解读了采用 22FDX-SOI 工艺技术制造的 MRAM 阵列的磁抗扰度实验分析结果。值得注意的是,该技术还具有非常吸引人的 RF 特性。因此,可能存在带有电感元件的片上 RF IP,即便这些电感元件会发出显著的场强。下面看看STT-MRAM对于外部场强和片上场强的反应。

外部场强源自 SoC 封装之外。Vinayak 展示了应用于 STT-MRAM 测试站点的实验设置和 MI 分析结果。下图显示了(ECC 校正的)存储器读写 BER 为零,活动 MI 大于 250 Oe。

图源:semiwiki

另外,Vinayak 还强调,MTJ 层内磁化畴的各向异性表明外部磁场和 STT-MRAM 测试点表面之间的入射角可能会影响抗干扰性。

SoC 芯片内的抗磁性能有两个方面:

- 源自电感线圈的场,例如用于LC谐振电路,导致STT-MRAM错误率。

- 源自MTJ阵列本身的场,影响LC槽功能。

Vinayak 分享了分析数据,显示感应线圈的磁场强度与分离距离的关系,如下所示。右上方的图表显示了源自嵌入式 STT-MRAM 阵列的磁场。在示例中,MRAM阵列场非常小,因此对LC谐振回路振荡频率的影响可以忽略不计。

图源:semiwiki

嵌入式MRAM 确实引入了一个新的可靠性问题——阵列对来自 SoC 封装外部或芯片上电感电路的磁场的“抗扰度”。在制造环节,为了解决磁干扰性问题,制造商选择在封装上沉积0.3mm厚的磁屏蔽层。实验表明在移动设备的商用无线充电器的磁场强度为3500Oe的情况下,暴露100小时的误码率可以从> 1E6 ppm降低到1ppm。另外,在650 Oe的磁场下,在125°C下的数据保存时间超过10年。

目前MRAM软件技术正在世界各地的实验室中开发,但是随着STT-MRAM产品成本的降低,无论是嵌入式产品还是独立产品,MRAM软件技术都可能成为MRAM取代最快的静态随机存取存储器应用的手段,提供更高的非易失性存储器密度。

谈到应用,STT-MRAM可以在许多嵌入式应用中替代NOR闪存和SRAM。非易失性存储使用NOR闪存存储代码,并将数据传输到SRAM充当缓冲区或高速缓存。例如低端手机同时使用NOR和SRAM,可以很容易地用单个STT-MRAM芯片替换它们。

同时,STT-MRAM具有重要的军事应用,在抗恶劣环境高性能计算机、军用卫星、导弹、火箭、航天飞行器控制和数据存储系统中都需要具有超高密度、超大容量、超低能耗、随机存储、非易失性、结构简单、抗辐照能力强等优点的存储器系统,这些特性STT-MRAM都具备。

本文由电子发烧友编辑整理自公开资料和semiwiki技术文章,转载请注明!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

闪存

+关注

关注

16文章

1885浏览量

117028 -

存储

+关注

关注

13文章

4704浏览量

89583 -

MRAM

+关注

关注

1文章

244浏览量

32834

发布评论请先 登录

相关推荐

热点推荐

BlackBerry QNX与众森软件进一步深化战略合作

今日,深圳市众森软件有限公司(以下简称"众森软件")正式宣布与全球领先的实时操作系统与嵌入式软件供应商 QNX(BlackBerry有限公司旗下部门QNX)进一步深化战略合作。此次合作将进一步推动

stt-marm存储芯片的结构原理

在存储技术快速演进的今天,一种名为STT-MRAM(自旋转移矩磁阻随机存取存储器)的新型非易失存储器,正逐步走入产业视野。它不仅继承了

嵌入式与FPGA的区别

器件的基础上进一步发展的产物,是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解.决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA是硬件电路设计,嵌入式是

发表于 11-20 07:12

Everspin串口MRAM芯片常见问题

在嵌入式存储应用中,串口MRAM芯片凭借其非易失性、高速度及高耐用性受到广泛关注。作为磁性随机存储器技术的代表,Everspin磁性随机存储

芯盛智能嵌入式eMMC E210系列斩获2025年度嵌入式存储产品金奖

11月18日, 一年一度中国数据与存储峰会在北京顺利召开,备受关注的2025存储风云榜同期揭晓。作为领先的存储控制器与解决方案提供商,芯盛智能受邀参会,凭借自主研发的

串行接口MRAM存储芯片面向工业物联网和嵌入式系统的应用

、BBSRAM、NVSRAM及NOR存储器件,专为应对工业物联网、嵌入式系统及高性能存储应用的严苛需求而设计。旨在通过其高性能、高可靠性及广泛的适用性,为下一代

MRAM存储器EMD4E001G-1Gb的优势介绍

在当今对数据持久性与系统可靠性要求极高的企业基础设施和数据中心中,Everspin推出的自旋转移扭矩MRAM(STT-MRAM)存储器——EMD4E001G-1Gb,凭借其卓越的性能与独特的技术优势,成为众多高性能

Everspin串口MRAM存储芯片有哪些型号

MRAM是一种利用电子的自旋磁性来存储信息的非易失性存储器。它完美结合了SRAM的高速读写特性与闪存(Flash)的非易失性,能够在断电后永久保存数据,同时具备无限次擦写、无磨损的卓越

VSCode环境下的用PlatformIO IDE进行RISC-V嵌入式开发的方法

简介:本教程以点亮RV-STAR开发板上的板载LED为目标,从工具安装开始一步一步详细介绍了VSCode环境下的用PlatformIO IDE进行RISC-V嵌入式开发的方法

系统环境

发表于 10-20 12:30

Linux嵌入式和单片机嵌入式的区别?

:使用Linux操作系统,可以运行各种复杂的应用程序和驱动程序。

4. 资源需求 :

单片机嵌入式 :对硬件资源的需求较低,通常只需要一个单片机芯片,内存和存储空间较小。

Linux嵌入

发表于 06-20 09:46

嵌入式超声电机微步距控制检测系统设计

摘 要:设计了一种行波超声电机的嵌入式微步距控制检测系统,该系统分为三大部分:嵌入式上位机、电机控制器和检测系统。以 ARM9微控制器作为主控芯片,将Iinux系统和 Qtopia图形

发表于 06-11 14:43

从eMMC到NAND,嵌入式系统存储的软件优化策略

在嵌入式系统开发领域,存储器作为信息交互的核心载体,其技术特性直接影响着系统性能与稳定性。然而,有些人在面对Linux、安卓等复杂操作系统环境时,理解其存储机制尚存局限,为突破这些技术瓶颈,飞凌

嵌入式存储的下一步:STT-MRAM

嵌入式存储的下一步:STT-MRAM

评论