据媒体报道,作为全球一号代工厂,台积电已经开始大规模量产第六代CoWoS晶圆级芯片封装技术,集成度大大提高。

我们知道,如今的高端半导体芯片越来越复杂,传统的封装技术已经无法满足,Intel、台积电、三星等纷纷研发了各种2.5D、3D封装技术,将不同IP模块以不同方式,整合封装在一颗芯片内,从而减低制造难度和成本。

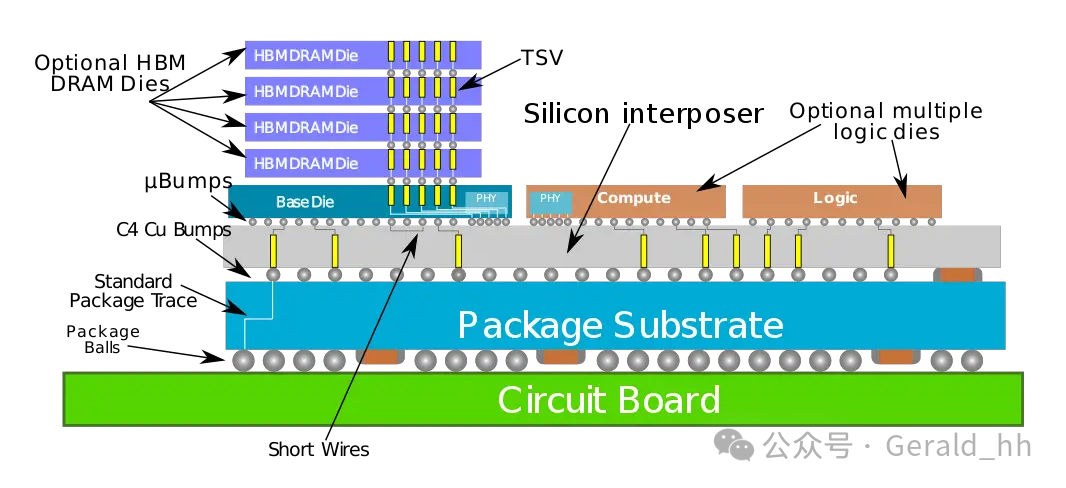

CoWoS的全称为Chip-on-Wafer-on-Substrate,是一种将芯片、基底都封装在一起的技术,并且是在晶圆层级上进行,目前只有台积电掌握,技术细节属于商业机密。

它属于2.5D封装技术,常用于HBM高带宽内存的整合封装,比如AMD Radeon VII游戏卡、NVIDIA V100计算卡都属于此类。

CoWoS封装结构简图

Radeon VII集成封装了四颗HBM

台积电当然也不会披露第六代CoWoS的细节,只是说可以在单个封装内,集成多达12颗HBM内存。

最新的HBM2E已经可以做到单颗容量16GB,12颗封装在一起那就是海量的192GB!

不知道哦什么样的芯片需要这么大的整合内存……

-

台积电

+关注

关注

44文章

5787浏览量

174708 -

晶圆

+关注

关注

53文章

5344浏览量

131655 -

内存

+关注

关注

9文章

3173浏览量

76099 -

CoWoS

+关注

关注

0文章

163浏览量

11451

发布评论请先 登录

瑞萨电子推出第六代DDR5 RCD,传输速率达9600MT/s

台积电CoWoS平台微通道芯片封装液冷技术的演进路线

【海翔科技】玻璃晶圆 TTV 厚度对 3D 集成封装可靠性的影响评估

化圆为方,台积电整合推出最先进CoPoS半导体封装

性能跃升,安全护航 ---- 澜起科技重磅发布全新第六代津逮® 性能核 CPU

台积电超大版CoWoS封装技术:重塑高性能计算与AI芯片架构

先进封装行业:CoWoS五问五答

台积电CoWoS进驻嘉义科学园区,2028年量产

台积电CoWoS封装A1技术介绍

台积电量产第六代CoWoS晶圆封装:12颗封装CPU可集成192GB内存

台积电量产第六代CoWoS晶圆封装:12颗封装CPU可集成192GB内存

评论