静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期。静态时序分析工具很好地解决了这两个问题。它不需要激励向量,可以报出芯片中所有的时序违例,并且速度很快。

通过静态时序分析,可以检查设计中的关键路径分布;检查电路中的路径延时是否会导致setup违例;检查电路中是否由于时钟偏移过大导致hold违例;检查时钟树的偏移和延时等情况。此外静态时序分析工具还可以与信号完整性工具结合在一起分析串扰问题。常用的静态时序工具是PrimeTime。

下面主要阐述一下静态时序的分析原理:静态时序分析工具读入门级网表、时序约束等信息,然后进行静态时序分析。分析过程可以分为3步:

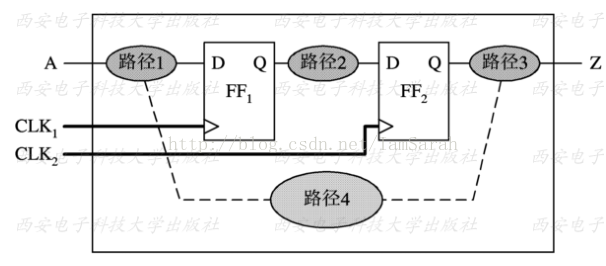

1)将电路分解为时序路径,即将电路转换为时序路径的集合。时序路径是一个点到点的数据通路,数据沿着时序路径进行传递。它的起点是输入端口或者寄存器的时钟,终点是输出端口或者一个寄存器的输入引脚,每个路径最多只能穿过一个寄存器。这样时序路径就可以划分为:输入端口到寄存器、寄存器到寄存器、寄存器到输出端口、输入端口到输出端口。如下图所示,分析其时序路径:

根据时序路径的定义,我们可以找到4条时序路径:从输入端口A到FF1的D端;从FF1的Clk端到FF2的D端;从FF2的clk端到输出端口out1;从输入端口A到输出端口out1。将这些路径在下图标出:

2)计算每个路径上面的延时。在一个路径上,可能包含这几类延时:连线延时(布局布线前后的延时计算方法不一样)、组合逻辑的单位延时(影响因子有输入信号的转换时间,该值也决定输入晶体管的翻转速度、负载、单元本身的固有延时、制程、电压、温度等)、寄存器从clk端到Q端的延时。一个路径上的延时是该路径上所有连线的延时与单位延时的综合。延时一般定义为从输入跳变的50%时刻到输出跳变的50%之间的时间。

3)检查路径时序约束是否满足。路径约束主要指的是建立时间约束和保持时间约束。在寄存器的综合库描述中对寄存器的D端定义了建立时间和保持时间的约束。所谓建立时间约束是指在采样时钟到达之前,数据应该稳定的时间;保持时间是指在时钟到达之后,数据应该保持的时间,这样才能保证寄存器正确地锁存数据。对于纯组合逻辑,时序分析主要检查最大延时约束和最小延时路径。这种情况比较简单。

时钟对于时序电路至关重要。在进行RTL设计时,可以认为时钟是理想的,但在静态时序分析的时候,必须考虑到实际的时钟情形。时钟模型的精度直接影响了静态时序分析的精度。时钟的非理想性包括:

1)时钟偏移(clock skew):同一时钟原到达不同的寄存器的延时不同。

2)时钟抖动(clock jitter):时钟频率和相位会不断变化,脉冲宽度会发生变化。

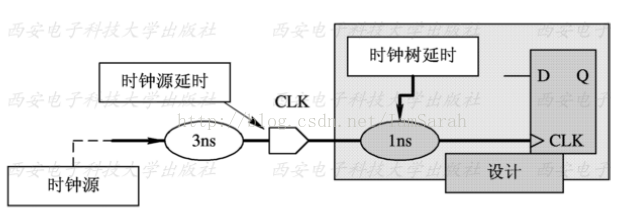

实际情况中,振荡器、互连、电源、负载都会影响到时钟,导致时钟出现偏移、抖动。下面主要讲一下在静态时序分析中,如何对实际的时钟进行建模。考虑下图中的电路,电路中时钟源位于芯片外部。我们将时钟定义在芯片端口上,从时钟源到达端口需要经过3ns左右的延时(板级走线的延时),从时钟端口到寄存器要经过1ns左右的延时(时钟树的延时),对时钟树的延时进行建模可以采取下面的办法:

1)先在端口上定义时钟:

create_clock per8.0 [get_ports clk]

2)设置从时钟源到时钟端口的板级延时:

set_clock_latency source 3 clk

3)设置时钟树本身的延时,在布局布线之前可以采取下面的方法: set_clock_latency 1 clk;在布局布线之后,可以得到时钟树延时的确定值,采用如下的命令:set_propagated_clock clk;

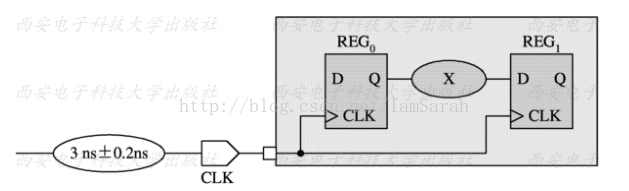

但是如果知道时钟源上的时钟具有0.2ns的不确定性,如下图所示,可以采用下面的方法进行建模:

set_clock_latency 2.8 source early [get_ports clk]

set_clock_latency 3.2 source late [get_ports clk]

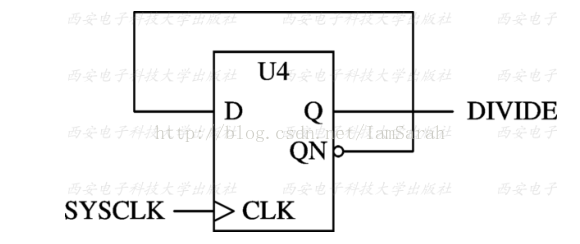

在设计中,往往存在分频时钟,如下图是一个2分频电路。

如果进行静态时序分析时,直接援用create_clock来设置,则PT会将分频后的时钟看做是一个与源时钟毫无关系的时钟。这样在分析源时钟域与分频时钟域之间的信号时,可能会出现问题。正确设置分频时钟方法如下:

create_generated_clock name divide

source [get -pins U4/clk] divide-by 2 [get -pins U4/Q]

下面概括介绍一下对于静态时序分析脚本构造的大致过程:

1)读入设计的相关信息:链接库、网表,如果是PR之后的静态时序分析还需要读入寄生参数信息

2)设置驱动及负载

3)设置时钟

4)设置建立时间和保持时间

5)设置设计规则约束:最大负载、最大转换时间等

6)分析时序:用report_timing 等检查时序,用report_constraint 检查是否有违例。

具体的构造过程可以参考综合脚本,这里不再详述。

编辑:hfy

-

寄存器

+关注

关注

31文章

5620浏览量

130440 -

晶体管

+关注

关注

78文章

10443浏览量

148676 -

数据通路

+关注

关注

0文章

6浏览量

7613 -

静态时序

+关注

关注

0文章

20浏览量

7076

发布评论请先 登录

海外静态IP和海外动态IP有哪些区别?怎么选择?

RGB时序灯条的工作原理讲解

数字IC/FPGA设计中的时序优化方法

ADP7000系列示波器特色功能:抖动分析,捕捉时序之微

Chroma 80611 电源时序/安规综合分析仪:电器安全与性能的自动化验证专家

什么是CVE?如何通过SAST/静态分析工具Perforce QAC 和 Klocwork应对CVE?

vivado时序分析相关经验

知识分享 | 使用MXAM进行AUTOSAR模型的静态分析:Embedded Coder与TargetLink模型

汽车软件团队必看:基于静态代码分析工具Perforce QAC的ISO 26262合规实践

动态BGP与静态BGP的区别?

Simcenter FLOEFD EDA Bridge模块:使用导入的详细PCB设计和IC热特性来简化热分析

盟通方案|专业的CANopen总线分析软件

静态时序的分析原理及详细过程

静态时序的分析原理及详细过程

评论