本文介绍了集成电路设计中静态时序分析(Static Timing Analysis,STA)的基本原理、概念和作用,并分析了其优势和局限性。

静态时序分析(Static Timing Analysis,STA)是集成电路设计中的一项关键技术,它通过分析电路中的时序关系来验证电路是否满足设计的时序要求。与动态仿真不同,STA不需要模拟电路的实际运行过程,而是通过分析电路中的各个时钟路径、信号传播延迟等信息来评估设计是否符合时序要求。

静态时序分析的目标

STA的主要目的是确保电路在每个时钟周期内能够稳定工作,满足时序要求,避免由于时序违例导致的功能错误。例如,信号从一个触发器传播到下一个触发器的时间不能超过时钟周期的长度,否则可能导致数据丢失或错误。

STA的基本原理

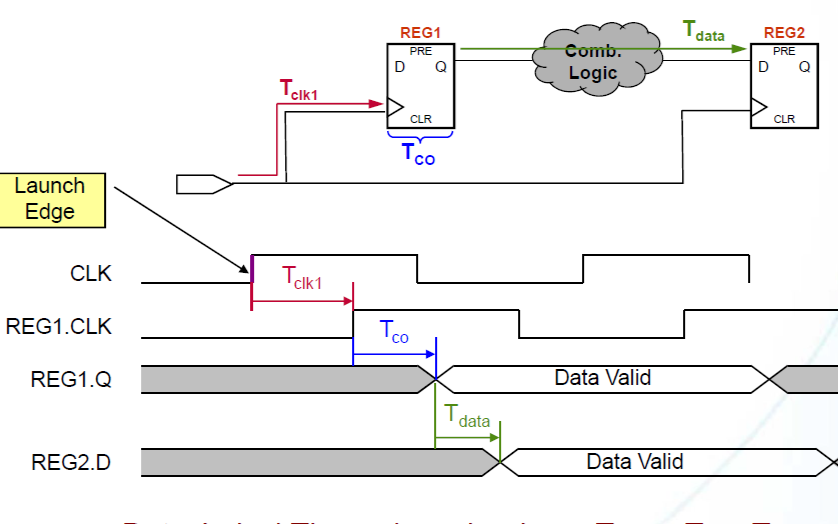

STA通过静态地计算信号在电路中从一个触发器(或寄存器)到下一个触发器的传播时间,并将这些传播时间与时钟周期进行比较,以确保设计中的所有路径在时序上都符合要求。它并不模拟信号的实际值,只分析电路的时序特性,因此非常高效,适用于大规模电路的验证。

STA的主要步骤

路径识别:STA首先识别电路中的时钟路径,即从时钟源到触发器的路径。在这些路径中,时钟信号需要传播和同步。

计算传播延迟:对于每一条时钟路径,STA计算信号从一个触发器到下一个触发器的传播延迟。这包括了电路中各种元器件(如逻辑门、寄存器等)的延迟以及连线的传播延迟。

时钟周期与路径延迟比较:将计算得到的传播延迟与时钟周期进行比较。如果路径延迟小于时钟周期,那么该路径是合格的;如果路径延迟超过时钟周期,就存在时序违例,可能导致信号同步问题。

时序分析:分析过程中,STA会检查两种关键时序:建立时间(Setup Time)和保持时间(Hold Time)。

建立时间:信号必须在时钟沿到达之前稳定到一定时间,以确保触发器正确捕获信号。

保持时间:信号必须在时钟沿后保持稳定,避免出现数据错误。

STA的分析方法

STA主要通过两种方式进行时序检查:

最大延迟(Max Path Delay):检查数据路径的最大传播延迟是否小于时钟周期,确保数据能够及时到达目标触发器。

最小延迟(Min Path Delay):检查数据路径的最小传播延迟,确保信号不会因为过早到达而引起错误。

STA的常见问题

时序违例:如果某条路径的传播延迟超过时钟周期,就会出现时序违例,导致芯片无法正确执行任务。

信号干扰:时序分析过程中,如果信号线长或交叉不当,会增加信号传播延迟,影响时序准确性。

时钟偏移:如果时钟源不稳定或者不同部分的时钟信号不同步,也可能导致时序违例。

STA的优势

高效性:STA通过静态分析计算路径延迟,不需要模拟电路的每个状态,因此在大型电路设计中具有很高的计算效率。

准确性:STA能够提供精确的时序信息,帮助设计人员发现和解决潜在的时序问题。

全面性:STA能够覆盖设计中的所有时钟路径,确保设计的每个部分都满足时序要求。

STA的局限性

无法捕捉动态行为:STA仅分析电路的静态时序特性,无法捕捉到动态行为中的时序问题,例如由于电源波动引起的时序问题。

无法验证所有功能:STA主要用于验证时序,无法检查电路的逻辑正确性和功能完整性,因此通常需要与其他仿真工具联合使用。

STA的应用

芯片验证:STA广泛应用于芯片设计中的时序验证,尤其是在SoC(系统级芯片)设计中。它帮助设计人员确保芯片在实际应用中的时序稳定性和可靠性。

时钟树优化:STA帮助设计人员优化时钟树的布局和时钟信号的传播路径,从而减少时序违例。

后仿验证:STA通常是后仿阶段的一部分,帮助设计团队在芯片设计接近完成时进行时序检查,确保设计能够按预期工作。

总结

静态时序分析(STA)是一项重要的芯片设计验证技术,它通过分析电路的时钟路径和信号传播延迟,确保芯片设计在时序上没有违例。STA能够有效提高设计的可靠性和稳定性,尤其在大型复杂的芯片设计中,能够高效地检测出潜在的时序问题。因此,它是芯片设计中不可或缺的工具之一。

-

集成电路

+关注

关注

5464文章

12688浏览量

375742 -

静态时序分析

+关注

关注

0文章

30浏览量

9797

原文标题:如何理解芯片设计中的STA?

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

同步电路设计中静态时序分析的时序约束和时序路径

集成电路设计中静态时序分析介绍

集成电路设计中静态时序分析介绍

评论