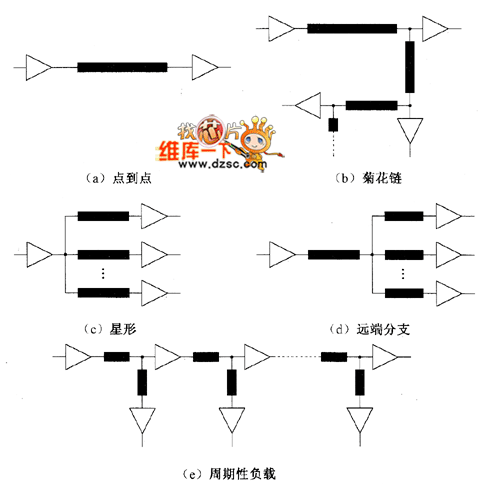

走线的拓扑结构是指一个网络的布线顺序及布线结构。对于多负载的网络,根据实际情况,选择合适的布线拓扑结构并采取正确的“地”端接方式很重要。通常情形下,PCB走线可以选用如图所示的几种拓扑结构。

图 几种典型拓扑结构

(1)点到点

如图2(a)所示的是点到点的拓扑结构,比较简单,只要在驱动端或接收端进行适当的阻抗匹配(通常情况下使用其中的一种就够了,有的电路会出现要求同时使用两种匹配的情况),便可以得到较好的信号完整性。

(2)菊花链

当网络的整个走线长度延迟小于信号的上升或下降时间时,可采用如图(b)所示的菊花链拓扑结构,布线从驱动端开始,依次到达各接收端,在实际设计中,应使菊花链布线中分支长度尽可能短。

菊花链走线的优点是:

· 占用的布线空间较小并可用单一电阻匹配终结;

· 在控制走线的高次谐波干扰方面,效果较好。

菊花链走线的缺点是:

· 布通率低,不容易100%布通;

· 不同的信号接收端,信号的接收是不同步的。

(3)星形

一个信号驱动器驱动多个信号接收器,并要求多个信号接收器同时接收信号时,要使用如图(c)所示的星形拓扑结构,要求每个分支的接收端负载和走线长度尽量保持一致,每条分支上一般都需要终端电阻,终端电阻的阻值应和连线的特征阻抗相匹配。这样即使在边沿速率非常快的情况下仍可以得到很好的性能。

星形拓扑结构可以有效地避免时钟信号的不同步问题,但在密度很高的PCB上手工完成布线十分困难,可采用自动布线器完成星形布线。

(4)远端分支

远端分支如图(d)所示,它跟星形类似,只不过分支是靠近接收端。在这种拓扑结构中,也要限制远端分支的长度,使分支上的传输延时小于信号的上升或下降时间。

(5)周期性负载

周期性负载的拓扑结构如图(c)所示,要求每段分支的长度足够小,使分支上的传输延时小于信号的上升或下降时间。这种主干传输线和所有的分支段组合起来的结构可以被看做一段新的传输线,其特征阻抗要比原来主干传输线的特征阻抗小,传输速率也比原来的低,因此在进行阻抗匹配时要注意。

在实际的PCB设计过程中,对于关键信号,应通过信号完整性分析来决定采用哪一种拓扑结构。

来源:维库电子市场网

-

pcb

+关注

关注

4417文章

23965浏览量

426177 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44715

发布评论请先 登录

高速数字PCB为什么不能全自动布线

调试ddrinit的时候,ddrinit在trap时出现输出乱序的情况,这是怎么回事呢?

PCB Gerber文件如何导出

真不敢信,PCB板上就挪动了一个电阻,DDR3竟神奇变好了

深入探讨PCB布局布线的专业设计要点与常见挑战

PCB布局布线的相关基本原理和设计技巧

micropython 文件同步失败是怎么回事?

Allegro Skill布线功能之删除Dangling介绍

高速PCB设计挑战 Allegro Skill布线功能 自动创建match_group

高速PCB布局/布线的原则

高速PCB布线拓扑是怎么回事

高速PCB布线拓扑是怎么回事

评论