很多人可能觉得PCB信号速率越高,如25Gbps,56G/112G-PAM4信号等调试上发现的问题会越多,其实不然。我们收到最多的调试问题还是DDR3、DDR4等,不是跑不到额度速率,就是识别不到,或者training出现了问题。这种情况下往往调试很久也找不到问题在哪里,最后可能会怀疑是不是PCB设计哪里出了问题,因为原理方案和软件是参考厂家的,“最不容易出错”。

之所以说调试很麻烦,尤其是出了问题后,牵扯到的因素太多,所谓术业有专攻,我们只能从PCB设计和信号或电源完整性的角度去排除,如果涉及到硬件原理或者软件等,我们可能也是一筹莫展。借助今天要讲的这个案例,我们可以来简单说一下在调试过程中一般会怎么处理这种DDRx问题。

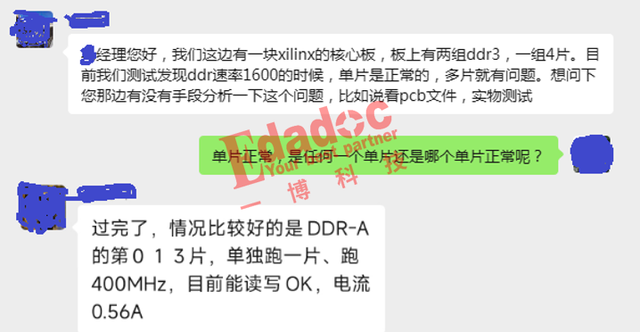

某客户在调试过程中发现他们的DDR3只能在低频下单片正常工作,多片没法同时正常运行,调试了好久也没有找到问题在哪里,最后来求助我们,希望我们查一下PCB设计,或者看是否能实物测试一下信号,下面是客户反馈的问题描述。

然后对应的测试部分结果如下,可以看到在时钟频率400MHz(对应数据率800Mbps)下测试了两块板,1号板只有A通道的第0片(挨着主芯片的第1片)颗粒通过,其余颗粒均报错不通过。2号板只有A通道的第0,1 , 3片颗粒通过,其余均报错不通过。如下图片所示。

在时钟频率800MHz(对应数据率1600Mbps)下测试所有颗粒都报错不通过,如下图所示。

按照我们之前一贯的说法,如果DDRx不能跑到额定速率,通过降频能改善的话,则说明一般是时序裕量问题,这种情况可能和PCB设计或者驱动及ODT的配置有关系,我们通过查板或者仿真有很大概率能找到并解决这类问题。

眼前的这个DDRx问题现象在高频的时候都报错不通过,而降频后有部分不报错可以通过,说明降频后还是有改善的,于是我们让客户把PCB设计文件给我们查一下,这个也是我们解BUG的基本套路。

拿到PCB板子,确实也发现了不少问题,挑出下面几个比较明显一点的。

1、PCB做等长的时候没有把芯片的Pin delay一起加上考虑,会影响时序;

2、电路板地址线的等长规则只设置了第一片颗粒到主控芯片的主干段,颗粒到颗粒间的分支没有设置相关规则,会影响到时序;

3、时钟按照Fly_by拓扑走线,端接电阻放在了靠近第1片颗粒处而不是最后一片颗粒处,这是一个严重的问题,如下图所示。

看到这里,眼尖的小伙伴们可能就知道问题出在了哪里,于是我们便让客户快速做一个实验,把上图红色圈出的电阻想办法焊接到最后一片颗粒对应的管脚P N上,同时担心客户不太明白,于是好人做到底,顺便把PCB对应的电阻位号和要挪到的位置也按照下图所示标示了出来。

因为B通道也是同样的问题,而且调试情况更糟糕,于是我们顺便也让客户按照同样的方法挪动了B通道的时钟网络电阻位置。

第二天好消息传来,客户按照我们的建议挪了电阻的位置,问题解决了。这个PCB板案例也说明了有时我们查板会发现很多细节不符合PCB设计要求,最重要的是要学会分析哪个点才是关键(致命)问题所在;同时我们发现在速率不是很高的情况下,就算不考虑芯片的pin delay,系统也不至于没法工作,这些都是引起时序裕量不足的一些因素,而我们要做的就是尽量从各方面去抠出更多的裕量。

关于一博:

一博科技成立于2003年3月,深圳创业板上市公司,股票代码: 301366,专注于高速PCB设计、SI/PI仿真分析等技术服务,并为研发样机及批量生产提供高品质、短交期的PCB制板与PCBA生产服务。致力于打造一流的硬件创新平台,加快电子产品的硬件创新进程,提升产品质量。

一博珠海板厂位于珠海经济开发区,坐拥PCB产业优质人才资源及完善的产业配套。一期全面投产,专注于高端快件,提供高品质的高多层、高速、高精密、HDI等PCB生产制造。二期提供中大批量高速、高多层PCB生产。聚焦国内高端快件细分市场,致力于推动国内PCB行业的技术进步,尤其是高速、高多层、高复杂PCB产品的快速交付,12-20层制板交期快至8天内交付,对应PCB广泛应用于ATE、AI算力、服务器、工控、通信、汽车、医疗设备等领域。

审核编辑 黄宇

-

PCB板

+关注

关注

27文章

1503浏览量

55540 -

DDR3

+关注

关注

2文章

290浏览量

44277

发布评论请先 登录

真不敢信,PCB板上就挪动了一个电阻,DDR3竟神奇变好了

真不敢信,PCB板上就挪动了一个电阻,DDR3竟神奇变好了

评论