说起来,每次看到新来的工程师对着PCB设计软件猛点"自动布线"按钮,我都忍不住想上去拦一把。不是我看不起自动布线这功能,坦白讲对于低速、低复杂度的板子,它确实香——省时省力,还能保证基本连通性。但问题是,只要你做的板子稍微"快"一点、复杂一点,自动布线分分钟给你埋雷。

按我的经验,很多硬件工程师入门的时候都踩过这个坑:板子画完,原理图没问题,器件也选对了,布局布线全靠软件自动搞定。结果一打样回来,调不通、误码率超标、EMC过不了……一查原因,十有八九就是布线埋下的隐患。今天就跟大家唠唠,高速数字PCB为什么不能全自动布线,人工布线的底线到底在哪里。

先搞清楚:高速信号到底有什么不一样?

很多刚入行的朋友可能觉得,PCB布线不就是把线连上嘛,能有什么玄机?说这话的人,十有八九没做过10Gbps以上的项目。

低速信号在板子上跑,说白了就是"数字0和1"慢慢悠悠地溜过去,沿途有点干扰、有点反射,都不是什么大事,接收端有足够的裕量来消化这些问题。但高速信号完全不是一个逻辑——它们是以电磁波的形式在传输线上跑的,频率一高,信号完整性问题就全冒出来了。

举个直白的例子,5GHz的信号,波长大概是3厘米。当你的走线长度接近这个量级的时候,导线就不再是简单的"导线"了,它变成了天线、变成了传输线。阻抗必须严格匹配,否则信号一进门就被弹回去,过冲、欠冲、振铃,一连串问题全来了。

行业默认的标准:单端信号阻抗50欧姆,差分对100欧姆。偏差个10%,高速场景下可能就出问题了。这精度要求,自动布线那个"差不多就行"的逻辑,根本兜不住。

自动布线到底哪里不行?

我跟你说,自动布线器本质就是个"走迷宫高手",它的核心逻辑是:找到一条路径把A点到B点连起来,顺便满足你设定的间距、线宽规则。它不关心信号是跑5Mbps还是5Gbps,不关心你这条线是时钟还是普通IO,更不关心回流路径是不是绕了十万八千里。

放到高速场景下,这就会引发一系列连锁反应。

第一,阻抗控制直接抓瞎

高速信号要求阻抗连续、精确匹配。决定阻抗的因素有四个:线宽、铜厚、介质厚度、介电常数。自动布线只会傻傻地按你预设的线宽走,但线走到拐角、走到过孔、走到换层的地方,阻抗早就不知道飘到哪里去了。

我见过最离谱的案例,一块PCIE Gen3的板子,自动布线出来的走线,阻抗误差超过20%。你说这板子能用吗?

第二,差分对等长是个玄学

USB、HDMI、PCIE、以太网,这些高速接口全靠差分对传输数据。差分对的原理很简单:两根线跑相反的信号,接收端一减,干扰全没了。但代价是,这两根线必须等长、等距、对称,长度差要控制在5mil以内,间距必须恒定。

自动布线能做好这个?做梦去吧。它要么给你绕成一长一短,要么两根线各走各的,间距忽大忽小。这直接导致的问题就是时序错位、共模噪声飙升、眼图闭合——每个都是高速设计的死穴。

第三,串扰控制想都别想

高速PCB走线密集,相邻走线之间会通过电磁场耦合产生串扰。学过电磁学的都知道,串扰强度和间距的平方成反比,和平行长度成正比。3W原则(间距≥3倍线宽)不是说着玩的。

自动布线追求的是布通率,它才不管你两条高速线是不是紧贴着走了十几毫米。这种板子回来,一测试,近端串扰、远端串扰,双双超标,调都不知道从哪里下手。

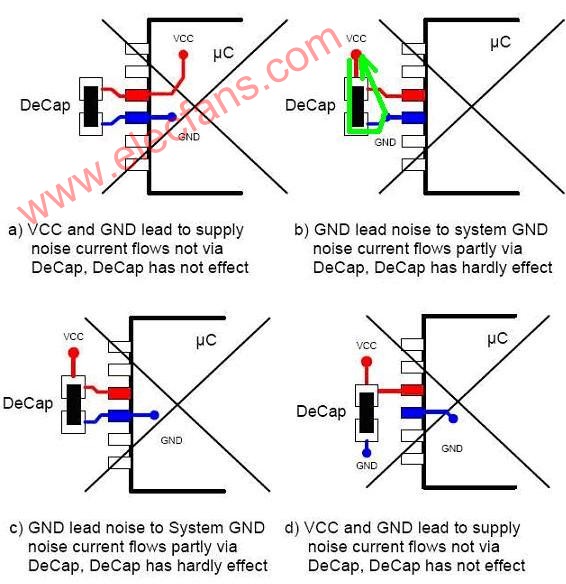

第四,回流路径说扔就扔

这是最容易忽略但最致命的问题。高速信号不是单程车票,它必须要有回流,而且回流路径越短、环路面积越小越好。理想情况是走线正下方有个完整的地平面,回流就贴着信号走,环路面积接近于零。

自动布线最常干的事:跨分割走线、绕开过孔、穿个过孔换层——每一步都在折腾回流路径。结果就是环路面积翻着倍地涨,EMC辐射直接爆表。

人工布线的底线在哪里?

说了这么多自动布线的问题,那人工布线是不是就高枕无忧了?也不尽然。关键是要知道哪些地方必须手动来,哪些地方可以交给软件。

按我的经验,这几类信号必须人工手动布线:

第一,时钟和PLL相关线路。晶振、时钟发生器、PLL这些,是整个板子的"心跳"。时钟线必须最短、最直,回流路径必须完整,而且要远离干扰源。自动布线分分钟给你绕个几圈,信不信?

第二,所有差分对。USB、HDMI、PCIE、SATA、MIPI、以太网,但凡带差分的信号,都得手动盯着。线宽、间距、等长,一个参数都不能马虎。

第三,DDR内存总线。这玩意儿等长要求极其变态,数据组、地址组、控制组,每一组都有严格的长度匹配要求,误差通常要控制在±5mil以内。自动布线?洗洗睡吧。

第四,电源和功率回路。虽然不是"高速",但大电流路径同样需要精心规划——铜皮要宽、过孔要多、环路面积要小,否则压降过大、发热严重。

第五,敏感模拟信号。ADC前端、传感器信号、射频走线,这些模拟信号的布线直接影响噪声底,自动布线出来的走线分分钟把信噪比拉垮。

半自动才是正解

其实吧,真正高效的做法是半自动布线:人工先把关键信号、高精度要求的信号布好,锁定;然后让自动布线去跑剩下的普通信号。

具体流程是这样婶儿的:先根据原理图和 datasheet 确定叠层结构、阻抗目标;然后手动布线所有关键信号(时钟、差分对、DDR等);接着设置好规则约束,让自动布线去处理电源、地、低速信号这些"不太讲究"的线路;最后再整体检查一遍,手动微调。

这样做的好处是既保证了高速信号的质量,又兼顾了设计效率。关键是工程师要有判断力,知道哪些该手动、哪些可以交给软件。

几个常见误区

最后说几个新人特别容易踩的坑,大家引以为戒。

误区一:规则设好了就万事大吉。错,规则只是告诉软件"你应该怎么走",不代表软件一定能走出来、走出来的一定对。规则设完必须检查结果。

误区二:仿真过了就不用管。仿真软件再强,也只是数学模型,和真实板子之间总有差距。仿真通过只能说明"大概率没问题",不代表"一定没问题"。

误区三:板子回来调一调就能搞定。实话告诉你,高速PCB的布线问题,在板子回来之后能调的空间极其有限。很多问题,比如阻抗不匹配、串扰超标、EMC辐射,在设计阶段不解决,回来之后就只能改板重来。

总结一下

说了这么多,其实核心就一句话:低速看连通,高速看阻抗。

自动布线对于简单板子是好工具,但对于高速数字PCB,它只能作为辅助,真正的设计质量还得靠工程师的经验和判断。

把连通做好是合格工程师,把高速信号做好才是资深工程师。希望今天的分享对你有帮助,下次布线的时候,别再无脑点自动了,先问问自己:这条线,是高速的吗?

-

PCB设计

+关注

关注

396文章

4938浏览量

95740 -

布线

+关注

关注

9文章

834浏览量

86251 -

高速信号

+关注

关注

1文章

277浏览量

18524

原文标题:高速数字PCB为什么不能全自动布线?这就告诉你底线在哪

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高速数字PCB为什么不能全自动布线

高速数字PCB为什么不能全自动布线

评论