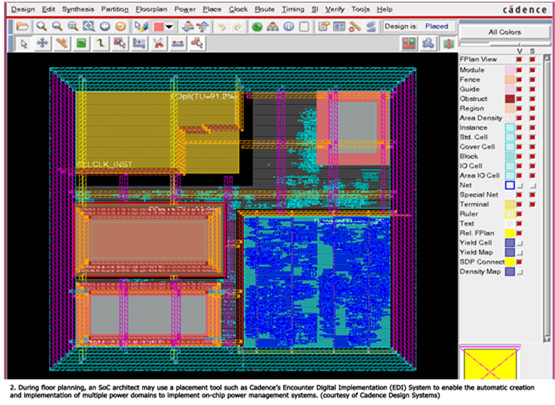

Cadence设计系统公司,日前宣布推出28纳米的可靠数字端到端流程,推动千兆门/千兆赫系统级芯片(SoC)设计,在性能与上市时间方面都有着明显的优势。在Cadence的硅实现方法的驱动下,在统一化设计、实现与验证流程中,通过技术集成和对核心架构与算法大幅改进,基于Encounter的全新流程提供了更快、更具决定性的途径实现千兆门/千兆赫硅片。通过与Cadence的模拟/混合信号与硅/封装协同设计领域的无缝综合,新的数字28纳米流程让设计师能够全局考虑整个芯片流程,在高性能、低功耗、混合信号甚至面向移动与多媒体SoC的3D-IC设计关键成功因素方面实现重大突破。

即将上市的这种新流程支持Cadence的硅实现方法,专注于独一无二且普遍深入的设计意图、提取与从RTL到GDSII,然后到封装。硅实现是EDA360构想的一个关键组成部分。

“28纳米工艺技术对设计人员来说既是重大的机遇也是严峻的挑战,在功率、性能以及尺寸方面都具有优势,但是也面临工艺变化和新制造效应的挑战,”创意电子公司设计与开发部门主管AlbertLi说,“我们采用了Cadence的数字端对端流程用于我们首个28纳米设计,因为Cadence公司的提供的千兆门级/千兆赫设计能力和先进工艺节点技术正是我们公司为客户提供服务所需要的。使用Cadence的数字端对端流程,我们公司不仅能够处理28纳米设计的复杂布局布线、多变性以及制造要求,还能够在合理的设计周期时间内应对100+百万门级的设计。最终可以提高我们公司的生产力并能帮助我们更好地预测服务的交付进度。”

这种新流程使高级工艺节点不用再为复杂性而妥协,可以优化28纳米的复杂设计,为高级SoC开发提供一个途径,使其能实现在更小工艺尺寸下的成本优势。流程功能的关键是统一基于意图、提取和聚合的数字设计、实现与验证。

提升统一意图的功能包括:

•完整、可靠的28纳米设计规则意图(电学、物理、DFM)和早期的提前权衡分析,通过智能导孔与引脚密度优化,提供运行时间方面的两倍提升。

•早期时钟拓扑意图捕捉和规划使用物理信息智能优化时钟门控,并在设计的合成过程中平衡时钟树。提高提取的功能包括:

•突破性的数据提取技术能够让整个逻辑模块被简单而精确地建模,并在逻辑与物理方面进行优化,提高千兆门级的可升级性与设计效率。

•支持分层低功耗和基于OpenAccess混合信号的快速/细节提取,以保证IP和高级SoC快速集成。更快的设计收敛通过如下功能实现:

•注重物理考量的pre-maskECO使困难的功能性ECO操作自动化,使设计收敛速度大大加快,并显著地缩短了设计周期。

•突破性的设计内高级分析架构,提供超快、一步式信号完整性与设计流程中的时序分析收敛,实现高效设计收敛。

•精确的全混合信号静态时序分析与时序驱动式优化,减少模拟与数字设计团队之间的反复工作。

•全新、带有统一意图、提取和收敛、全面集成的3D-IC/功能,跨越数字、全定制与封装设计,如今可实现优化的性能、尺寸、成本与功率。

“28纳米设计的复杂性以及对复杂千兆门/千兆赫设计的支持需要,都要求一种综合的端到端流程,”SiliconRealization产品市场部高级经理DavidDesharnais说。“我们独一无二的硅实现方法让我们的客户推进其SoC设计到新的层次,从而为新一代的多媒体、通信与计算应用提供功能最强的芯片。今天我们公布的28纳米全面数字硅实现流程是朝着EDA360构想的实现又迈出了一大步。”

Cadence推出28纳米的可靠数字端到端流程

相关推荐

高通将推出28纳米工艺Krait系芯片

高通执行副总裁史蒂芬·莫林科夫(Steven Mollenkopf)终于证实,公司旗下首款采用28纳米制造工艺的产品将于今年年底到来!其实早前业内就已经有消息放出,暗示高通将于今年晚些时候才发

2011-07-23 09:14:13 3258

3258

3258

3258Cadence首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

Cadence宣布业内首个DDR4 Design IP解决方案在28纳米级芯片上得到验证

2012-09-10 09:53:24 1403

1403

1403

1403以28纳米为基础,赛灵思(Xilinx)20纳米继续超越

赛灵思的20纳米产品以备受市场肯定的28纳米制程突破性技术为基础,提供超越一个技术世代的系统效能、功耗和可编程系统整合度,继续超越下一代!

2012-12-03 09:48:01 876

876

876

876台积电认可Cadence Tempus时序签收工具用于20纳米设计

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电(TSMC)在20纳米制程对全新的Cadence® Tempus™时序签收解决方案提供了认证。该认证

2013-05-24 11:31:17 1345

1345

1345

1345Cadence设计工具通过台积电16nm FinFET制程认证

Cadence系统芯片开发工具已经通过台积电(TSMC) 16纳米 FinFET制程的设计参考手册第0.1版与 SPICE 模型工具认证,客户现在可以享用Cadence益华电脑流程为先进制程所提供的速度、功耗与面积优势。

2013-06-06 09:26:45 1236

1236

1236

1236传华力微挖角联电28纳米研发团队 望破瓶颈

继台湾半导体高层人士高启全、蒋尚义、孙世伟等陆续加入大陆企业之后,近期传出上海华力微电子挖角联电一组高达 50 人的 28 纳米研发团队,希望解决在 28 纳米制程中的瓶颈问题,加速为联发科代工芯片的量产进程。

2017-02-07 10:31:31 729

729

729

729Cadence发布推动SiP IC设计主流化的EDA产品

。” Cadence推出的RFSiP套件为无线通信应用的RFSiPs设计提供了自动化和加速设计流程的最新产品和技术。它同时提供了基于802.11b/g无线局域网设计的成熟的SiP实施方法,能够低风险地实现

2008-06-27 10:24:12

纳米防水防潮技术的作业流程

、东南亚产品,衣鞋等。注意:1.网上很多自己喷上去的,还很好卖,这些附着力很差的,可以说是一次性的,上面有灰尘、水分。鞋子有纳米防水镀膜始需要可靠性测试的。某国际品牌已经在做测试2.街头的那个纳米防水技术,还现场演示。实践是检验真理的唯一标准。忽悠老板姓。

2018-10-09 09:54:28

AD5272数字电位器W端输出电压在5不变化

5V 单电源供电,RESET直接5V拉高,AD5272 寄存器读写正常,游标可变化(WA端电阻可根据配置值变化),但是W端输出电压始终维持在5V不变化。用万用表无法测试W端到地的阻抗值(表上数字闪烁测不出具体值)。注:我们用的是ADI的DEMO板。

2018-08-31 09:35:45

ARM端和DSP端的程序分别各自烧到ARM端和DSP端,两者数据交互在公共的缓存区?

大家好,刚接触到DSP+ARM,请教个问题:ARM端和DSP端的程序应该是分别独立的两个程序文件,也分别独立编译成各自的.out,分别各自烧到ARM端和DSP端,两者数据交互在公共的缓存区?是不是

2020-08-12 13:18:30

GPS轨道记录PC端

GPS轨道记录PC端GPS轨迹记录PC端.rar 2014-8-28 17:42 上传 点击文件名下载附件 65.97 KB, 下载次数: 74

2018-07-19 04:48:55

ad9361射频端收发直连回环那基带数字接收端能收到基带发送的IQ信号吗?

ad9361射频端收发直连回环,基带数字接收端能收到基带发送的IQ信号吗?我基带发送端IQ是正交的1MHz正余弦波,通过ad9361发送到射频发送端,通过SMA直接回环到射频接收端,最后到基带接收端

2018-09-05 11:27:51

stm32 u***和安卓手机端的通讯流程是怎样的

stm32 u***和安卓手机端的通讯流程前段时间公司开发了一个安卓外设,主要是用某宝淘来的demo 在stm32F103的u***功能来和安卓设备的u***来通讯叙述之前先来一个整体的框图吧:需要

2022-02-22 08:24:38

光耦两端的数字地与模拟地如何接?

采样,当然,模拟地和单片机数字地之间是通过0欧姆电阻连接。因为微弱信号只有几mV,也就是说,模拟地稍微遇到一点干扰,就会严重影响到信号采样和输出。如果一起光耦两端地模拟地和数字地之间不连接任何器件,仪器

2023-09-20 06:48:36

基于cadence的问题

本人现在大学3年级,做课程设计,老师居然给了我们一个研究生课题,我真是***了。该题目为基于cadence的双端输入单端输出的运算放大电路现在比较急了,还有几天就要交了,自己的电路图一直有问题,希望大神们帮帮忙,不胜感激

2016-07-05 10:25:40

如何使用CCC数字钥匙R3汽车锚的BLE端?

我们用 kw45b41zevk 板敲响了数字钥匙汽车锚演示代码。我不知道如何使用 CCC 数字钥匙 R3 汽车锚的 BLE 端。请给我一些演示文件。

2023-06-08 07:04:28

如何使用Socket实现UDP客户端?

本教程介绍了如何利用socket 编程来实现一个 UDP 客户端,与服务器进行通信。与开发 TCP 客户端一样,我们先将 socket 编程的流程列出来,然后给出具体的实例。

2021-03-30 07:39:10

展讯将主打TD与WCDMA 将推出28纳米LTE芯片

展讯计划在2012年推出WCDMA智能手机芯片,并将主打TD+WCDMA双模芯片。而在LTE产品规划方面,他表示展讯将可能在不久之后推出基于28纳米技术的TD-LTE芯片。拟推28nm TD-LTE

2011-10-27 11:50:07

点到点和端到端通讯

点到点通信点到点是物理拓扑,是网络层的,如光纤,就必须是点到点连接,DDN专线也是,即两头各一个机器中间不能有机器。端到端通信端到端是网络连接,是传输层的。网络要通信,必须建立连接,不管有多远,4G

2019-01-18 18:06:07

电子行业人士带你入行之纳米制程小白篇

能耗。简单的说,这也符合未来轻薄化的趋势。纳米制程是什么纳米制程是指芯片中的线能缩小到的尺寸,举个例子,长得跟下图一样的传统电晶体,L代表着我们期望缩小的闸极长度,从Drain 端到 Source 端

2016-12-16 18:20:11

电子行业人士带你入行之纳米制程小白篇

能耗。简单的说,这也符合未来轻薄化的趋势。纳米制程是什么纳米制程是指芯片中的线能缩小到的尺寸,举个例子,长得跟下图一样的传统电晶体,L代表着我们期望缩小的闸极长度,从Drain 端到 Source 端

2016-06-29 14:49:15

英特尔将在2014年推出14纳米处理器芯片

的竞争对手仍然很难应用20纳米以下的技术。 考虑到英特尔是第一个大批量生产32纳米芯片的公司,这个消息并不让人感到意外。而且,作为另一个行业第一,英特尔最近宣布它已开始使用22纳米技术批量生产代号为Ivy

2011-12-05 10:49:55

蜂窝/PCS电话优选的端到端设计指南 第二版

蜂窝/PCS电话优选的端到端设计指南 第二版为你的W-CDMA电话设计提供端到端方案 [hide]蜂窝_PCS电话设计指南第二版.rar[/hide]

2009-12-07 10:48:50

语音端到端加密方案

本帖最后由 蓝是昵称 于 2019-11-7 14:21 编辑

提供完整的全数字语音端到端加密方案:包括硬件、软件功能:通过通信终端的耳机接口、蓝牙接口实现全数字语音加密通信,可在现有终端

2019-11-07 14:08:17

阿里展示“云到端”整体方案

阿里展示“云到端”整体方案,今日,Qualcomm 宣布已经完成在 Qualcomm MDM9206 全球多模 LTE IoT 调制解调器上运行阿里云 Link物联网套件。此项进展有助于展示通过在

2021-07-27 06:30:49

Cadence仿真流程

Cadence 仿真流程:第一章 在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方

2008-07-12 08:56:05 0

0

0

0cadence 视频教程 (第28课)

cadence 视频教程 (第28课):adence SPB 15.7 视频教程,手把手教你学习cadence软件使用方法。本套视频教程是于博士信号完整性研究网于争博士主讲。从一个工程师的角度出发讲解软件的操

2009-09-16 19:02:12 0

0

0

0Cadence生物指纹安全解决方案为UPEK整合芯片设计流程

2009年3月4日,Cadence设计系统公司今天宣布生物指纹安全解决方案领先厂商UPEK®, Inc.已经整合其设计流程,并选择Cadence®作为其全芯片数字、模拟与混合信号设计的

2009-03-05 12:14:18 519

519

519

519Cadence推出首个TLM驱动式设计与验证解决方案提升基于

Cadence推出首个TLM驱动式设计与验证解决方案提升基于RTL流程的开发效率

Cadence设计系统公司推出首个TLM驱动式协同设计与验证解决方案和方法学,使SoC设计师们可以尽

2009-08-11 09:12:18 499

499

499

499中芯国际采用Cadence DFM解决方案用于65和45纳米

中芯国际采用Cadence DFM解决方案用于65和45纳米 IP/库开发和全芯片生产

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461

461

461中芯国际(SMIC)和Cadence 共同推出用于65纳米的

中芯国际(SMIC)和Cadence 共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

完全集成的能效型流程令快速、轻松地设计低功耗尖端器件成为可能

2009-10-31 07:48:01 1228

1228

1228

1228中芯国际(SMIC)和Cadence共同推出用于65纳米的低

中芯国际(SMIC)和Cadence共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

全球电子设计创新领先企业Cadence设计系统公司今天宣布推出一款全面的低功耗设计流程,面向

2009-11-04 17:05:17 589

589

589

589微捷码推出28纳米及28纳米以下IP特征表征新标准

微捷码推出28纳米及28纳米以下IP特征表征新标准

微捷码(Magma®)设计自动化有限公司(纳斯达克代码:LAVA)日前宣布推出业界标准SiliconSmart产品线新产品——

2009-12-18 09:51:50 907

907

907

907高通携手TSMC,继续28纳米工艺上合作

高通携手TSMC,继续28纳米工艺上合作

高通公司(Qualcomm Incorporated)与其专业集成电路制造服务伙伴-TSMC前不久日共同宣布,双方正在28纳米工艺技术进行密切合作。此

2010-01-13 08:59:23 910

910

910

910台积电与联电大客户赛灵思合作28纳米产品

台积电与联电大客户赛灵思合作28纳米产品

外电引用分析师资讯指出,联电大客户赛灵思(Xilinx)3月可能宣布与台积电展开28纳米制程合作;台积电28纳米已确定取得富

2010-01-19 15:59:55 1058

1058

1058

1058高通首款基于28纳米工艺的Snapdragon芯片组MSM8

近期,高通公司宣布将推出首款基于28纳米工艺的Snapdragon芯片组MSM8960并宣布此芯片组将于2011财年开始出样。基于28纳米工艺的该芯片组采用新的CPU内核为特征,主要针对高端

2010-11-24 09:19:57 1471

1471

1471

1471微捷码32/28纳米低功耗工艺层次化参考流程

微捷码(Magma®)设计自动化有限公司日前宣布,一款经过验证的支持Common Platform™联盟32/28纳米低功耗工艺技术的层次化RTL-to-GDSII参考流程正式面市。

2011-01-26 09:44:09 894

894

894

894三星使用Cadence统一数字流程实现20nm芯片流片

三星电子有限公司使用Cadence统一数字流程,从RTL到GDSII,成功实现了20纳米测试芯片的流片

2011-07-27 08:47:49 967

967

967

967Giantec采用Cadence技术统一数字流程生产其混合信号芯片

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence® Virtuoso®统一定制/模拟(IC6.1)以及Encounter®统一数字流程生产其混合信号芯片。

2011-09-27 11:06:26 1483

1483

1483

1483Cadence提供新一代Encounter RTL-to-GDSII流程

全球电子设计创新领先企业Cadence设计系统公司日前宣布推出最新版Cadence Encounter RTL-to-GDSII流程.

2012-03-10 09:44:06 763

763

763

763苹果合作伙伴台积电TSMC加速量产28纳米芯片

台积电TSMC已经准备量产28纳米工艺的ARM处理器了。TSMC在2011年第四季度开始从28纳米芯片获得营收,目前28纳米工艺芯片占有公司总营收的额5%。在今年晚些时候,TSMC将加速28纳米芯片的生

2012-04-18 10:22:37 830

830

830

830

台积电28纳米产能季增3倍

晶圆代工龙头台积电力拚28纳米扩产,随着良率拉升到8成以上,及中科12寸厂Fab15新产能大量开出,本季已安装产能(installed capacity)较上季大增3倍,为第4季营运淡季不淡埋下伏笔。

2012-08-20 08:38:03 587

587

587

587TSMC 20纳米的设计架构选择Cadence解决方案

全球电子设计创新领先企业Cadence设计系统公司日前宣布TSMC已选择Cadence解决方案作为其20纳米的设计架构。Cadence解决方案包括Virtuoso定制/模拟以及Encounter RTL-to-Signoff平台。

2012-10-22 16:48:03 909

909

909

909Cadence采用FinFET技术流片14纳米芯片

该14纳米产品体系与芯片是ARM、Cadence与IBM之间在14纳米及以上高级工艺节点上开发系统级芯片(SoC)多年努力的重要里程碑。使用FinFET技术以14纳米标准设计的SoC能够大幅降低功耗。 这

2012-11-16 14:35:55 1270

1270

1270

1270借力Cadence,Avago 28nm网络芯片设计性能提升57%

Cadence设计系统公司日前宣布Avago Technologies在大型28纳米网络芯片设计中使用其EDI系统,大幅度加快设计进度,提高了工程效率。Avago实现1GHz的性能,比之前所用软件设计的芯片提高57%。

2013-02-04 09:17:00 1150

1150

1150

1150

Cadence和GLOBALFOUNDRIES合作改进20及14纳米节点DFM签收

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)近日宣布,GLOBALFOUNDRIES已携手Cadence®,为其20和14纳米制程提供模式分类数据

2013-05-13 10:20:02 770

770

770

770Cadence解决方案助力创意电子20纳米SoC测试芯片成功流片

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,设计服务公司创意电子(GUC)使用Cadence® Encounter®数字实现系统(EDI)和Cadence

2013-07-09 15:53:24 769

769

769

769联华电子28nm节点采用Cadence物理和电学制造性设计签收解决方案

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)今天宣布,历经广泛的基准测试后,半导体制造商联华电子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence® “设计内”和“签收”可制造性设计(DFM)流程对28纳米设计进行物理签收和电学变量优化。

2013-07-18 12:02:09 905

905

905

905华力微电子与Cadence共同宣布交付55纳米平台的参考设计流程

全球电子创新设计Cadence公司与上海华力微电子,15日共同宣布了华力微电子基于Cadence Encounter数字技术交付55纳米平台的参考设计流程。华力微电子首次在其已建立55纳米工艺上实现了从RTL到GDSII的完整流程。

2013-08-16 11:08:11 1383

1383

1383

1383华力微电子基于Cadence Encounter开发55纳米平台的参考设计流程

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)与上海华力微电子有限公司,今天共同宣布华力微电子基于Cadence ® Encounter® 数字技术交付出55纳米平台的参考设计流程。

2013-08-16 12:02:40 1445

1445

1445

1445中芯国际采用Cadence数字流程 提升40纳米芯片设计能力

中芯国际新款40纳米 Reference Flow5.1结合了最先进的Cadence CCOpt和GigaOpt工艺以及Tempus 时序签收解决方案, 新款RTL-to-GDSII数字流程支持Cadence的分层低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839

1839

1839中芯国际采用Cadence数字流程 新增高级功能,以节省面积、降低功耗和提高性能

® 数字工具流程,应用于其新款SMIC Reference Flow 5.1,一款为低功耗设计的完整的RTL-GDSII 数字流程。Cadence流程结合了先进功能,以帮助客户为40纳米芯片设计提高功率、性能和面积。

2013-09-05 16:50:41 748

748

748

748Cadence宣布推出基于台积电16纳米FinFET制程DDR4 PHY IP

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布,立即推出基于台积电16纳米FinFET制程的DDR4 PHY IP(知识产权)。

2014-05-21 09:44:54 1769

1769

1769

1769Cadence为台积电16纳米FinFET+制程推出IP组合

美国加州圣何塞(2014年9月26日)-全球知名的电子设计创新领导者Cadence设计系统公司(NASDAQ: CDNS)今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。

2014-10-08 19:19:22 919

919

919

919Cadence工具获台积电7纳米早期设计及10纳米芯片生产认证

2016年3月22日,中国上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10纳米 FinFET工艺的数字、定制/模拟和签核工具通过台积电(TSMC)V1.0设计参考手册(DRM)及SPICE认证。

2016-03-22 13:54:54 1026

1026

1026

1026联华电子认证Cadence Virtuoso LDE Analyzer适用于其28HPCU制程

, LDE) Analyzer 分析方案通过联华电子认证,支援其28纳米HPCU(High Performance Compact,高效能精简型)制程技术。

2016-04-15 10:09:07 1939

1939

1939

1939Cadence 与 SMIC 联合发布低功耗 28纳米数字设计参考流程

“我们与 Cadence 密切合作开发参考流程,帮助我们的客户加快其差异化的低功耗、高性能芯片的设计,”中芯国际设计服务中心资深副总裁汤天申博士表示,“Cadence创新的数字实现工具与中芯国际28纳米工艺的紧密结合,能够帮助设计团队将28纳米设计达到更低的功耗以及更快的量产化。”

2016-06-08 16:09:56 2242

2242

2242

2242Cadence 数字全流程解决方案通过三星5LPE工艺认证

采用极紫外(EUV)光刻技术的Cadence 数字全流程解决方案已通过Samsung Foundry 5nm早期低功耗版(5LPE)工艺认证。

2019-07-11 16:36:47 3436

3436

3436

3436Cadence PCB封装制作流程

区别于altium的一库走天下,cadence的PCB套件流程中,PCB封装的制作需要单独制作pad,然后绘制封装。这两步的工具分别为Padstack和PCB Editor

2019-11-02 09:32:55 9632

9632

9632

9632

Cadence推出革命性新产品Cerebrus:完全基于机器学习,提供一流生产力和结果质量,拓展数字设计领导地位

随着 Cerebrus 加入到Cadence广泛的数字产品系列中,Cadence现在可以提供业界最先进的基于机器学习的数字全流程,从综合到实现和签核。

2021-07-23 16:37:23 2028

2028

2028

2028Cadence宣布推出Cadence Safety Solution安全方案

Cadence Safety Solution 包括新的 Midas Safety Platform,为模拟和数字流程提供基于 FMEDA 功能安全设计和验证的统一方案 该安全流程方案为汽车、工业

2021-10-26 14:24:34 4050

4050

4050

4050Cadence® 数字全流程获(GF) 12LP/12LP+工艺平台认证

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence® 数字全流程获得了 GlobalFoundries (GF) 12LP/12LP+ 工艺平台认证,以推动移动和消费市场的航空航天、超大规模计算、人工智能、移动和消费电子应用的设计。

2022-05-24 16:33:23 1202

1202

1202

1202Cadence数字和定制 / 模拟设计流程获得N4P工艺认证

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其数字和定制 / 模拟设计流程已获得 TSMC N3E 和 N4P 工艺认证,支持最新的设计规则手册(DRM)。

2022-06-17 17:33:05 4800

4800

4800

4800Cadence数字和定制/模拟设计流程获得台积电最新N4P和N3E工艺认证

中国上海,2022 年 10 月 27 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence 数字和定制/模拟设计流程已获得台积电最新 N4P 和 N3E

2022-10-27 11:01:37 940

940

940

940Cadence定制设计迁移流程加快台积电N3E和N2工艺技术的采用速度

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的节点到节点设计迁移流程,能兼容所有的台积电先进节点

2023-05-06 15:02:15 801

801

801

801Cadence数字和定制/模拟设计流程获得TSMC最新N3E和N2工艺技术认证

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发

2023-05-09 10:09:23 708

708

708

708Cadence 数字和定制/模拟设计流程获得 Samsung Foundry SF2 和 SF3 工艺技术认证

已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ● Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322

322

322Cadence数字和定制/模拟流程通过Samsung Foundry的SF2、SF3工艺技术认证

已经过 SF2 和 SF3 流程认证 ● Cadence 数字全流程针对先进节点实现了最佳 PPA 结果 ●Cadence 定制/模拟工具,包括基于 AI 的 Virtuoso Studio,已针对

2023-07-05 10:12:14 381

381

381

381Cadence 推出经过认证的创新背面实现流程,以支持 Samsung Foundry SF2 技术

内容提要 ● 完整的背面布线解决方案,助力面向移动、汽车、人工智能和超大规模应用的下一代高性能芯片设计 ● Cadence SF2 数字全流程包括用于 nTSV 优化的先进技术 ● 背面实现流程

2023-07-10 10:45:04 272

272

272

272

Cadence 数字、定制/模拟设计流程通过认证,Design IP 现已支持 Intel 16 FinFET 制程

的 Cadence 流程,以十足把握交付各类 HPC 及消费电子应用 中国上海,2023 年 7 月 14 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布其数字和定制/模拟

2023-07-14 12:50:02 381

381

381

381

Cadence 与 Arm 合作,成功利用 Cadence AI 驱动流程加速 Neoverse V2 数据中心设计

内容提要 ● Cadence 优化了其 AI 驱动的 RTL-to-GDS 数字流程,并为 Arm Neoverse V2 平台提供了相应的 5nm 和 3nm 快速应用工具包(RAK),助力设计人

2023-09-05 12:10:01 3159

3159

3159

3159Cadence 数字和定制/模拟设计流程获 TSMC 最新 N2 工艺认证

内容提要 Cadence 数字全流程涵盖关键的新技术,包括一款高精度且支持大规模扩展的寄生参数 3D 场求解器 Cadence Cerebrus 由 AI 驱动,支持 N2 制程,可大幅提高客户

2023-10-10 16:05:04 270

270

270

270Imagination在OnCloud平台上使用AI驱动的Cadence Cerebrus优化PPA结果

“基于人工智能的cadence cerebrus和更广泛的cadence数字进程是为复杂的下一代设计而设计的,例如5纳米低功耗gpu的imagination。”

2023-10-20 10:04:07 261

261

261

261Cadence推出全新数字孪生平台Millennium Platform

楷登电子(Cadence Design Systems)今日宣布推出全新的Cadence® Millennium™ Enterprise Multiphysics Platform,这是一款面向

2024-02-03 11:31:11 553

553

553

553 电子发烧友App

电子发烧友App

评论