高通执行副总裁史蒂芬·莫林科夫(Steven Mollenkopf)终于证实,公司旗下首款采用28纳米制造工艺的产品将于今年年底到来!其实早前业内就已经有消息放出,暗示高通将于今年晚些时候才发

2011-07-23 09:14:13 3258

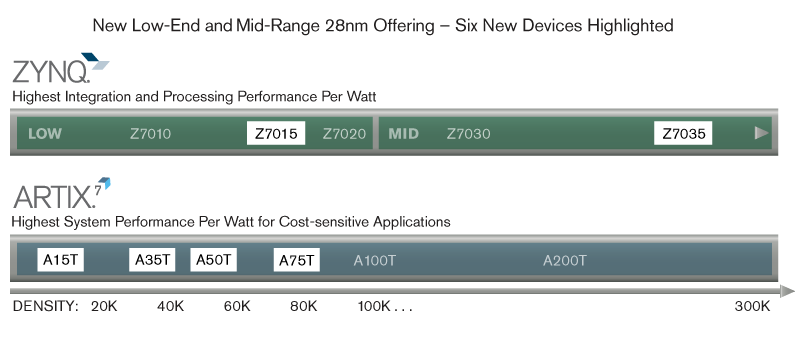

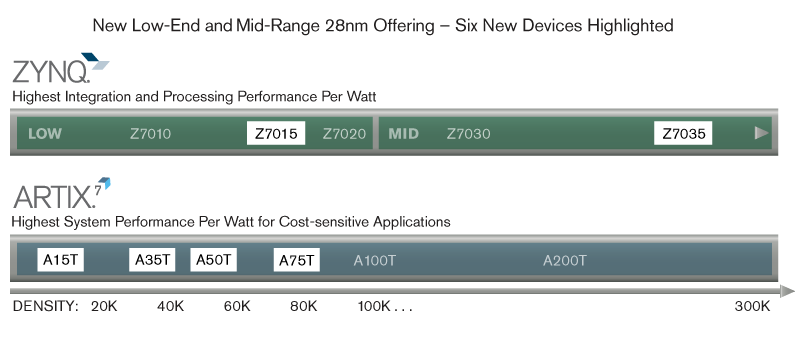

3258 赛灵思的20纳米产品以备受市场肯定的28纳米制程突破性技术为基础,提供超越一个技术世代的系统效能、功耗和可编程系统整合度,继续超越下一代!

2012-12-03 09:48:01 876

876 采用其28纳米工艺制程的 Qualcomm®骁龙™410处理器已成功应用于主流智能手机,这是28纳米核心芯片实现商业化应用的重要一步,开启了先进手机芯片制造落地中国的新纪元。

2015-08-11 07:54:46 2718

2718 就是关闭XT2晶振了,在低功耗的之前开启XT2作为时钟源,进入低功耗的时候关闭XT2,为什么这时候功耗依然很大呢,如果在时钟初始化的时候不操作BCSCTL1这个寄存器的话,进入低功耗后电流就非常小,我

2016-11-14 13:10:49

(Microcontroller Unit, MCU)市场,最新推出95纳米单绝缘栅非易失性嵌入式存储器(95纳米5V SG eNVM)工艺平台。在保证产品稳定性能的同时,95纳米5V SG eNVM工艺平台以其低功耗、低成本

2017-08-31 10:25:23

65纳米和45纳米。 65纳米IC设计规模极为庞大,复杂度高,大多采用层次化物理设计和低功耗设计流程,这使65纳米节点IC设计成本和设计团队规模随之增加。在典型情况下,设计成本是随着设计类型的不同而改变

2019-05-20 05:00:10

低功耗MCU,晶振1.晶振有无源晶振和有源晶振,2pin和4pin,2P的晶振在设计、贴片工艺上更方便些。4脚有源晶振比2脚无源晶振好在哪里?2.供电2.5-5.5V这也算是低功耗?我看国外的低功耗

2021-10-11 17:18:28

数据透传是选择低功耗WiFi模块还是低功耗蓝牙模块好?

2021-01-04 06:55:35

低功耗以太网PHY对于楼宇自动化的深远影响

2020-11-26 06:29:47

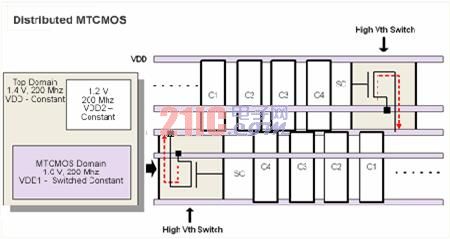

Altera公司产品和企业市场副总裁DannyBiran低功耗是一种战略优势 在器件的新应用上,FPGA功耗和成本结构的改进起到了非常重要的作用。Altera针对低功耗,同时对体系结构和生产工艺进行

2019-07-16 08:28:35

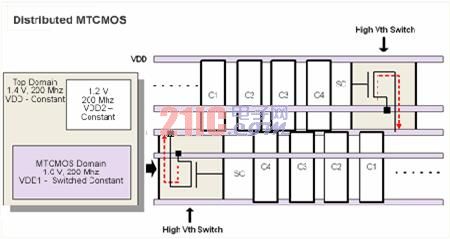

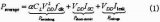

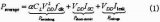

功耗存在。静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗。动态功耗:包括开关功耗或者成为翻转功耗、短路功耗或者称为内部功耗;动态功耗影响因素:门寄生电容、时钟翻转翻转、时钟频率、供电电压;降低功耗:应当在所有涉及层次上进行,即系统级、逻辑级和物理即,层次越高对功耗降低越有效;在系统

2021-11-11 06:24:53

。彩灯控制把低功耗蓝牙模块内置于LED内,即可通过APP控制灯泡的色彩、亮暗。在智能家居、连锁酒店、办公室、饭店等需要灯光控制调节的地方均可以内置低功耗蓝牙模块,改进设备的智能化和时尚化。计算机外设、I

2019-03-18 02:25:12

可选,并能够以低电流进行备用电池供电。此外,产品还应尽可能地提高响应速度,并具备更多的内部资源。 近日,微芯(Microchip)公司推出的具有多种灵活低功耗休眠模式且工作电流超低的PIC24F

2019-07-10 08:10:06

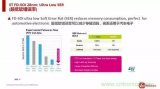

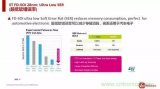

工艺节点中设计,但是 FD-SOI 技术提供最低的功率,同时可以承受辐射效应。与体 CMOS 工艺相比,28 纳米 FD-SOI 芯片的功耗将降低 70%。射频数据转换器需要同时具有高带宽和低功耗,以

2023-02-07 14:11:25

程序使用定时唤醒采样方式,每隔一段时间唤醒,进行AD采样。问题在于,如果不使用内部2.5V基准电压,进入低功耗时候,电流在20uA左右;使用内部2.5V基准电压,进入低功耗前关闭(ADC12CTL0

2018-06-21 14:54:10

DL-RX809L 基于SOC 的超外差无线接收芯片设计,是一款低功耗、低成本、小体积、带解码(学习码)超外差无线接收模块。内部集成高性价比无线数据接收芯片及性能优异的低功耗单片机,模块具有行业超高

2018-07-07 13:33:46

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。如何减小动态和静态功耗?如何使功耗最小化?

2019-08-27 07:28:24

消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。尽管基于90nm工艺的FPGA的功耗已低于先前的130nm产品,但它仍然是整个系统功耗的主要载体。此外,如今的终端产品设计大多

2019-07-15 08:16:56

PCB制造工艺流程是怎样的?

2021-11-04 06:44:39

你好微芯片的工作人员!我正在从以下链接阅读关于降低功耗的一些技巧的文档:http://ww1.micro..com/...01146B_.%202.pdfOn TIP#3 Configuring

2020-04-30 09:25:33

SimpleLink™超低功耗 无线微控制

2016-02-25 10:27:27

XLD3011系列是一套采用CMOS工艺实现的三端低功耗高压电路。它们可以输出100mA的电流,允许高达28V的输入电压。它们有3.0V到5.0V的几种固定输出电压。CMOS技术确保低电压降和低静太

2022-01-18 10:09:07

XLD3011系列是一套采用CMOS工艺实现的三端低功耗高压电路。它们可以输出100mA的电流,允许高达28V的输入电压。它们有3.0V到5.0V的几种固定输出电压。CMOS技术确保低电压降和低静态

2020-02-20 15:54:30

什么是纳米?为什么制程更小更节能?为何制程工艺的飞跃几乎都是每2年一次?

2021-02-01 07:54:00

现代化战争对吸波材料的吸波性能要求越来越高,一般传统的吸波材料很难满足需要。由于结构和组成的特殊性,使得纳米吸波涂料成为隐身技术的新亮点。纳米材料是指三维尺寸中至少有一维为纳米尺寸的材料,如薄膜

2019-08-02 07:51:17

低成本低功耗的同步解调器设计怎么简单化?

2021-05-20 06:36:50

HAL250低功耗霍尔开关是采⽤BCD工艺制作的全极低功耗霍尔ic,BCD⼯艺把双极⼯艺和CMOS工艺,DMOS工艺同时制作在同一芯⽚上。HAL250低功耗霍尔开关综合了双极器件高耐压、强负载的驱动

2021-10-14 11:45:24

关于黑孔化工艺流程和工艺说明,看完你就懂了

2021-04-23 06:42:18

在微功耗场景下,使用RCC是否比低功耗芯片的效率更高?设计例子:单火取电项目,从AC线取电取电,交流220V转直流12V,再通过DC-DC方案,将12V转为3.3V供Zigbee工作,该Zigbee

2016-06-17 13:50:42

的默认值,而且设计人员必须能够在流程中的任何阶段修改这些参数。为了解决这个问题,ReShape流程可以根据所用的工艺、特定的芯片类型及芯片内的特定模块类型提供层次化的配置文件来控制这些设置工作。这样就消除

2018-11-26 16:21:06

芯片设计解决方案供应公司微捷码(Magma)设计自动化有限公司近日宣布,已和专为消费性应用提供超低功耗65纳米FPGA(现场可编程门阵列)技术的先驱者SiliconBlue科技公司正式签定技术合作

2019-07-26 07:29:40

结合采用低功耗元件和低功耗设计技术在目前比以往任何时候都更有价值。随着元件集成更多功能,并越来越小型化,对低功耗的要求持续增长。当把可编程逻辑器件用于低功耗应用时,限制设计的低功耗非常重要。本文将讨论减小动态和静态功耗的各种方法,并且给出一些例子说明如何使功耗最小化。

2019-07-12 06:38:08

给予过高的期望。当然,所选择的工艺不同,结果也会不同。双极性器件具有最终决定带宽 (BW=gm/2πCc) 的更高跨导 (gm)。要弄清楚多低才算低功耗,可以看一下流耗仅为 150nA 的最新 TLV3691。在 1V 以下的工作电压下,135nW 就是低功耗。

2018-09-13 14:25:14

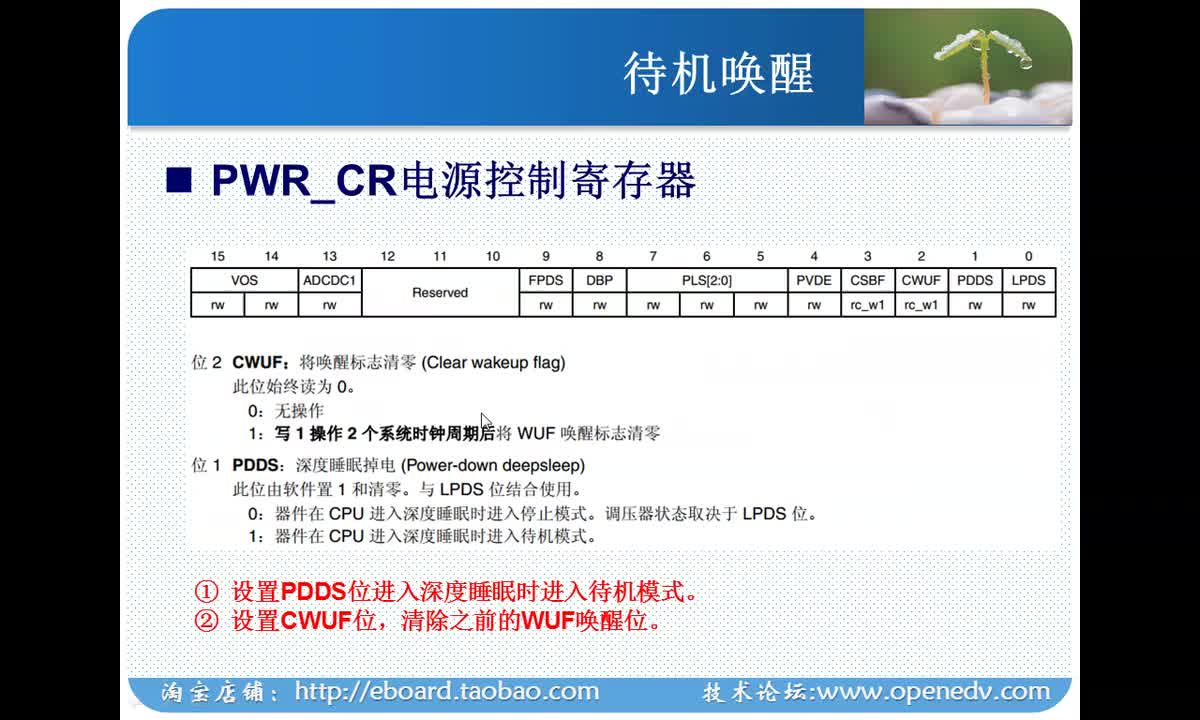

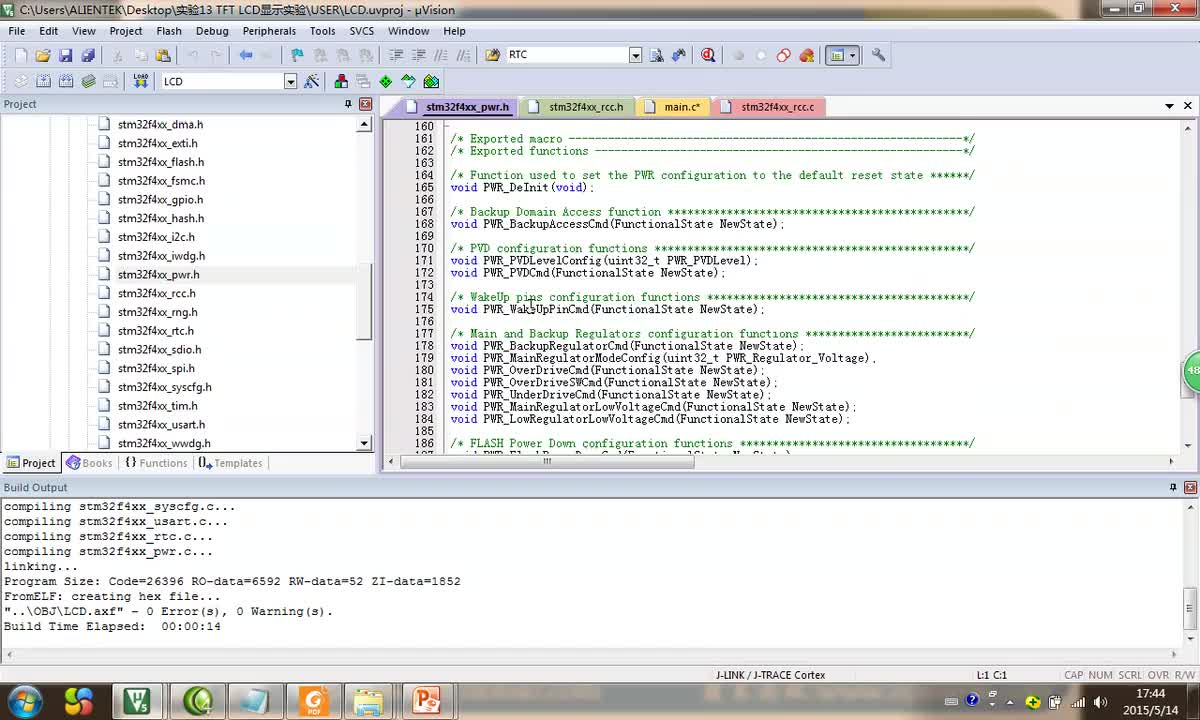

现在电子产品一般都有要求低功耗,不同的MCU,进入低功耗的处理流程可能不一样,但是大致的流程还是一样。现对MCU进入低功耗的处理流程大致如下:(1)关闭MCU之外的外设电源,例如:RS485、CAN

2021-11-01 08:10:03

从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。Altera在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

2019-09-17 08:18:19

量。通过采用基于40nm的半导体最新制造工艺以及创新方法来优化这些复杂的器件,设计人员能够在单芯片中集成更多的功能。这不但降低了总功耗,而且还可以降低后续工艺节点每一相应功能的功耗。TPACK便是能够

2019-07-31 07:13:26

一半,而性能提高两倍。通过选择一个高性能低功耗的工艺技术,一个覆盖所有产品系列的、统一的、可扩展的架构,以及创新的工具,赛灵思将最大限度地发挥 28 纳米技术的价值, 为客户提供具备 ASIC 级功能

2019-08-09 07:27:00

有这个功耗存在。静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗;动态功耗:包括开关功耗或者称为翻转功耗、短路功耗或者称为内部功耗。动态功耗影响因素:门寄生电容、时钟翻转率、时钟频率、供电电压;降低功耗:应当在所有设计层次上进行,即系统级、逻辑级和物理级,层次越高对功耗降低越

2021-11-11 06:27:30

的市场前景,众商家摩拳擦掌、跃跃欲试,试图在产品终端形态和穿戴方式,以及应用效能和实际用途方面推陈出新、抢滩市场,这也就对产品的内核模块设计提出了更高的要求——小尺寸、低功耗、高工艺、性能稳定、可操作性强

2017-12-12 15:29:01

分享一款巨微MS1581低功耗蓝牙无线收发器

2021-01-01 07:46:30

,Vdd为工作电压。 2 常用的低功耗设计技术 低功耗设计足一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统

2016-06-29 11:28:15

复制性决定了指纹锁是目前所有锁具中最为安全的锁种。指纹锁除指纹识别外,根据国家公安部规定,应当加配应急机械钥匙。 灵动微推出一款针对指纹锁应用的低功耗MCU,型号:MM32F031MM32F031

2018-09-06 15:32:41

晶体管管芯的工艺流程?光刻的工艺流程?pcb制版工艺流程?薄膜制备工艺流程?求大佬解答

2019-05-26 21:16:27

`DL-RX809L 基于SOC 的超外差无线接收芯片设计,是一款低功耗、低成本、小体积、带解码(学习码)超外差无线接收模块。内部集成高性价比无线数据接收芯片及性能优异的低功耗单片机,模块具有行业

2019-02-22 18:23:05

样板贴片的工艺流程是什么

2021-04-26 06:43:58

终端节点关闭低功耗模式和开启低功耗模式,功耗有何区别?功耗相差多少?

2018-05-22 08:42:02

芯片制造全工艺流程详情

2020-12-28 06:20:25

芯片生产工艺流程是怎样的?

2021-06-08 06:49:47

功耗及其组成部分,总结降低功耗的若干种常用方案;并重点介绍如何用UPF把低功耗意图描述出来以及如何用Synopsys工具实现整个流程。 目前常用的低功耗设计的一些方法特别是用power-gating

2020-07-07 11:40:06

直到器件/I艺级的整个数字系统设计流程。每个级别可以达到的低功耗设计效果不同,抽象层次越高则优化的空间越大,效果也越明显。对于电路的平均翻转率,通过软硬件分工有可能降低电路30%的翻转次数,而通过逻辑

2013-05-16 20:00:33

请详细叙述腐蚀工艺工段的工艺流程以及整个前道的工艺技术

2011-04-13 18:34:13

stm32进入低功耗模式,必须用中断来唤醒,现在就是不用这种模式,如何通过程序来降低功耗啊

2019-05-06 18:43:22

贴片电阻的生产工艺流程如何

2021-03-11 07:27:02

要。Altera Cyclone V FPGA通过多种方法帮助设计人员降低系统总成本,设计人员受益的不仅是TSMC的28nm低功耗(28LP)制造工艺,还包括Cyclone V器件系列内置的体系结构,以及

2015-02-09 15:02:06

本资料是关于如何采用低功耗28nm降低系统总成本

2012-07-31 21:25:06

中芯国际(SMIC)和Cadence 共同推出用于65纳米的低功耗解决方案Reference Flow 4.0

完全集成的能效型流程令快速、轻松地设计低功耗尖端器件成为可能

2009-10-31 07:48:01 1228

1228 高通携手TSMC,继续28纳米工艺上合作

高通公司(Qualcomm Incorporated)与其专业集成电路制造服务伙伴-TSMC前不久日共同宣布,双方正在28纳米工艺技术进行密切合作。此

2010-01-13 08:59:23 910

910 台积电与联电大客户赛灵思合作28纳米产品

外电引用分析师资讯指出,联电大客户赛灵思(Xilinx)3月可能宣布与台积电展开28纳米制程合作;台积电28纳米已确定取得富

2010-01-19 15:59:55 1058

1058 赛灵思宣布采用 28 纳米工艺加速平台开发

全球可编程逻辑解决方案领导厂商赛灵思公司 (Xilinx Inc. ) 今天宣布,为推进可编程势在必行之必然趋势,正对系统工

2010-02-23 11:16:21 382

382 统一工艺和架构,赛灵思28纳米FPGA成就高性能和低功耗的完美融合

赛灵思公司(Xilinx)近日宣布,为推进可编程势在必行之必然趋势,正对系统工程师在全球发布赛灵思

2010-03-02 08:48:51 576

576 根据贯穿整个IC实现流程的集成化低功耗设计技术策略

降低功耗是现代芯片设计最具挑战性需求之一。采用单点工具流程时,往往只有到了设计流程后期阶段才会去考虑降

2010-04-21 10:54:28 651

651

近期,高通公司宣布将推出首款基于28纳米工艺的Snapdragon芯片组MSM8960并宣布此芯片组将于2011财年开始出样。基于28纳米工艺的该芯片组采用新的CPU内核为特征,主要针对高端

2010-11-24 09:19:57 1471

1471 本文基于IEEEl801标准Uni-fied Power Format(UPF),采用Synopsys和Mentor Graphics的EDA工具实现了包括可测性设计在内的“从RTL到GDSII”的完整低功耗流程设计。本论文第1部分描述了低功耗技术和术语

2011-03-11 11:33:55 1621

1621

微捷码QCP提取器已被台积电(TSMC)纳入其季度28纳米集成电路(IC)EDA质量检验报告中。这次质量检验让设计师们对采用QCP解决台积电28纳米工艺IC日益提高的复杂性问题更有信心。

2011-07-15 08:39:06 877

877 本文采用自顶而目的设计原则,从体系结构到电路实现上分层次探讨了时钟芯片的功耗来源,并采取相应的控制手段实现芯片的低功耗设计。

2011-10-08 11:50:04 2128

2128

在高层次对系统进行功耗佑算和功耗优化是soc设计的关健技术本文首先给出soc设计的特点和流程,然后综述目前高层次功耗估算和功耗优化的常用方法和技术,重点论述寄存器传输级和

2011-12-27 16:42:38 46

46 本白皮书介绍了有关赛灵思 28 nm 7 系列 FPGA 功耗的几个方面,其中包括台积电 28nm高介电层金属闸 (HKMG) 高性能低功耗(28nm HPL 或 28 HPL)工艺的选择。 本白皮书还介绍了 28 HPL 工艺提供

2012-03-07 14:43:44 41

41 台积电TSMC已经准备量产28纳米工艺的ARM处理器了。TSMC在2011年第四季度开始从28纳米芯片获得营收,目前28纳米工艺芯片占有公司总营收的额5%。在今年晚些时候,TSMC将加速28纳米芯片的生

2012-04-18 10:22:37 830

830

日前,联华电子与SuVolta公司宣布联合开发28纳米工艺技术,该工艺将SuVolta的SuVolta的Deeply Depleted Channel晶体管技术集成到联华电子的28纳米High-K/Metal Gate高效能移动工艺。

2013-07-25 10:10:52 1049

1049 中芯国际新款40纳米 Reference Flow5.1结合了最先进的Cadence CCOpt和GigaOpt工艺以及Tempus 时序签收解决方案, 新款RTL-to-GDSII数字流程支持Cadence的分层低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 2016年2月5日,北京讯——ARM 宣布,从即日起全球晶圆专工领导者联华电子(UMC)的28纳米28HPCU工艺可采用ARM® Artisan® 物理IP平台和ARM POP™ IP。

2016-02-15 11:17:49 896

896 “我们与 Cadence 密切合作开发参考流程,帮助我们的客户加快其差异化的低功耗、高性能芯片的设计,”中芯国际设计服务中心资深副总裁汤天申博士表示,“Cadence创新的数字实现工具与中芯国际28纳米工艺的紧密结合,能够帮助设计团队将28纳米设计达到更低的功耗以及更快的量产化。”

2016-06-08 16:09:56 2242

2242 28纳米以后逻辑工艺开始分岔:立体工艺FinFET由于获得英特尔与台积电的主推成为主流,14/16纳米都已量产,10纳米工艺也有可能在2017年量产;体硅工艺停止在28纳米,想增加集成度而又对FinFET开发成本望而却步的半导体公司另辟蹊径。

2016-11-04 19:12:11 846

846

台积电业务开发副总经理金平中指出,台积电的超低功耗平台包括55纳米超低功耗技术、40纳米超低功耗技术、22纳米超低功耗/超低漏电技术等,都已经被各种穿戴式产品和物联网应用采用,同时,台积电也把超低功耗

2017-12-11 15:03:29 1409

1409 于联电55纳米超低功耗工艺(55ULP)的 PowerSlash 基础IP方案。智原 PowerSlash 与联电工艺技术相互结合设计,为超低功耗的无线应用需求技术进行优化,满足无线物联网产品的电池长期寿命需求。 智原科技营销暨投资副总于德洵表示:物联网应用建构过程中,效能往往受制于低功耗技术。

2018-03-05 15:08:00 5142

5142 位于厦门火炬高新区的联芯集成电路制造(厦门)有限公司日前传来喜讯,已于今年2月成功试产采用28纳米High-K/Metal Gate 工艺制程的客户产品,试产良率高达 98%。这是该公司28纳米

2018-03-31 15:28:50 11192

11192 赛灵思7系列FPGA产品通过采用新的工艺和新的架构方式,成功将产品的功耗显著降低。7系列FPGA产品的实测功耗与上一代产品相比,降低了约一半。采用台积电全新28HPL工艺,赛灵思7系列28nm FPGA产品同时实现了高性能和低功耗。

2018-06-05 13:45:00 4085

4085 Credo 在2016年展示了其独特的28纳米工艺节点下的混合讯号112G PAM4 SerDes技术来实现低功耗100G光模块,并且快速地跃进至16纳米工艺结点来提供创新且互补的112G连接

2018-10-30 11:11:12 5204

5204 近日,华虹集团旗下中国领先的12英寸晶圆代工企业上海华力与全球IC设计领导厂商---联发科技股份有限公司(以下简称“联发科技”)共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一---基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2018-12-12 15:15:01 2029

2029 12月11日,华虹集团旗下中国领先的12英寸晶圆代工企业上海华力与全球IC设计领导厂商---联发科技股份有限公司(以下简称“联发科技”)共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一---基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2018-12-14 15:47:30 3159

3159 华虹集团旗下中国领先的12英寸晶圆代工企业上海华力与全球IC设计领导厂商---联发科技股份有限公司(以下简称“联发科技”)共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一---基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2019-01-01 15:13:00 3780

3780 华虹集团旗下上海华力与联发科技股份有限公司共同宣布,在两家公司的互相信任及持续努力下,近日双方合作成果之一——基于上海华力28纳米低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

2019-01-07 14:15:45 3224

3224 低功耗设计是一个整体的概念,意思是它在每个设计层次上都可以进行功耗的优化——算法层次的优化、RTL级代码的优化、门级网表的优化、版图布局的优化等等。

2019-02-02 17:20:00 5693

5693 持续创新 28HPL 高性能低功耗工艺,成就跨越全新中低端器件,和 Artix-7 FPGA、Kintex-7 FPGA 及 Zynq-7000 SoC 产品系列的全新低功耗工业速度等级的器件敬请

2019-08-01 09:07:32 3066

3066

28纳米与40纳米为目前半导体市场上的主流工艺,无论是IP、光罩与晶圆等技术均趋于稳定成熟,成本大幅低于FinFET工艺。

2019-09-19 14:43:29 1446

1446 的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低。目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。在消费电子领域,OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。 尽管基于90nm工艺的FPGA的功耗已低

2020-10-28 15:02:13 2498

2498 级四个层次按照自顶向下的电路设计方法,在不同设计层次上对功耗进行优化时,改善的程度是不同的,设计层次越高,优化所能达到的效果越好。本论文对各个层次的低功耗设计技术进行了研究和分析,并将系统级总线编码技术作为

2021-04-13 16:49:37 19

19 现在电子产品一般都有要求低功耗,不同的MCU,进入低功耗的处理流程可能不一样,但是大致的流程还是一样。现对MCU进入低功耗的处理流程大致如下:(1)关闭MCU之外的外设电源,例如:RS485、CAN

2021-10-25 11:36:02 18

18 都导通时所引起的功耗。低功耗设计方法对于系统是在低功耗下提高性能,还是高性能下降低功耗,这对采样什么样的低功耗技术很关键。下图是基于低功耗反馈的前向设计法,如图,可以看出五个层次下对系统的功耗进行优化,自顶向下分别对应系统级、行为级、RTL级、逻辑级和物理级。下图说明了各层次的具体优化方法和优化效果,可以看到层次

2021-11-06 15:51:01 18

18 功耗存在。静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗。动态功耗:包括开关功耗或者成为翻转功耗、短路功耗或者称为内部功耗;动态功耗影响因素:门寄生电容、时钟翻转翻转、时钟频率、供电电压;降低功耗:应当在所有涉及层次上进行,即系统级、逻辑级和物理即,层次越高对功耗降低越有效;在系统

2021-11-06 17:21:01 14

14 低功耗一直是便携式电子设备的关键要求,但近年来,在人工智能、5G、大数据中心、汽车等应用快速发展的推动下,对低功耗的需求已经扩散到更多的终端产品中。

2023-02-14 09:10:59 778

778 无压烧结银工艺和有压烧结银工艺流程区别如何降低纳米烧结银的烧结温度、减少烧结裂纹、降低烧结空洞率、提高烧结体的致密性和热导率成为目前研究的重要内容。烧结银的烧结工艺流程就显得尤为重要

2022-04-08 10:11:34 778

778

电子发烧友App

电子发烧友App

评论